Изобретение относится к электросвязи и может использоваться в системах передачи или регистрации информации.

Цель изобретения - повышение информативности устройства.

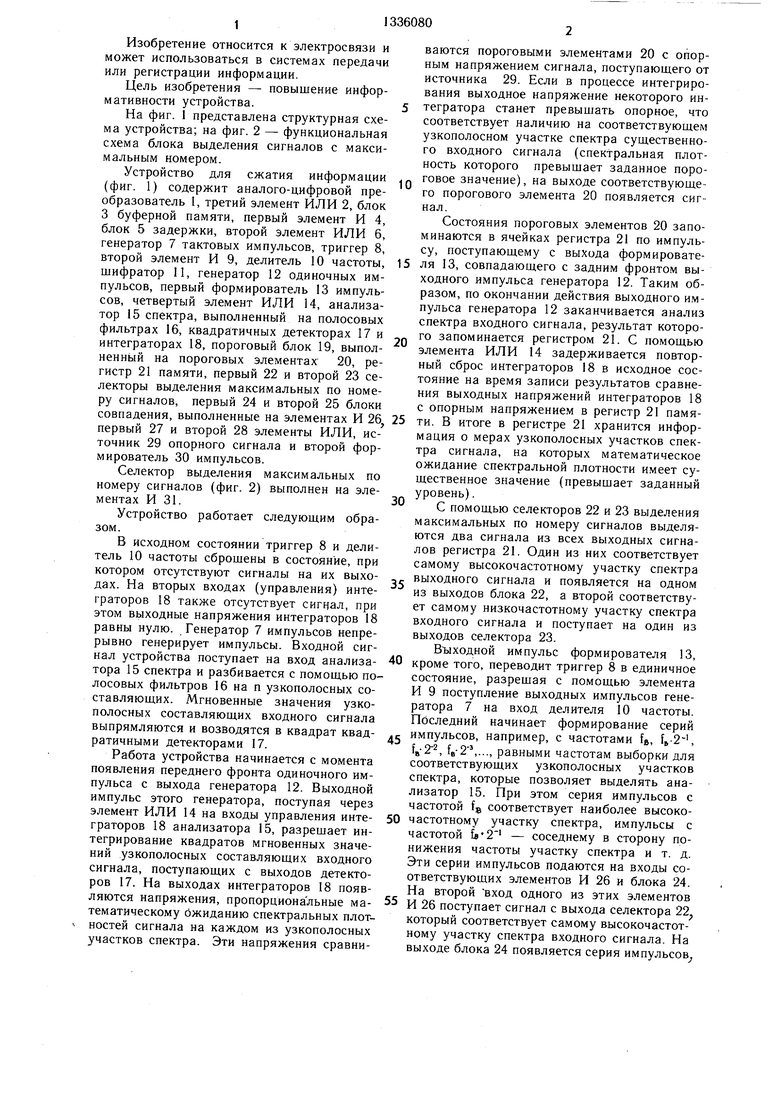

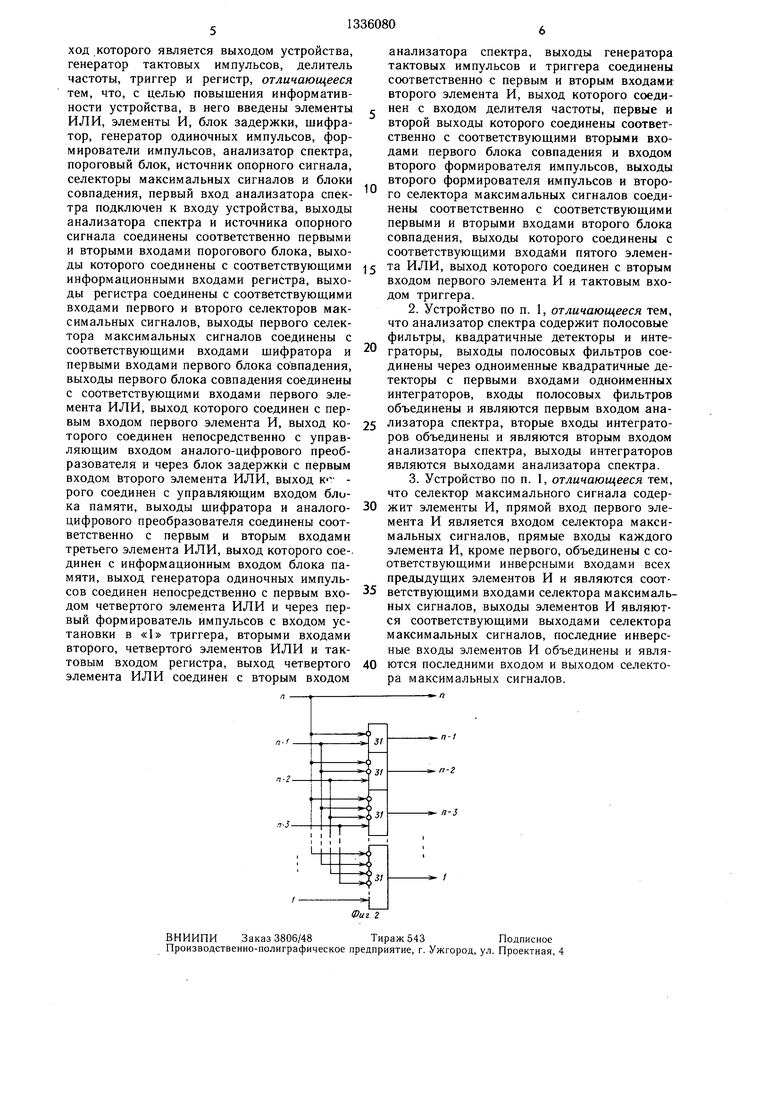

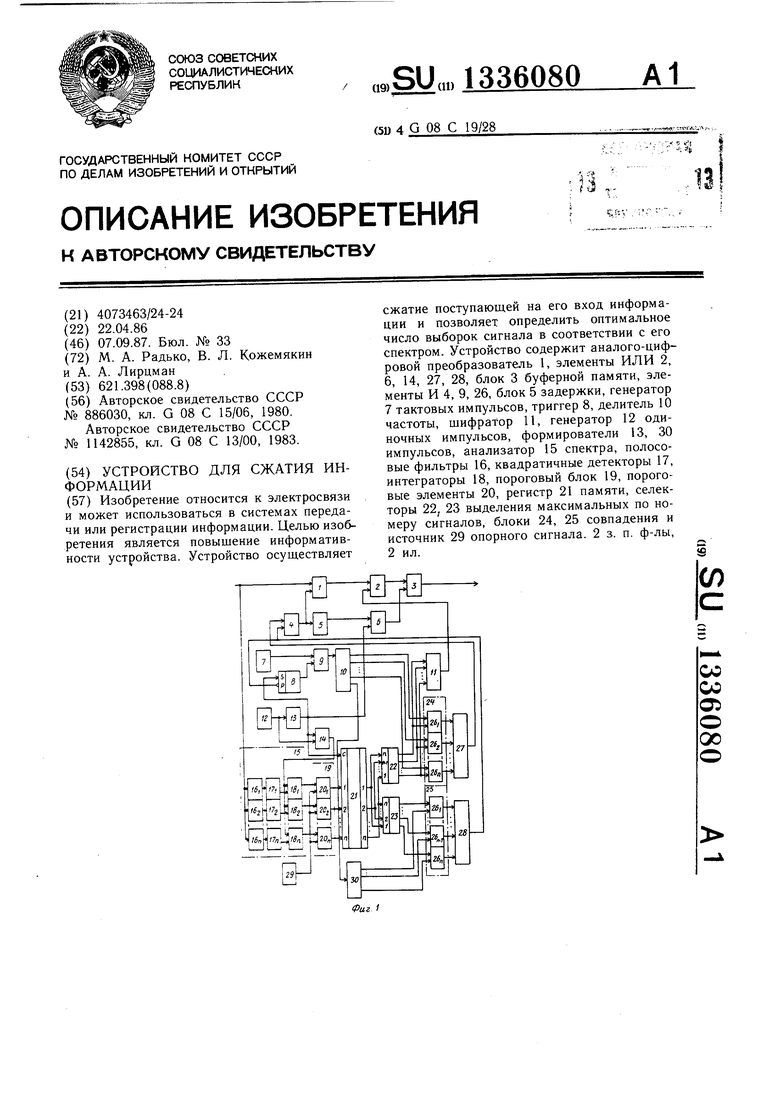

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема блока выделения сигналов с максимальным номером.

Устройство для сжатия информации (фиг. 1) содержит аналого-цифровой преобразователь 1, третий элемент ИЛИ 2, блок 3 буферной памяти, первый элемент И 4, блок 5 задержки, второй элемент ИЛИ б, генератор 7 тактовых импульсов, триггер 8, второй элемент И 9, делитель 10 частоты, шифратор 11, генератор 12 одиночных импульсов, первый формирователь 13 импульсов, четвертый элемент ИЛИ 14, анализатор 15 спектра, выполненный на полосовых фильтрах 16, квадратичных детекторах 17 и интеграторах 18, пороговый блок 19, выполненный на пороговых элементах 20, регистр 21 памяти, первый 22 и второй 23 селекторы выделения максимальных по номеру сигналов, первый 24 и второй 25 блоки совпадения, выполненные на элементах И 26, первый 27 и второй 28 элементы ИЛИ, источник 29 опорного сигнала и второй формирователь 30 импульсов.

Селектор выделения максимальных по номеру сигналов (фиг. 2) выполнен на элементах И 31.

Устройство работает следующим образом.

В исходном состоянии триггер 8 и делитель 10 частоты сброшены в состояние, при котором отсутствуют сигналы на их выходах. На вторых входах (управления) интеграторов 18 также отсутствует сигнал, при этом выходные напряжения интеграторов 18 равны нулю. Генератор 7 импульсов непрерывно генерирует импульсы. Входной сигнал устройства поступает на вход анализатора 15 спектра и разбивается с помощью полосовых фильтров 16 на п узкополосных составляющих. Мгновенные значения узкополосных составляющих входного сигнала выпрямляются и возводятся в квадрат квадратичными детекторами 17.

Работа устройства начинается с момента появления переднего фронта одиночного импульса с выхода генератора 12. Выходной импульс этого генератора, поступая через элемент ИЛИ 14 на входы управления интеграторов 18 анализатора 15, разрешает интегрирование квадратов мгновенных значений узкополосных составляющих входного сигнала, поступающих с выходов детекторов 17. На выходах интеграторов 18 появляются напряжения, пропорциональные математическому ожиданию спектральных плотностей сигнала на каждом из узкополосных участков спектра. Эти напряжения сравни0

5

0

5

0

5

0

5

0

5

ваются пороговыми элементами 20 с опорным напряжением сигнала, поступающего от источника 29. Если в процессе интегрирования выходное напряжение некоторого интегратора станет превыщать опорное, что соответствует наличию на соответствующем узкополосном участке спектра существенного входного сигнала (спектральная плотность которого превышает заданное пороговое значение), на выходе соответствующего порогового элемента 20 появляется сигнал.

Состояния пороговых элементов 20 запоминаются в ячейках регистра 21 по импульсу, поступающему с выхода формирователя 13, совпадающего с задним фронтом выходного импульса генератора 12. Таким образом, по окончании действия выходного и.м- пульса генератора 12 заканчивается анализ спектра входного сигнала, результат которого запоминается регистром 21. С помощью элемента ИЛИ 14 задерживается повторный сброс интеграторов 18 в исходное состояние на время записи результатов сравнения выходных напряжений интеграторов 18 с опорным напряжением в регистр 21 памяти. В итоге в регистре 21 хранится информация о мерах узкополосных участков спектра сигнала, на которых математическое ожидание спектральной плотности имеет существенное значение (превышает заданный уровень).

С помощью селекторов 22 и 23 выделения максимальных по номеру сигналов выделяются два сигнала из всех выходных сигналов регистра 21. Один из них соответствует самому высокочастотному участку спектра выходного сигнала и появляется на одном из выходов блока 22, а второй соответствует самому низкочастотному участку спектра входного сигнала и поступает на один из выходов селектора 23.

ВЪ1ход,ной импульс формирователя 13, кроме того, переводит триггер 8 в единичное состояние, разрещая с помощью элемента И 9 поступление выходных импульсов генератора 7 на вход делителя 10 частоты. Последний начинает формирование серий импульсов, например, с частотами fe, , в2 2, fe-2 ,..., равными частотам выборки для соответствующих узкополосных участков спектра, которые позволяет выделять анализатор 15. При этом серия импульсов с частотой f соответствует наиболее высокочастотному участку спектра, импульсы с частотой fe 2 - соседнему в сторону понижения частоты участку спектра и т. д. Эти серии импульсов подаются на входы соответствующих элементов И 26 и блока 24. На второй вход одного из этих элементов И 26 поступает сигнал с выхода селектора 22 который соответствует самому высокочастотному участку спектра входного сигнала. На выходе блока 24 появляется серия импульсов

частота импульсов в этой серии однозначно соответствует верхней граничной частоте спектра входного сигнала.

Эти импульсы подаются через элемент ИЛИ 27 и элемент И 4 на вход запуска аналого-цифрового преобразователя 1. С помощью аналого-цифрового преобразователя 1 начинается выборка входного сигнала, частота выборки определяется верхней граничной частотой в спектре входного сигнала. Частоты fe, fg S , ..., можно выбрать из условия, чтобы среднеквадратическая погрешность от сжатия информации не превышала допустимую.

Выходной сигнал селектора 22, кроме того, подается на вход шифратора 11, с выхода которого кодовая комбинация, соответствующая частоте выборки входного сигнала, поступает через элемент ИЛИ 2 на информационный вход блока 3 памяти. Одновременно на вход управления блока 3 подается импульс с выхода формирователя 13 через элемент 6 ИЛИ. В одну из ячеек памяти блока 3 записывается кодовая комбинация частоты выборки входного сигнала.

Импульсы с выхода элемента И 4, кроме того, подаются через блок 5 задержки и элемент ИЛИ 6 на вход управления записью блока 3 памяти, управляя записью информации, поступающей из аналого-цифрового преобразователя 1. Блок 5 задержки предназначен для сдвига во времени момента записи информации в блок 3 памяти относительно момента запуска аналого-цифрового преобразователя.

Импульсы с одного из выходов делителя 10 часто ы поступают на вход формирователя 30, который формирует импульсы с длительностями Т; Т 2 ; Т-2, ..., равными интервалами времени проведения выборок для каждого из узкополосных участков спектра, выделяемых анализатором 15. Эти импульсы поступают на первые входы соответствующих элементов И 26 блока 15. На второй вход одного из этих элементов И 26 подается сигнал с выхода селектора 23, который соответствует самому низкочастотному участку спектра входного сигнала. На выход блока 25 прн этом поступает только один импульс, длительность которого равна интервалу времени проведения выборок входного сигнала в соответствии с нижней граничной частотой в его спектре. Этот импульс подается через элемент ИЛИ 28 на второй вход элемента И 4 и ограничивает количество импульсов в серии, поступающей на управляющий вход аналого-цифрового преобразователя 1. Длительности импульсов Т, Т 2 , ... можно выбрать таким образом, что погрешность определения спектральных характеристик- входного сигнала не превышает допустимую, в том числе и для самой низкочастотной области спектра.

0

5

0

5

0

5

0

5

0

5

Импульс с выхода элемента ИЛИ 28, кроме того, поступает на вход сброса триггера 8, переводя его в исходное состояние по заднему фронту. Прекращается поступление импульсов на выходах делителя 10 частоты.

Таким образом, в ячейках блока 3 памяти накоплена информация о входном сигнале, причем частота выборок входного сигнала и длительность процесса проведения выборок соответствует верхней и нижней граничным частотам в спектре сигнала.

Селекторы 22 и 23 выделения сигналов с максимальным порядковым номером (фиг. 2) работают следующим образом.

Предположим, что на выход селектора поступает несколько сигналов, из которых, например, (п-2)-и сигнал имеет максимальный порядковый номер. Сигналы подаются на входы селектора таким образом, что их порядковые номера соответствуют порядковым номерам соответствующих входов.

Сигнал с максимальным порядковым номером поступает с (п-2)-го входа через соответствующий элемент И 31 на (п-2)-и выход, так как отсутствуют сигналы на инверсных входах этого элемента И 31 (эти входы подключены к входам селектора с более высокими порядковыми номерами). В то же время сигнал с (п-2)-го входа селектора подается на инверсные входы 1-го, 2-го, ..., (п-3)-го элементов И 31, запрещая поступление на соответствующие выходы селектора сигналов с его входов. Поэтому выходной сигнал селектора появляется только на одном из его выходов, порядковый номер которого соответствует максимальному из порядковых номеров, присутствующих на его входах сигналов.

Предлагаемое устройство позволяет по сравнению с известным уменьшить количество информации, требующейся для последующего восстановления квазистационарного сигнала, а также для получения характеристик такого сигнала, так как позволяет определять оптимальное число выборок сигнала в соответствии с его реальным спектром. Кроме того, оно позволяет предсказывать требуемый объем блока 3 памяти при регистрации квазистационарного сигнала, так как по определяемым частоте выборок и длительности интервала времени проведения выборок можно судить о количестве выборок еще до их проведения. Это особенно важно при многоканальной регистрации квазистационарных сигналов, когда объем блока 3 памяти ограничен, а общее количество регистрируемой информации сравнимо с объемом блока 3 памяти.

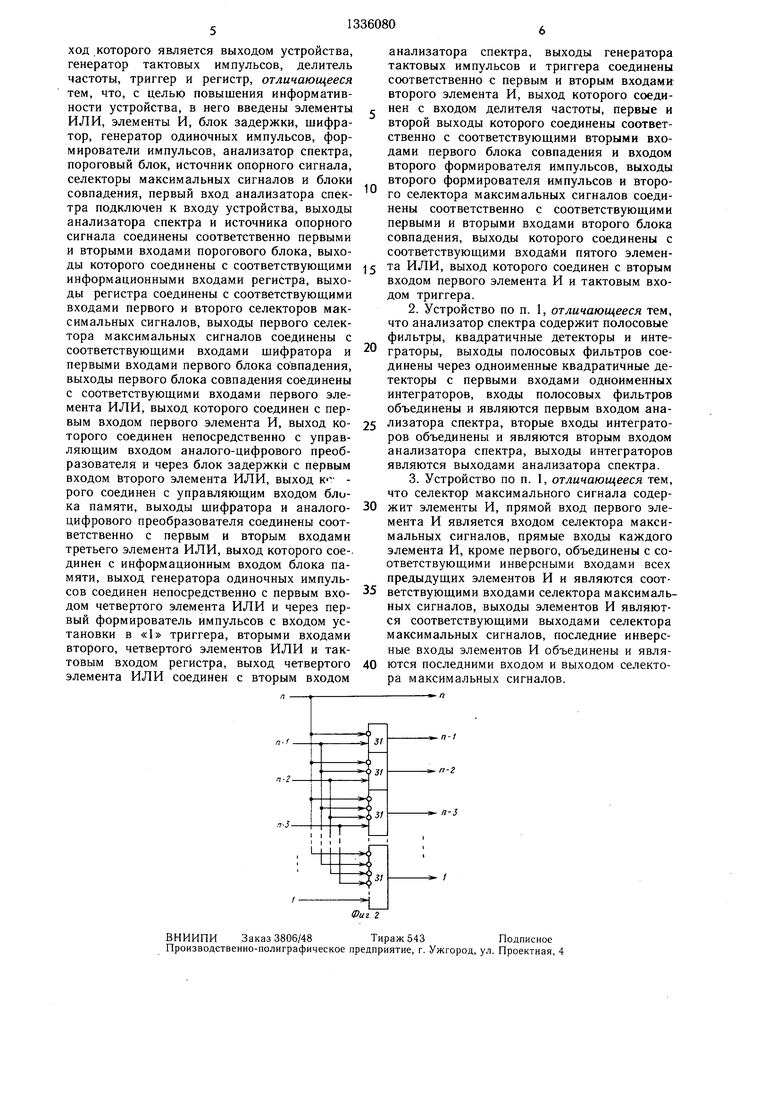

Формула изобретения 1. Устройство для сжатия информации, содержащее аналого-цифровой преобразователь, информационный вход которого является входом устройства, блок памяти, выход которого является выходом устройства, генератор тактовых импульсов, делитель частоты, триггер и регистр, отличающееся тем, что, с целью повышения информативности устройства, в него введены элементы ИЛИ, элементы И, блок задержки, шифратор, генератор одиночных импульсов, формирователи импульсов, анализатор спектра, пороговый блок, источник опорного сигнала, селекторы максимальных сигналов и блоки совпадения, первый вход анализатора спектра подключен к входу устройства, выходы анализатора спектра и источника опорного сигнала соединены соответственно первыми и вторыми входами порогового блока, выходы которого соединены с соответствуюш,ими информационными входами регистра, выходы регистра соединены с соответствуюшими входами первого и второго селекторов максимальных сигналов, выходы первого селектора максимальных сигналов соединены с соответствуюш.ими входами шифратора и первыми входами первого блока совпадения, выходы первого блока совпадения соединены с соответствуюп1,ими входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен непосредственно с управ- ляюш,им входом аналого-цифрового преобразователя и через блок задержки с первым входом бторого элемента ИЛИ, выход к- - рого соединен с управляющим входом блока памяти, выходы шифратора и аналого- цифрового преобразователя соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с информационным входом блока памяти, выход генератора одиночных импульсов соединен непосредственно с первым входом четвертого элемента ИЛИ и через первый формирователь импульсов с входом установки в «1 триггера, вторыми входами второго, четвертого элементов ИЛИ и тактовым входом регистра, выход четвертого элемента ИЛИ соединен с вторым входом

0

анализатора спектра, выходы генератора тактовых импульсов и триггера соединены соответственно с первым и вторым входами второго элемента И, выход которого соединен с входом делителя частоты, первые и второй выходы которого соединены соответственно с соответствуюшими вторыми входами первого блока совпадения и входом второго формирователя импульсов, выходы второго формирователя импульсов и второго селектора максимальных сигналов соединены соответственно с соответствующими первыми и вторыми входами второго блока совпадения, выходы которого соединены с соответствуюшими входами пятого элемен- 5 та ИЛИ, выход которого соединен с вторым входом первого элемента И и тактовым входом триггера.

2.Устройство по п. 1, отличающееся тем, что анализатор спектра содержит полосовые фильтры, квадратичные детекторы и инте0 граторы, выходы полосовых фильтров соединены через одноименные квадратичные детекторы с первыми входами одноименных интеграторов, входы полосовых фильтров объединены и являются первым входом анализатора спектра, вторые входы интеграторов объединены и являются вторым входом анализатора спектра, выходы интеграторов являются выходами анализатора спектра.

3.Устройство по п. 1, отличающееся тем, что селектор максимального сигнала содер0 жит элементы И, прямой вход первого элемента И является входом селектора максимальных сигналов, прямые входы каждого элемента И, кроме первого, объединены с соответствуюшими инверсными входами всех предыдущих элементов И и являются соответствующими входами селектора максимальных сигналов, выходы элементов И являются соответствующими выходами селектора максимальных сигналов, последние инверсные входы элементов И объединены и являются последними входом и выходом селектора максимальных сигналов.

5

5

0

n-t

п-г

Фиг г

ВНИИПИ Заказ 3806/48Тираж 543Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2080608C1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| МАЛОГАБАРИТНЫЙ РАДИОЛОКАТОР ТРАНСПОРТНОГО СРЕДСТВА | 1997 |

|

RU2117964C1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840444A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ | 2004 |

|

RU2259011C1 |

Изобретение относится к электросвязи и может использоваться в системах передачи или регистрации информации. Целью изобретения является повышение информативности устройства. Устройство осуществляет сжатие поступающей на его вход информации и позволяет определить оптимальное число выборок сигнала в соответствии с его спектром. Устройство содержит аналого-цифровой преобразователь 1, элементы ИЛИ 2, 6, 14, 27, 28, блок 3 буферной памяти, элементы И 4, 9, 26, блок 5 задержки, генератор 7 тактовых импульсов, триггер 8, делитель 10 частоты, шифратор 11, генератор 12 одиночных импульсов, формирователи 13, 30 импульсов, анализатор 15 спектра, полосовые фильтры 16, квадратичные детекторы 17, интеграторы 18, пороговый блок 19, пороговые элементы 20, регистр 21 памяти, селекторы 22, 23 выделения максимальных по номеру сигналов, блоки 24, 25 совпадения и источник 29 опорного сигнала. 2 з. п. ф-лы, 2 ил. (Л со 00 05 о 00

| Устройство для адаптивной временной дискретизации сигналов | 1980 |

|

SU886030A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для сжатия информации | 1983 |

|

SU1142855A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-22—Подача