1

Изобретение относится к связи и может быть использовано при построеини приемников телеграфной аппаратуры передачи данных.

Известны устройства для приема дискретной информации старт-стопным способом, содержащие на входе последовательно соединенные входной блок и блок выделения перепадов ампл итуды импульсов, а на выходе - последовательно соединенные распределитель, блок регистрацни, блок намяти, дешифратор и блок печати, а также генератор тактовых импульсов и делитель частоты, выход (к/4)-то разряда которого подключен ко входу циклового триггера, а выход к-го разряда - к продвигающему входу старт-стопного распределителя, выход которого, в свою очередь, подключен ко второму входу циклового триггера и к дополнительному входу блока памяти, кроме того, выход входного блока подключен к управляющему входу блока регистрации.

В известных устройствах искажения начала стартового импульса приводят к уменьщению рабочей исправляющей способности и поэтому они обладают низкой помехоустойчивостью.

С целью повыщения помехоустойчивости приема информации в предлагаемом устройстве выход блока перепадов амплитуды импульсов и парафазные выходы циклового триггера через две схемы «И подключены соответственно ко входам триггеров, ко вторым входам которых подключен выход старт-стопного распределителя, а выходы триггеров подключены к продвигающему входу делителя частоты через две вспомогательные схемы «И и схему «ИЛИ, причем ко вторым входам вспомогательных схем «И подключен генератор тактовых импульсов непосредственно и через дополнительный делитель частоты соответственно, кроме того, вход одното из триггеров соединен со в.ходом запуска делителя частоты, выход (к/4)-го разряда которого дополнительно (подключен IKO входу зануска старт-стопного распределителя, а между и входом (к/2)-го разряда делителя частоты включена дополнительная схема «И, ко второму входу которой подключен соответствующий парафазный выход циклового триггера.

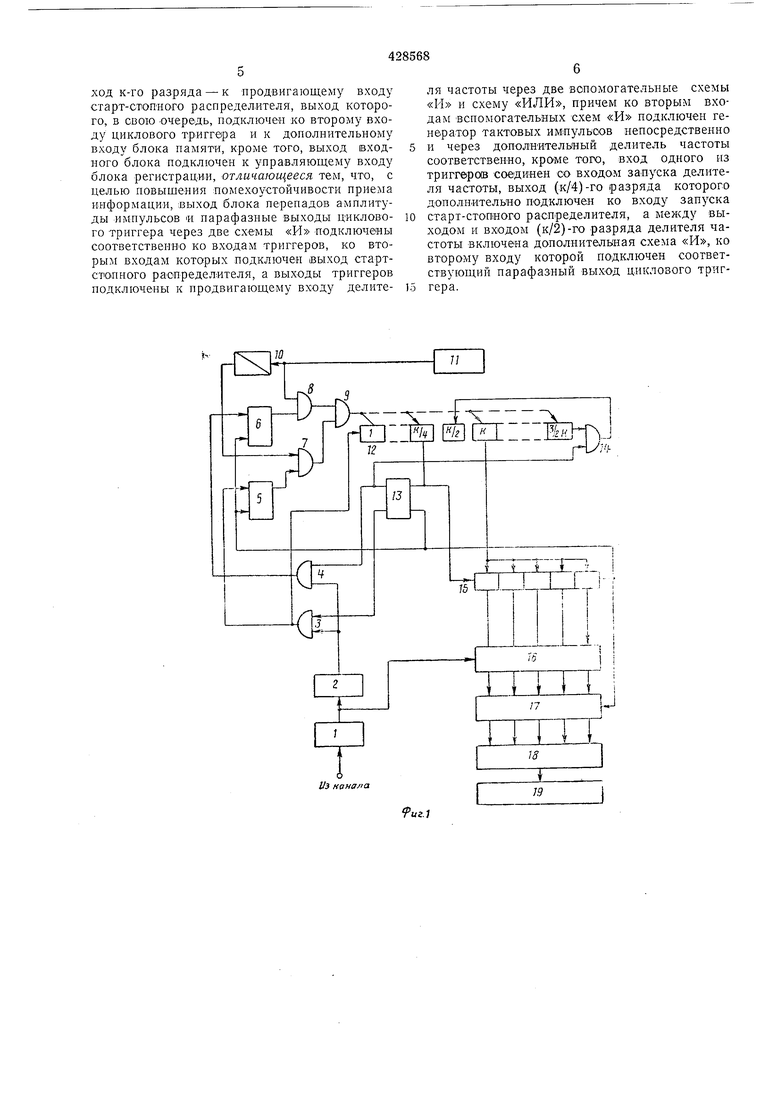

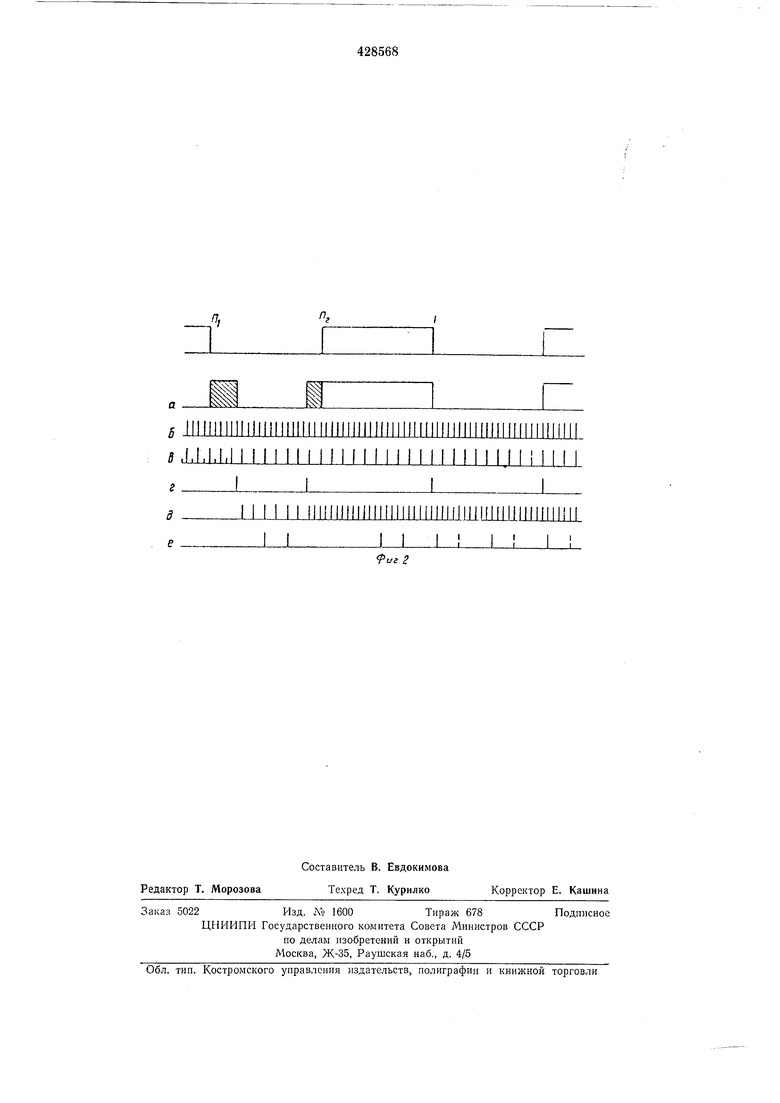

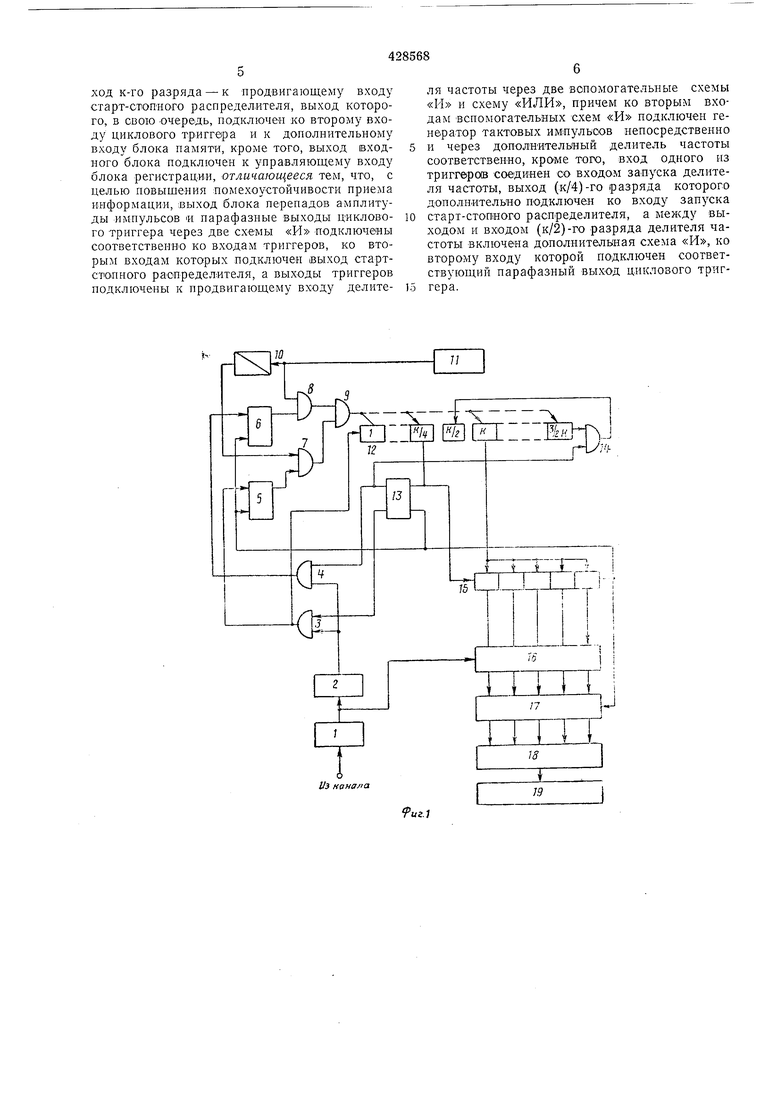

Иа фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содерл ит входной блок 1, блок 2 выделения перепадов амнлитуды импульсов, схемы «И 3 и 4, триггеры 5 и 6, схемы «И 7 н 8, схему «ИЛИ 9, делитель частоты 10, генератор // тактовых импульсов, делитель частоты 12, цикловой триггер 13, схему «И 14, старт-стопный распределитель 15, блок 16 регистрации, блок 17 памяти, дешифратор 18 и блок 19 печати. Канал связи подключен ко входному блоку /, выход которого подключен к блоку 16 регистрации п к блоку 2 выделения перепадов, выход которого через схемы «II 3 « 4 подключен ко входам триггеров 5 и 6 соотвегственно, кроме того, выход схемы «И 3 подан на вход запуска делнтеля частоты 12. Выходы триггеров 6 н 5 подключены .ко входам схемы «И 8 п 7 соответственно. Ко второму входу схемы «И 5 подключен выход генератора II тактовых импульсов, который также подключен через делитель частоты W ковторОМу входу схемы «И 7. Выходы схемы «И 7 и 8 через схему «ИЛИ 9 поданы на продвигаюпдкн вход делителя частоты 72. Выход (к/4)-го разряда делителя частоты 12 подан ща один из входов циклового триггера 13 и «а вход за-пуска старт-стопного распределителя 15. Выход к-го разряда делителя частоты 12 подан на продвигающие входы старт-iCTonHoro распределителя 15. Выход носледнего разряда делителя частоты 12 иодаи на .вход схемы «И 14, на второй вход которой подан выход циклового триггера 13, а выход схемы «И 14 соединен со входом (к/2)-го разряда делителя частоты 12. Выходы циклового триггера 13 поданы на вторые входы схем «И . Выходы старт-стопного распределителя /5 поданы на блок регистрации 16, -а выходы последеего разряда старт-стопиого распределителя 15 поданы на входы триггеров б, 6, 13 и на вход блока памяти 17. Выходы блока 16 регистрации через блок 17 памяри поданы та входы деш.ифр.атора 18, выход которого подключен к блоку 19 печати. Устройство работает следующим образом. При по.ступлении из канала сигналов очередной комбинации первыми поступают два перепада импульсов тока, определяющие .начало кодовой комбинации. После усиления и ограничения входным блоком / (фиг. 2, с) выделяется нервый перепад, сигнал о котором пз блока 2 выделения перепадов (фиг. 2, г) через схему «И 3 поступает -на вход Запуска делителя частоты 12 и сбрасывает все его разряды в состояние «О, а первый - в состояние «1. Кроме того, этот сигнал опрокидывает триггер 5 в состояние «1 и тем самы.м обеспечивает поступление через схемы «И 7 и «ИЛИ 9 продвигающих импульсов от делителя частоты 10 на делитель частоты 12. Под воздействием этих импульсов «единица про.двигается по делителю частоты 12 с частотой K/2.V (фиг. 2, 0). Если «единица доходит до (к/4)-го разряда, то сигнал с его выхода запускает старт-стопный распределитель 15 и опрокидывает цикловой триггер 13 в состояние «1, тем самым снимается сипнал со входа «И 3 и нодается сигнал на вход «И 4. Поэтому с приходом второго перепада сигнал с выхода блока 2 .выделения .перепада через схему «И 4 опрокидывает триггер 6 в состояние «1 и тем самым обеспечивает подачу сигнала па второй вход «И 8. С этого момента через схемы «И 8, «ИЛИ 9 на продвигающий вход поступают импульсы от задаюп1его генератора с частотой KN (фиг. 2, б). Если второй перепад придет раньше, чем цикловой триггер 13 опрокинется в состояние «1, то происходит дробление, и сигнал о втором перепаде приводит дел 1тель частоты 12 в исходное состояние. Сигналы с выхода к-го разряда определяют предполагаемые середины принимаел1ых импульсов и продвигают единицу в старт-стопном распределителе 15 из разряда в разряд, а его выходные сигналы определяют моменты начала ан-ализа поступающих с канала спгпалов блоком 16 регистраци.и для определения значения символа. Поскольку цикловой триггер 13 открывает схему «И 14, то при появлении сигнала .на выходе делителя частоты 12 он записьквает единицу (к/2)-и разряд, т. е. цикл этого регистра уменьщается на 1/2 к и будет равен к-тактам или o -r,- Сигналы с выхода последнего разряда определяют полагаемые гр-аницы импульсов. Отклонения сигналов, определяющих п.редполагаемые границы (середины) импульсов при таком построении делителя частоты 12 меньще искажений стартового сигнала. З.начения каждого символа поступают из блока 16 регистрации на блок 17 памяти, а з конце цикла по окончании регистрации пятого импульса поступает сигнал сброса, по которому накопленные символы .принятой комбинации сбрасываются на дешифратор ., который дешифрирует принятый знак и подает сигиал для отпечатывания его на блок 19 печати. Кроме тою, сипнал сброса с пятого выхода старт-стопного распределителя 15 приводит все элементы схемы в лс.одное состояние: триггеры 5, 6 и 13-в положение «О (.высокое напряжение на инвер.сном выходе) п все разряды делителя частоты 12-в состояние «О, после чего прнем.ное устр.ойство снова готово к приему очередного знака. Предлагаемое старт-стопное устройство обеспечивает запуск пр.иемно1го устройства по двум перепадам, соответствующим стартовому сигналу. При этом значительно уменьшается влияние искаженигс стартового сигнала на смещение моментов регистрации из-за этих искажений и у.меньшается вероятность .незапуска приемного устройства по сравнению с известным способом запуска по одному стартовому перепаду. Предмет изобретения Устройство для пр.иема дискретной и.кформации старт-стопным способом, содержащее на входе последовательно соединенные входной блоки блок выделения перепадов ампл.итуды импульсов, а на выходе - последовательно соединенные распределитель, блок регистрации, блок памяти, дешифратор и блок печати, а также генератор тактовых импульсов и делитель частоты, выход (к/4)-го разряда .которого подключен ко входу циклового триггера, а выход к-го разряда - к продвигающему входу старт-стопного распределителя, выход кото рого, в свою очередь, подключен ко второму входу циклового триггера и к дополнительному входу блока памяти, кроме того, выход входного блока подключен к управляющему входу блока регистрации, отличающееся тем, что, с целью повышения помехоустойчивости приема информации, :выход блока перепадов амплитуды импульсов и парафазные выходы циклового триггера через две схемы «И подключены соответственно ко входам триггеров, ко вторым входам которых иодключен выход стартсгоппого распределителя, а выходы триггеров подключены к продвигающему входу делителя частоты через две вопомогательные схемы «И и схему «ИЛИ, причем ко вторым входам вспомогательных схем «И подключен генератор тактовых импульсов непосредственно и через дополнительный делнтель частоты соответственно, кроме того, вход одного из триггеров соединен со входом запуска делителя частоты, выход (к/4)-го разряда которого дополнительно подключен ко входу запуска старт-стопного распределителя, а между выходом и входом (к/2)-го разряда делителя частоты включена дополнительная схема «И, ко второму входу которой подключен соответствующий парафазный выход циклового триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU319100A1 |

| Устройство для фазирования электронного стартстопного телеграфного приемника | 1987 |

|

SU1518904A1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| Приемное стартстопное устройство | 1985 |

|

SU1325721A1 |

| Устройство для фазирования электронного телеграфного приемника | 1983 |

|

SU1124437A1 |

| ПРИЕМНОЕ СТАРТСТОПНОЕ УСТРОЙСТВО | 1973 |

|

SU385401A1 |

| Устройство для регистрации потоков подвижных объектов | 1984 |

|

SU1193704A1 |

| Двухкратная стартстопно-синхронная система передачи дискретной информации | 1988 |

|

SU1570018A1 |

| Стартстопное приемное устройство | 1979 |

|

SU843283A2 |

| Стартстопное приемное устройство | 1985 |

|

SU1259506A1 |

Из наняла

19

Д.1.1.1.1.И I II II И Ml I И I I ИИ И I IJ I I I I I I

гL.JIL

дИ II I I Н1 1111 111 11111111ПП1111111111111111П111 11

Даты

1974-05-15—Публикация

1972-01-25—Подача