1

Изобретение относится к вычислительной технике и может быть использовано в качестве автоматического построителя графиков в регистрирующих устройствах с линейным органом записи, основанных, например, на электростатическом, электрохимическом, феррографическом и других способах регистрации.

В известных устройствах вычерчивание графиков происходит построчно с параллельным формированием всей строки.

Известное устройство для записи информации содержит усилители записи, подключенные к регистрирующим элементам и выходам схем «И, коммутатор, входы которого соединены с одним из запоминающих регистров и счетчиком, которые подключены к другому запоминающему регистру, дешифратор, подключенный к триггеру, двоичные дешифраторы, входы которых соединены с коммутатором, а выходы подключены к одним из входов первой и второй групп схем «ИЛИ, другие входы которых соединены с выходами схем «ИЛИ предыдущего разряда той же группы, выходы схем «ИЛИ первой группы подключены к одним из входов схем «И, а выходы схем «ИЛИ второй группы через инверторы - к другим входам схем «И.

Однако при помощи таких устройств линии наносятся только одной толщиной, равной размеру или разрешающей способности регистрирующего элемента, а для получения линий разной толщины необходимо повторять цикл записи, причем количество циклов записи равно толщине линии в битах и с ростом толщины линии снижается быстродействие устройства.

Цель изобретения - нанесение линий различной толщины за один цикл записи, что расширяет область применения устройства

практически без снижения быстродействия.

Для этого предлагаемое устройство содержит счетчик толщины линии, входы которого подключены к ключам четвертой группы, а выходы - к третьему входу схемы «ИЛИ, и

входной и выходной коммутаторы, причем входной коммутатор подключен к выходам запоминающих регистров всех групп, промежуточному коммутатору и одним из входов выходного коммутатора, другие входы которого подключены к выходам схем «ИЛИ первой группы и выходам инверторов, а выходы его - к входам схем «И.

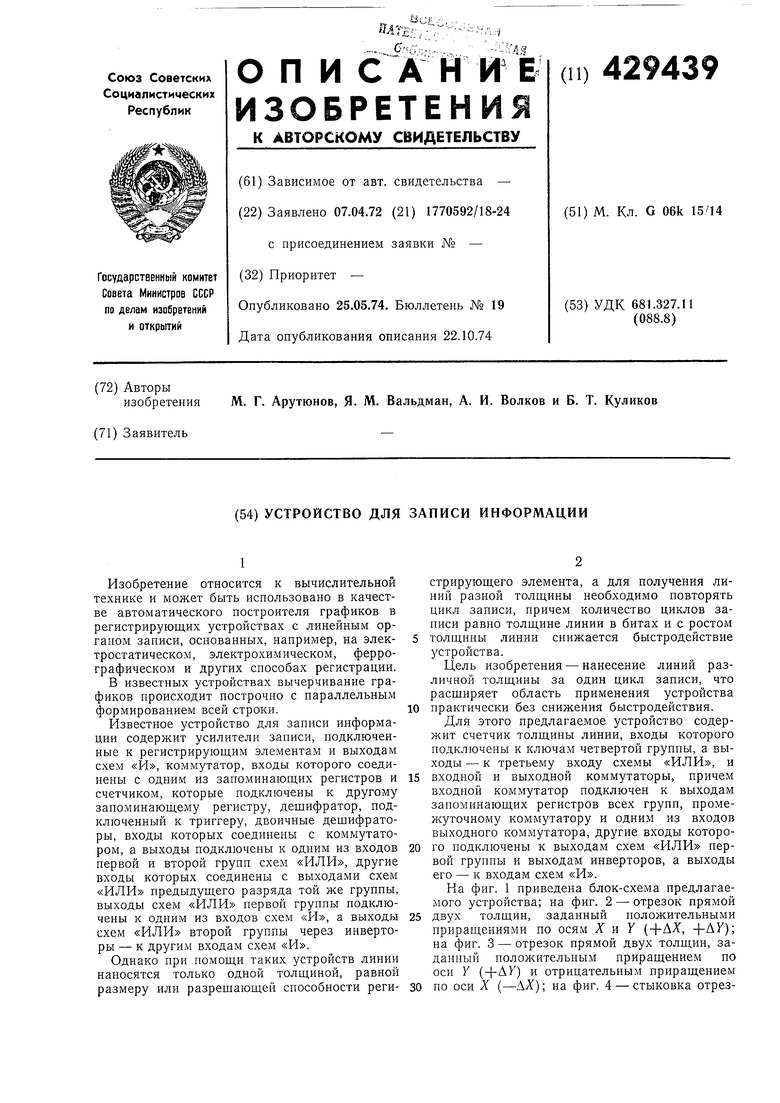

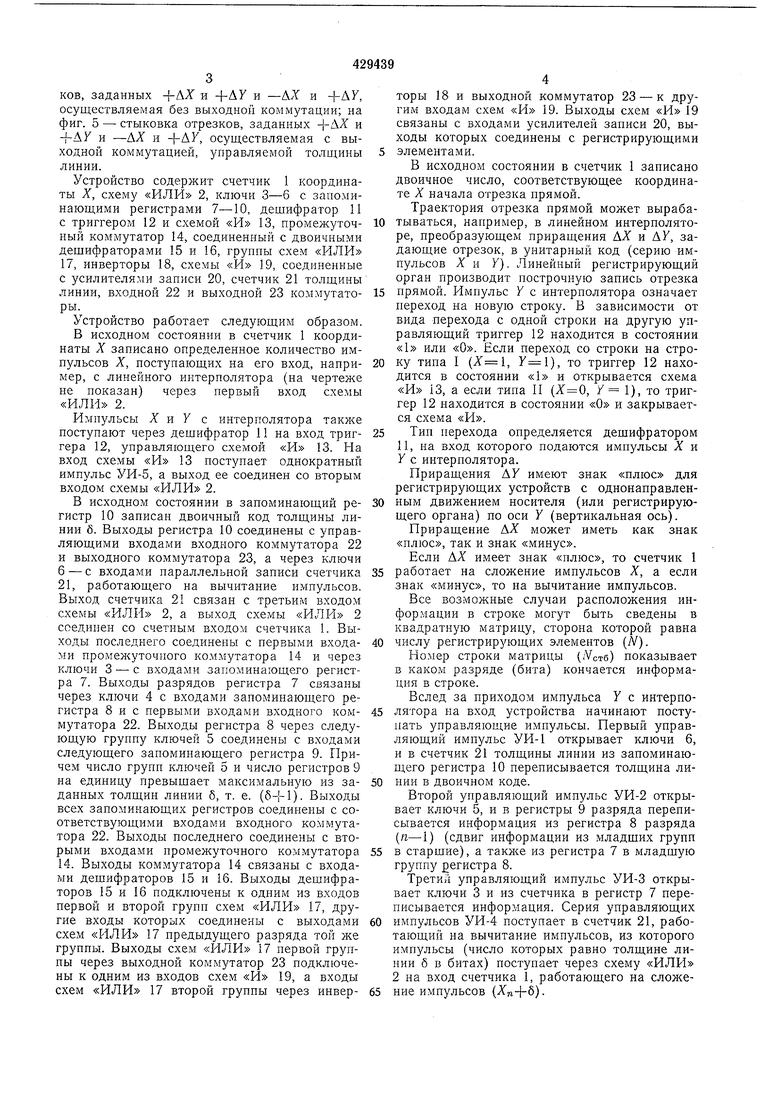

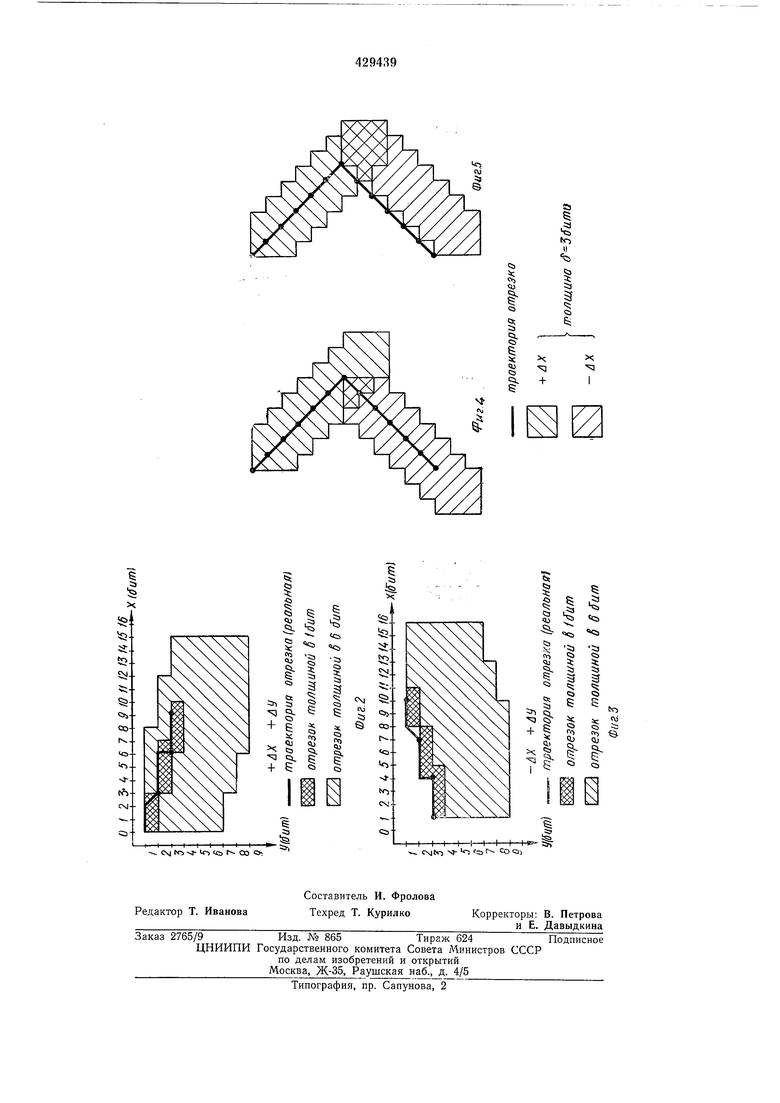

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - отрезок прямой

двух толщин, заданный положительными приращениями по осям J и У (+АХ, +А5); на фиг. 3 - отрезок прямой двух толщин, заданный положительным приращением по оси У (4-АУ) и отрицательным приращением

по оси X (-ДХ); на фиг. 4 - стыковка отрезков, заданных +Л и +Д и -&Х и Ч-АУ, осуществляемая без выходной коммутации; на фиг. 5 - стыковка отрезков, заданных +ДА и +ДУ и -Д и +А. осуществляемая с выходной коммутацией, управляемой толщины линии.

Устройство содержит счетчик 1 координаты X, схему «ИЛИ 2, ключи 3-6 с запоминающими регистрами 7-10, дещифратор 11 с триггером 12 и схемой «И 13, промежуточный коммутатор 14, соединенный с двоичными дешифраторами 15 и 16, группы схем «ИЛИ 17, инверторы 18, схемы «И 19, соединенные с усилителями записи 20, счетчик 21 толщины линии, входной 22 и выходной 23 коммутаторы.

Устройство работает следующим образом.

В исходном состоянии в счетчик 1 координаты /Y записано определенное количество импульсов X, поступающих на его вход, например, с линейного интерполятора (на чертеже пе показан) через первый вход схемы «ИЛИ 2.

Импульсы и у с интерполятора также поступают через дешифратор 11 на вход триггера 12, управляющего схемой «И 13. На вход схемы «И 13 поступает однократный импульс УИ-5, а выход ее соединен со вторым входом схемы «ИЛИ 2.

В исходном состоянии в запоминающий регистр 10 занисан двоичный код толщины линии б. Выходы регистра 10 соединены с управляющими входами входного коммутатора 22 и выходного коммутатора 23, а через ключи 6 - с входами параллельной записи счетчика 21, работающего на вычитание импульсов. Выход счетчика 21 связан с третьим входом схемы «ИЛИ 2, а выход схемы «ИЛИ 2 соединен со счетным входом счетчика 1. Выходы последнего соединены с первыми входами промежуточного коммутатора 14 и через ключи 3 - с входами запоминающего регистра 7. Выходы разрядов регистра 7 связаны через ключи 4 с входами запоминающего регистра 8 и с первыми входами входного коммутатора 22. Выходы регистра 8 через следующую группу ключей 5 соединены с входами следующего запоминающего регистра 9. Причем число групп ключей 5 и число регистров 9 на единицу превышает максимальную из заданных толщин линии б, т. е. (б-|-1). Выходы всех запоминающих регистров соединены с соответствующими входами входного коммутатора 22. Выходы последнего соединены с вторыми входами промежуточного коммутатора 14. Выходы коммутатора 14 связаны с входами дешифраторов 15 и 16. Выходы дешифраторов 15 и 16 подключены к одним из входов первой и второй групп схем «ИЛИ 17, другие входы которых соединены с выходами схем «ИЛИ 17 предыдущего разряда той же группы. Выходы схем «ИЛИ 17 первой группы через выходной коммутатор 23 подключены к одним из входов схем «И 19, а входы схем «ИЛИ 17 второй группы через инверторы 18 и выходной коммутатор 23 - к другим входам схем «И 19. Выходы схем «И 19 связаны с входами усилителей записи 20, выходы которых соединены с регистрирующими элементами.

В исходном состоянии в счетчик 1 записано двоичное число, соответствующее координате X начала отрезка прямой.

Траектория отрезка прямой может вырабатываться, например, в линейном интерполяторе, преобразующем приращения ДХ и ДК, задающие отрезок, в унитарный код (серию импульсов X и Y). Линейный регистрирующий орган производит построчную запись отрезка прямой. Импульс Y с интерполятора означает переход на новую строку. В зависимости от вида перехода с одной строки на другую управляющий триггер 12 находится в состоянии «1 или «О. Если переход со строки на строку типа I , ), то триггер 12 находится в состоянии «1 и открывается схема «И 13, а если типа II (0, / 1), то триггер 12 находится в состоянии «О и закрывается схема «И.

Тип перехода определяется дешифратором 11, на вход которого подаются импульсы X и Y с интерполятора.

Приращения ДУ имеют знак «плюс для регистрирующих устройств с однонаправленным движением носителя (или регистрирующего органа) по оси У (вертикальная ось).

Приращение ДХ может иметь как знак «плюс, так и знак «минус.

Если ДХ имеет знак «плюс, то счетчик 1 работает на сложение импульсов X, а если знак «минус, то на вычитание импульсов.

Все возможные случаи расположения информации в строке могут быть сведены в квадратную матрицу, сторона которой равна числу регистрирующих элементов (N).

Номер строки матрицы (;Устб) показывает в каком разряде (бита) кончается информация в строке.

Вслед за приходом импульса У с интерполятора па вход устройства начинают поступать управляющие импульсы. Первый управляющий импульс УИ-1 открывает ключи 6, и в счетчик 21 толщины линии из запоминающего регистра 10 переписывается толщина линии в двоичном коде.

Второй управляющий импульс УИ-2 открывает ключи 5, и в регистры 9 разряда переписывается информация из регистра 8 разряда (п-1) (сдвиг информации из младших групп в старшие), а также из регистра 7 в младшую группу дегистра 8.

Третий управляющий импульс УИ-3 открывает ключи 3 и из счетчика в регистр 7 переписывается информация. Серия управляющих импульсов УИ-4 поступает в счетчик 21, работающий на вычитание импульсов, из которого импульсы (число которых равно толщине линии б в битах) поступает через схему «ИЛИ 2 на вход счетчика 1, работающего на слол ение импульсов (). Пятый управляюи.1;ий импульс УИ-5 через схему «И 13 и схему «ИЛИ 2 поступает на счетный вход счетчика 1, работающего на вычитание импульсов (). Реверс счетчика осуществляется управляющим триггером 12, находящимся в состоянии «1 (при и ) независимо от знака АХ. Логические схемы реверса счетчика 1 на схеме не показаны. Если триггер 12 находится в состоянии «О (Х 0, ), то схема «И 13 закрыта и вычитания не происходит (п + б). Шестой управляющий импульс УИ-б открывает схемы «И 19 после окопчан-ия работы всех коммутаторов и происходит возбуждение соответствующих регистрирующих элементов и запись строки на носитель. Предмет изобретения Устройство для записи информации, содержащее усилители записи, подключенные к регистрирующим элементам и выходам схем «И, дешифратор, который подключен к триггеру, соединенному через схему «И с одним из входов схемы «ИЛИ, второй вход которой подключен к дешифратору, а выход ее - к счетчику координаты X, который подключен к промежуточногуу коммутатору, соединенному с двоичными дешифраторами, выходы которых подключены к одним из входов первой и второй групп схем «ИЛИ, другие входы которых соединены с выходами схем «ИЛИ предыдупд,его разряда той же. группы, выходы схем «Или второй группы подключены к инверторам, и группы ключей к, запоминающим регистрам, причем ключи первой группы подключены к счетчику координаты X, а запоминающий регистр первой группы - к ключам второй группы, запоминающий регистр которой соединен с ключами третьей группы, отличающееся тем, что, с пелью расширения области применения устройства, оно содержит счетчик толщины линии, входы которого подключены к ключам четвертой группы, а выходы - к третьему входу схемы «ИЛИ, и входной и выходной коммутаторы, нричем входной коммутатор подключен к выходам запоминающих регистров всех групн, промежуточному ко: 1мутатору и одним из входов выходного коммутатора, другие входы которого подключены к выходам схем «ИЛИ первой группы и выходам инверторов, а выхода его- к входам схем «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ | 1973 |

|

SU370621A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Устройство для считывания графической информации | 1983 |

|

SU1164754A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Цифровой линейный интерполятор | 1976 |

|

SU579599A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для формирования векторов на газоразрядной индикаторной панели | 1988 |

|

SU1642509A1 |

Х(з

У X

11

УИ-S If

W-J У//-2

0

W-4

i

лл Q

(f+/

TJI

/7

k

j

Крегистрируюшим элементам

Авторы

Даты

1974-05-25—Публикация

1972-04-07—Подача