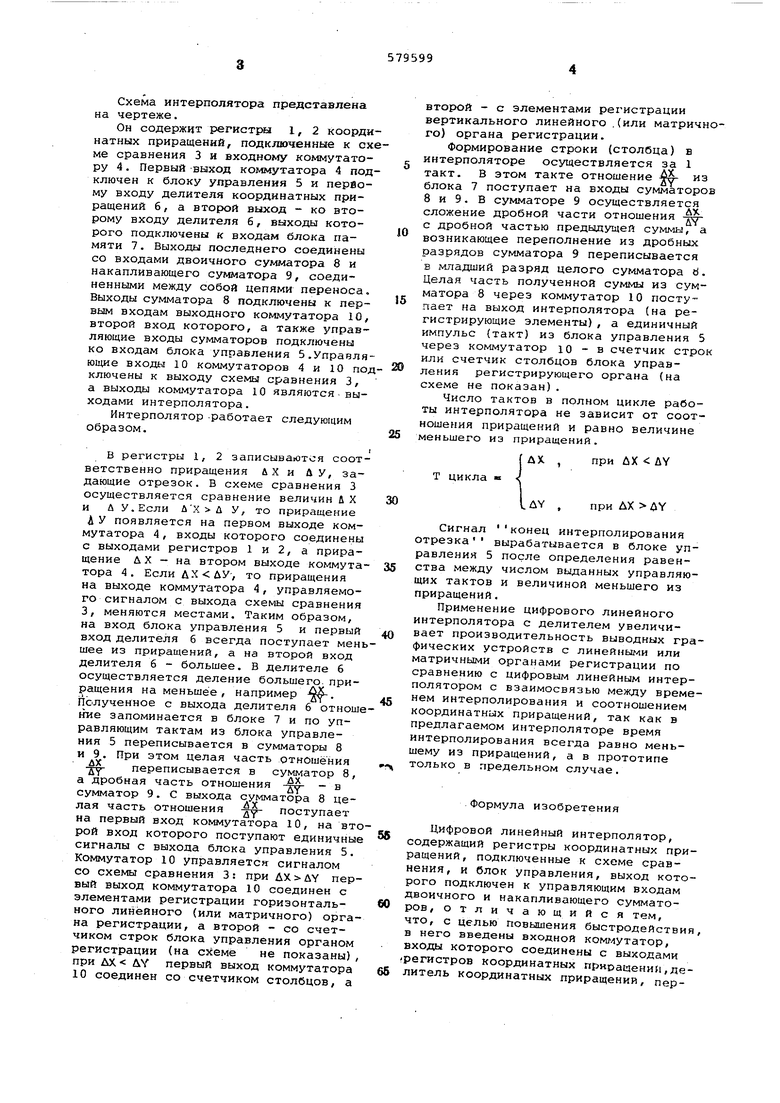

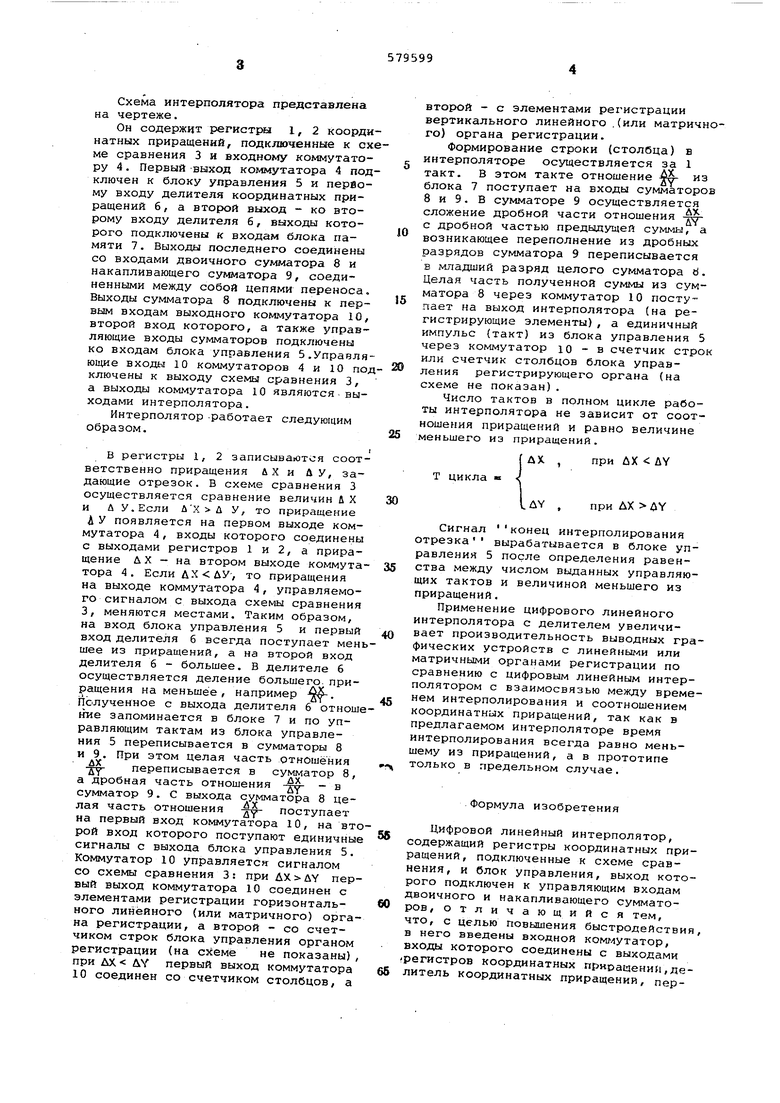

(54) ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР Схема интерполятора представлена на чертеже, Он содержит регистгйл 1, 2 коорди натных приращений, подключенные к сх ме сравнения 3 и входному коммутатору 4. Первый выход коммутатора 4 под ключен к блоку управления 5 и первому входу делителя координатных приращений б, а второй выход - ко второму входу делителя 6, выходы которого подключены к входам блока памяти 7, Выходы последнего соединены со входами двоичного сумматора 8 и накапливающего сумматора 9, соединенными между собой цепями переноса. Выходы сумматора 8 подключены к первым входам выходного коммутатора 10, второй вход которого, а также управляющие входы сумматоров подключены ко входам блока управления 5.Управля ющие входы 10 коммутаторов 4 и 10 по ключены к выходу схемы сравнения 3, а выходы коммутатора 10 являются - выходами интерполятора. Интерполятор -работает следующим Образом, в регистры 1, 2 записываются соответственно приращения ЛХ и Л У, Задающие отрезок. В схеме сравнения 3 осуществляется сравнение величин Д X и Л У.Если ЛХ Д У, то приращение Л У появляется на первом выходе коммутатора 4, входы которого соединены с выходами регистров 1 и 2, а приращение ДX - на втором выходе коммута тора 4, Если , то приращения на выходе коммутатора 4, управляемого сигналом с выхода схемы сравнения 3, меняются местами. Таким образом, на вход блока управления 5 и первый вход делителя б всегда поступает мен шее из приращений, а на второй вход делителя б - большее. В делителе б осуществляется деление большего приращения на меньшее, например -. Полученное с выхода делителя б отнош ние запоминается в блоке 7 и по управляющим тактам из блока управления 5 переписывается в сумматоры 8 и 9. При этом целая часть отношения -jy- переписывается в сумматор 8, а дробная часть отношения - в сумматор 9. С выхода сумматора 8 целая часть отношения поступает на первый вход коммутатора 10, на вт рой вход которого поступают единичны сигналы с выхода блока управления 5. Коммутатор 10 управляется сигналом со схемы сравнения 3: при ДХ ду пер вый выход коммутатора 10 соединен с элементами регистрации горизонтального линейного (или матричного) орга на регистрации, а второй - со счетчиком строк блока управления органом регистрации (на схеме не показаны) при ДХ AY первый выход коммутатора 10 соединен со счетчиком столбцов, а второй - с элементами регистрации вертикального линейного . (или матричного) органа регистрации. Формирование строки (столбца) в интерполяторе осуществляется за 1 такт. В этом такте отношение у- из блока 7 поступает на входы сумматоров 8 и 9. В сумматоре 9 осуществляется сложение дробной части отношения с дробной частью предыдущей суммы, а возникающее переполнение из дробных разрядов сумматора 9 переписывается в младший разряд целого сумматора 6. Целая часть полученной суммы из сумматора 8 через коммутатор 10 поступает на выход интерполятора (на регистрирующие элементы), а единичный импульс (такт) из блока управления 5 через коммутатор ю - в счетчик строк или счетчик столбцов блока управления регистрирующего органа (на схеме не показан). Число тактов в полном цикле работы интерполятора не зависит от соотношения приращений и равно величине меньшего из приращений. при ЛХ ДУ Т цикла при ДХ AY Сигнал конец интерполирования отрезка вырабатывается в блоке управления 5 после определения равенства между числом выданных управляющих тактов и величиной меньшего из приращений. Применение цифрового линейного интерполятора с делителем увеличивает производительность выводных графических устройств с линейными или матричными органами регистрации по сравнению с цифровым линейным интерполятором с взаимосвязью между временем интерполирования и соотношением координатных приращений, так как в предлагаемом интерполяторе время интерполирования всегда равно меньшему из приращений, а в прототипе только в предельном случае. Формула изобретения Цифровой линейный интерполятор, содержащий регистры координатных приращений, подключенные к схеме сравнения, и блок управления, выход которого подключен к управляющим входам двоичного и накапливающего сумматоров, отличающийся тем, что, с целью повышения быстродействия, в него введены входной KOMf-iyTaTOp, входы которого соединены с выходами егистров координатных пЕ ираиени{1,делиталь координатных приращении, первый и второй входы которого соединены с первым и вторым входами входного коммутатора, первый выход которого соединен со входом блока управления, блок памяти, входы которого подключен ны к выходам делителя координатны приращений, а выходы - к входам двоичного и накапливающего сумматоров, я выходной коммутатор, первые входы которого соединены с выходами двоичного сумматора, второй вход - с выходом блока управления, а управляю1дие входы коммутаторов подключены к выходу схемы сравнения.

Источники информации, принятые во внимание при экспертизе:

1,Авторское свидетельство СССР W 377822, М, Кл G 05 В 19/18 1971,

2,Авторское свидетельство СССР

М 259492, М, Кл, G 05 Б 19/18, 1968.

3,Заявка 2112695/24,

М. G 05 В 19/16, 1975 г., по которой принято решение о вы/шче авт. сзид.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1975 |

|

SU529458A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Линейный интерполятор | 1975 |

|

SU543922A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Трехкоординатный линейный интерполятор | 1982 |

|

SU1037214A1 |

| Многокоординатный регулятор линейнойСКОРОСТи | 1978 |

|

SU798728A1 |

Авторы

Даты

1977-11-05—Публикация

1976-07-22—Подача