1

Изобретение касается построения узлов вычислительной техники и дискретной автоматики в микроэлектронном исполнении, в частности в виде больших интегральных схем (БИС).

Известно устройство, построенное в логическом базисе «И-ИЛИ-НЕ на основе двух триггеров-триггера памяти с Л устойчивыми состояниями, каждое плечо которого содержит вентиль ввода информации, причем первый вход этого вентиля соединен со счетным входом кольцевого счетчика, вентиль памяти, и коммутационного триггера с устойчивыми состояниями, содержащего в каждом плече по одному вентилю ввода информации и по одному вентилю памяти, вход которого соединен со счетным входом кольцевого счетчика.

Однако в таком устройстве необходимо применение дешифратора, усложняющего его схему, увеличивающего величину потребляемой мощности за счет сравнительно большого количества иснользуемых активных логических элементов «И-ИЛИ-НЕ.

Предложенный счетчик отличается тем, что для его упрощения каждое плечо коммутациониого триггера содержит по () вентилей памяти, входы которых соединены с выходами всех остальных плеч этого триггера, за исключеиием предыдунхего смежного плеча. Первые входы вентилей ввода информации

любого плеча коммутационного триггера соединены с выходами одноименных нлеч триггера памяти, а вторые входы этих вентилей памяти соединены соответственно с выходами

предыдущих смежных плеч этого триггера. Вторые входы вентилей ввода ииформации триггера памяти соединены соответственно с выходами предыдущих смежных плеч коммутационного триггера.

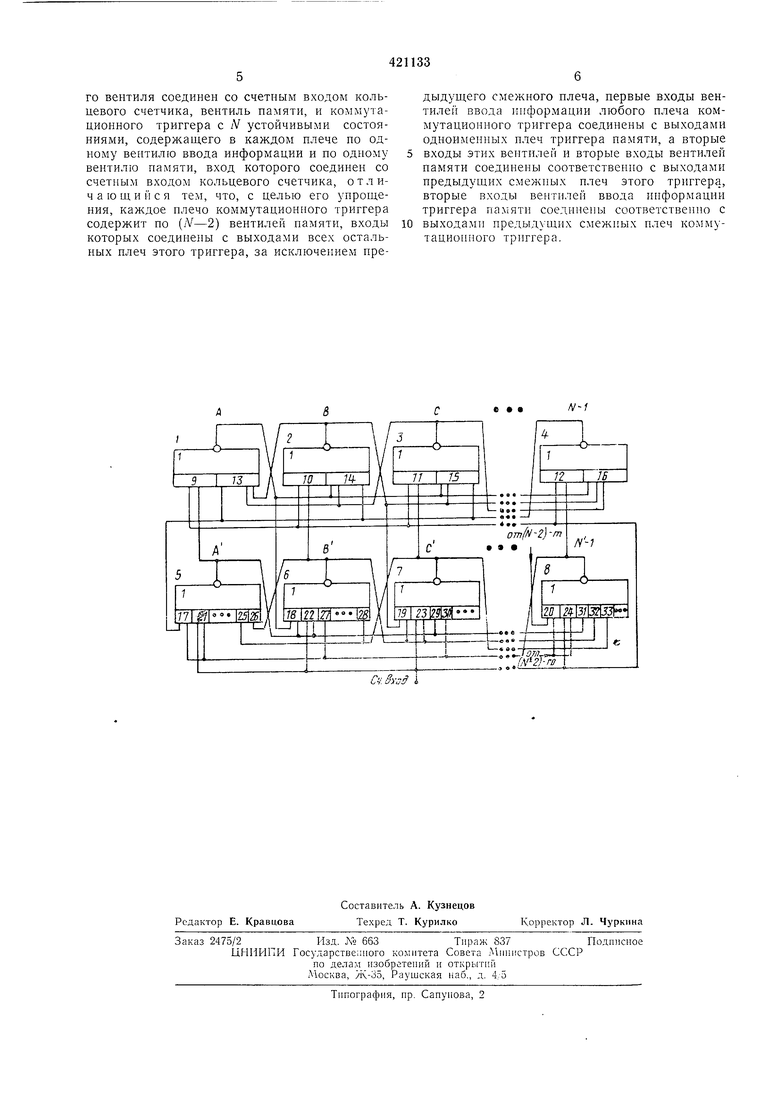

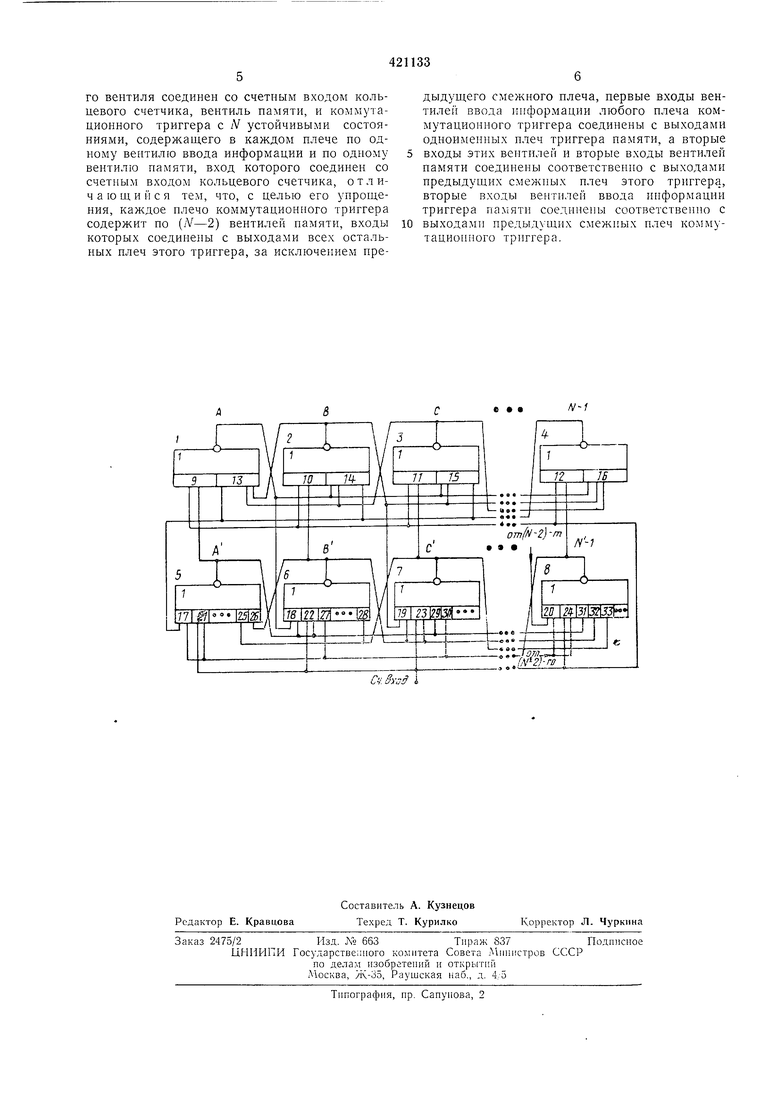

На чертеже приведена функциональная схема предложеппого кольцевого счетчика по модулю N, где , 3, 4 ...; па фнг. 2 - таблица состояний этого счетчика. Предложенный счетчик построен в логическом базисе «И-ИЛИ-НЕ и образован соединением двух триггеров - триггера памяти с Л устойчивыми состояниями (элемеиты 1, 2, 3, . .., 4) и коммутационного триггера с Л устойчивыми состояниями (элементы 5, 6, 7, . . ., 8).

Плечи триггера памяти (элементы 1, 2, 3, ..., 4) содержат по одному вентилю ввода информации 9-12 и по одному вентилю намяти 13-16 для образования триггерных связей, входы вентиля памяти любого плеча триггера

памяти соедипены с выходами всех остальных плеч этого трпггера. Первые входы вентилей ввода ииформацни всех нлеч триггера памяти соединены со счетным входом кольцевого счетчика, а вторые входы этих вептилей соединены соответственно с выходами предыдущих смежных плеч (в том числе (Л-1)-го плеча - для нулевого) коммутациопного триггера, Плечи коммутациоиного триггера (элементы 5, 6, 7, ..., 8) содержат по одпому вентилю ввода информации 17-20, по одпому вентилю памяти, осуп1ествляю1цих перехват предыдуп его состояния коммутационного триггера при переключении триггера памяти, - вептилц 21-24, -и по (V-2) вентилей памяти 25-33 для образования триггерных связей, входы вентилей памяти любого плеча коммутациоппого триггера соединены с выходами всех остальных плеч этого триггера, за исключением нредыдущего смежного плеча (в том числе (Л-1)-го плеча - для нулевого). Первые входы вептнлей ввода информации любого плеча коммутационного триггера соединены с выходами одноиме1 ных плеч триггера памяти, а вгорые входы этих вентилей соединеиы соответственно с выходами предыдун:1,их смежных нлеч этого триггера, (в том числе (Л-)-го плеча для нулевого). Первые входы вентилей кратковремеппой памяти любого плеча коммутационного триггера соединены со счетным входом кольцевого счетчика, а вторые входы этих вентилей соединены соответственно с выходами нредыдуншх смежных плеч этого триггера (в том числе (Л-1)-го плеча для нулевого).

При поступлении счетных имнульсов переключается только одно плечо триггера памяти, выбор которого определяется состояииями предыдущего плеча (в том числе (Л-1)-го плеча для нулевого) этого триггера и коммутационного триггера. После окончания счетного имнульса коммутационный триггер переключается в новое состояние в соответствии с новым состоянием триггера памяти. Стабильпость состояний коммутационного триггера нри переключении триггера памяти достигается за счет перехвааа нредыдущего состояния ко.ммутационпого триггера при поступлении счетных импульсов на вентили (на время длительности этих импульсов) памяти.

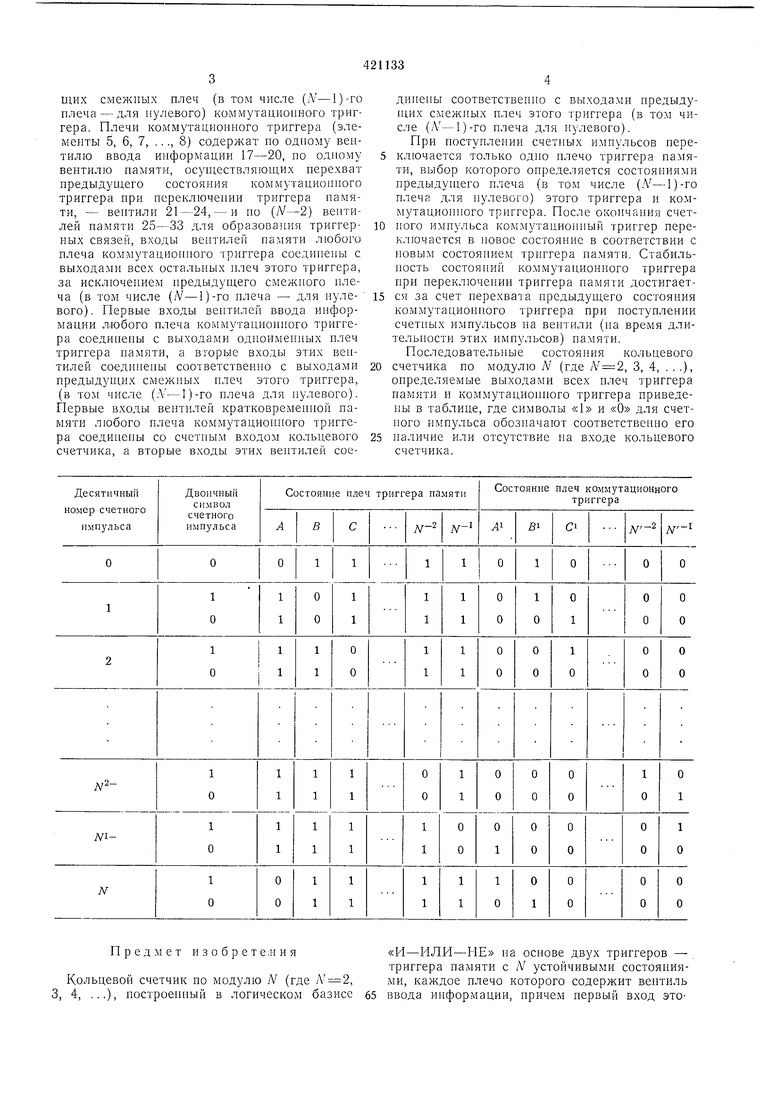

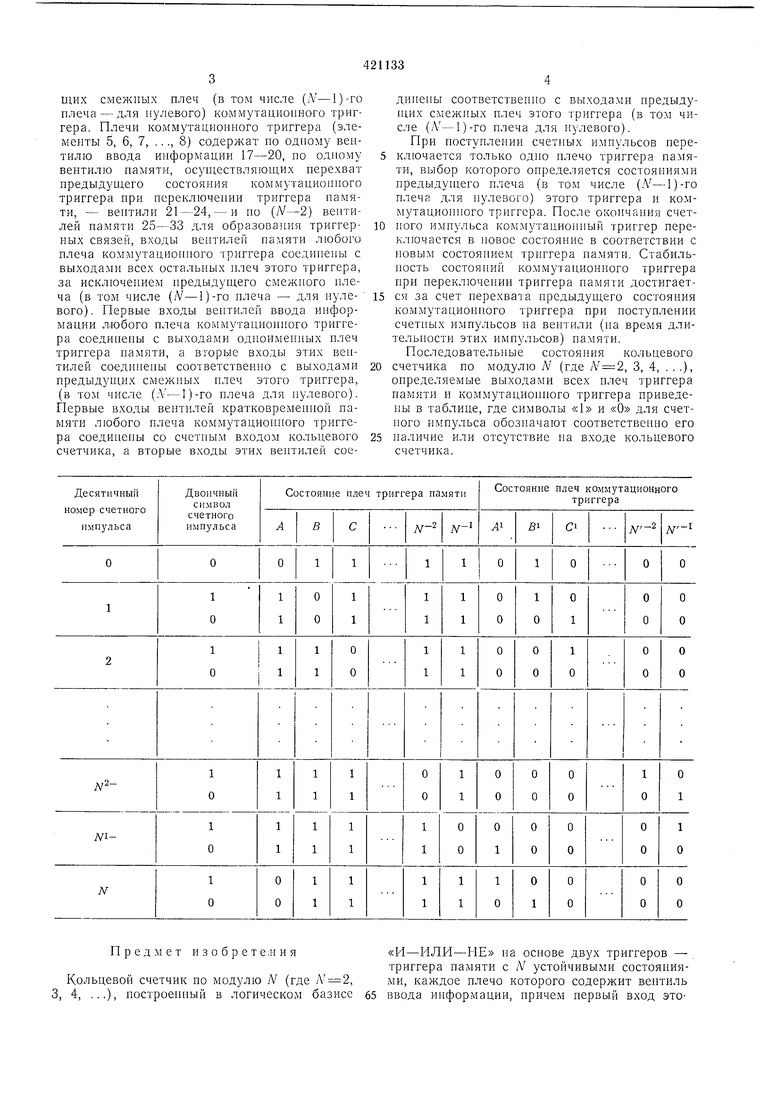

Последовательпые состояния кольцевого счетчика по модулю N (где , 3, 4, . . .), определяемые выходами всех плеч триггера памяти и коммутациоппого триггера приведены в таблице, где символы «1 и «О для счетного импульса обозначают соответственно его наличие или отсутствие на входе кольцевого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ С 2/V+1 УСТОЙЧИВЫМИСОСТОЯНИЯМИ | 1972 |

|

SU429537A1 |

| Счетчик по модулю 4 | 1972 |

|

SU523529A1 |

| Разряд счетчика по модулю три | 1971 |

|

SU445989A1 |

| Реверсивный счетчик с последовательным переносом | 1974 |

|

SU516196A1 |

| Реверсивный счетчик | 1977 |

|

SU708516A2 |

| Реверсивное счетное устройство | 1989 |

|

SU1713100A1 |

| Реверсивный регистр сдвига | 1974 |

|

SU593317A1 |

| Реверсивный счетчик | 1985 |

|

SU1257839A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ГРУППОВЫМ ПЕРЕНОСОМ | 1970 |

|

SU287121A1 |

| ИЗОБРНТ37М. Кл. Н 0.3k 23/04УДК 621.374.4(088.8) | 1973 |

|

SU407426A1 |

Предмет изобрете:ния Кольцевой счетчик по модулю /V (где N 2, 3, 4, ...), построеппый в логическом базисе 65 «И-ИЛП-ПЕ на основе двух триггеров - . триггера памяти с Л устойчивыми состояниями, каждое плечо которого содержит вентиль ввода информации, причем первый вход этого вентиля соединен со счетным входом кольцевого счетчика, вентиль памяти, и коммутационного триггера с V устойчивыми состояниями, содержащего в каждом нлече по одному вентилю ввода информации п по одному вентилю памяти, вход которого соединен со счетным входом кольцевого счетчика, о т л ич а ю щ и Ii с я тем, что, с целью его упрощения, каждое плечо коммутационного триггера содержит по (jV-2) вентилей памяти, входы которых соединены с выходами всех остальных плеч этого триггера, за исключением предыдущего смежного плеча, первые входы вентилей ввода информации любого плеча коммутационного триггера соединены с выходами одноименных плеч триггера памяти, а вторые входы этих вентилей и вторые входы вентилей памяти соединены соответственно с выходами предыдущих смежных плеч этого триггера, вторые входы вентилей ввода информации триггера памяти соединены соответственно с выходами предыдущих смежных нлеч коммутационного триггера.

N-1

е

С.ВУ:; I

Даты

1974-03-25—Публикация

1972-08-09—Подача