1

Изобретение относится к средствам технической кибернетики.

Известен преобразователь кода временной интервал, содержащий устройстео управления, устройство записи преобразуемого кода, регистр памяти младших разрядов преобразуемого чИ|Сла, 1селектор, тригг управления селектором, счетчик, формирователь импульса конца временного инте(рвала, генератор «алряжбния считываиия и ком.мутируемую линию задержки.

Однако Иопользуемые в таком преобразователе для уменьшения дискретности преоб(разования коммутируемые линии задержки ие обеСПечявают требуемой точности преобразования, так как при прохождении им-пульоов через лийию задержки искажается их форма, что вносит существенную погрешность; для уменьшения искажений необходимо применять широкополосные линии задержки, а это ведет к увеличению габаритов, потребляемой мощности и стоимости annapaiypbi; неполное согласаваиие лниии вносит дополиителыные погрешности; изготовление линий с плавной регулировкой величины заде1рж1ки наталкивается на определенные трудности технологического и конст1ру1ктивнопо характера.

Цель изобретения - по вышение точности преобразования.

Это достигается тем, что в предлагаемый

преобразователь дополнительно введены последовательно соединенные ко:ммутируемые фазосдвигающие каскады и усилитель-ограничитель, при этом выхюд генератора синусоидалыного напряжения считывания соединен с входом первого фазосдвигающсго каскада, выход последнего фазосдвигающего каскада подключен к входу усилителя-ограничителя, выход которого соединен с входом селектора, управляющие входы фазосдвигающих каскадов подключены к соответствующим выходам регистра памяти младших разрядов, старт-импульсный выход устройства правления соединен с входо-м коммутируемой линии задержки, управляющий вход которой подключен к выходу старшего разряда регистра памяти младших разрядов, а ее выход - к единичному входу триггера управления селектором.

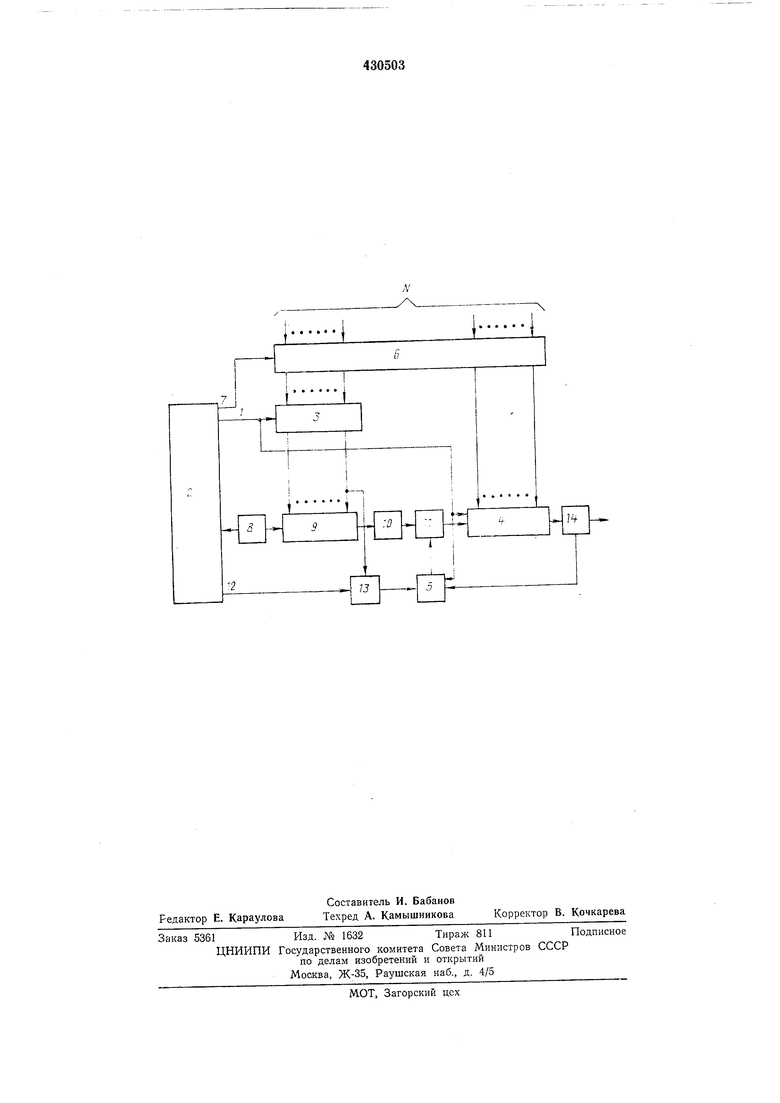

На чертеже изображена схема предлагаемого преобразователя.

Преобразователь работает следующим образом.

Импульсом сброса, поступающим с выхода 1 устройства управления 2, регистр памяти- 3 младших разрядов преобразуемого числа, счетчик 4 и триггер 5 управления селектором устанавливаются в исходное состояние. Код, поступающий на вход устройства записи 6 преобразуемого кода, импульсом записи

с выхода 7 переписывается в регистр па:мяти 3 и .в счетчик 4. Пр,и этом в регистр памяти записывается прямой «од младших разрядов преобразуемого числа, а в счетчик - обратный код старших разрядов. С выхода генератора 8 эталонное синусоидальное напряжение считывания подается .на вход пocлeдaвaтe ьнo соединенных коммутируемых фа засдвига10щих каскадов 9, где П|роиз1водит1ся задержка ПО фазе этого напряжения. Величина задержки по фазе напряжения счнтывания пропорциональна значению кода в младших разрядах преобразуемого числа и определяется выражением

rt-l

ф(П1)Дф.,. (),

г 0

где (f{ni) - величина фазовой задержки напряжения считывания; П1 - значение кода в младших разрядах преобразуемого числа; Аф - величина минимального сдвига фазы, соответствующая диюкретт

ности преобразования А -

(Т - период напряжения считывания) ;

Ф( (i) - величина фазового сдвига

1-го каскада на частоте считывания;

п - число разрядов регистра памяти 3;

г 0,1,2,..., п-1 - порядковый номер разряда; 0,1 - значение кода в t-м разряде.

Таким образом, напряжение считывания задерживается на время, равное At п.

С выхода последнело фазосдвнгаюшего каскада напряжение считывания поступает на вход усилителя-ограничителя 10, где из синусоидального напряжения формируется прямоуголыное напряжение. Это напряжение подается на сигнальный вход селектора 11. Стартимпульс с выхода 12 устройства управления 1 проходит через коммутируемую линию заде:ржки 13. При этом, если в старшем разряде регистра памяти, управляющем линией задержки, записана «единица, то старт-импульс задерживается на время, paiBHoe половине периода напряжения считывания, а если записан «ноль, то старт-импулыс проходит без задержки. С выхода линии задержки

старт-вмпульс поступает на единичный вход триггера 5, селектор // открывается, и на вход счетчика 4 проходят импульсы прямоугольного напряжения, задержанного относительно старт-импульса на время, проиорциональное значению кода в регистре памяти 3 младших разрядов. В момент переполнения счетчика 4 формирователь импулыса 14 конца преобразования сбра)СЫвает триггер 5 в «ноль. Задержка импульса окончания преобразования относительно старт-импульса равна t ni/ t+n2T (где П2 - значение кода в старших разрядах преобразуемого чнсла, записываемое в счетчик 4).

П р е д ;м е Т изобретения

Преобразователь кода во временной интервал, соде|ржащий устройство упра;вления, устройспво записи преобразуемого кода, регистр

памяти младших разрядов преобразуемого , селектор, триггер управления селектором, счетчик, формирователь импульса конца временного интервала, генератор напряжения считывания и коммутируемую линию задержки, отличающийся тем, что, с целью повышения точности преобразо1вания, в него введены последовательно соединенные коммутируемые фазосдвигающие каскады и усилительограничитель, при этом выход генератора синусоидального напряжения считывания соединен с входом первого фазосдвигающего каскада, выход последнего фазосдвигающего каскада подключен к входу усилителя-ограничителя, выход которого соединен с входом селектора, управляю щие входы фазосдвигающих каскадов подключены к соответствующим выходам регист|ра памяти младших разрядов,старт-им:Пульоный выход устройства упраовления соединен с входом коммутируемой линии

задержки, управляющий вход которой подключен к выходу старшего разряда регистра памяти младших разрядов, а ее выход - к единичному входу триггера упра:вления селектором.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ВО ВРЕЛ1ЕННОЙ ИНТЕРВАЛ | 1972 |

|

SU360718A1 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2014 |

|

RU2570116C1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Преобразователь код-временной интервал | 1986 |

|

SU1361721A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Измеритель однократных временных интервалов | 1974 |

|

SU571787A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1106011A1 |

Авторы

Даты

1974-05-30—Публикация

1972-05-06—Подача