о ю ю

DS

00

Изобретение относится к радиотехнике и может быть использовано в системах синхронизации, в синхронизирующих устройствах для коррекции шкалы времени.

Известно устройство для коррекции шкалы времени, содержащее генератор, хранитель времени, регистр сдвига, элемент И, счетчик, делитель частоты и два формирователя управляющих сигналов.

Известно также устройство для коррекции шкалы времени, содержащее генератор тактовых импульсов, два делителя частоты. регистр сдвига, элемент И, формирователь импульсов, блок сравнения кодов и два триггера.

Кроме того, известно устройство для коррекции шкалы времени, содержащее генератор, фазосдвига1ощий блок, делитель частоты, электронный переключатель, элемент И, два счетчика импульсов, сумматор, регистр сдвига, преобразователь кода коррекции, дешифратор, формирователь сигнала управления, элемент ИЛИ и формирователь одиночных импульсов.

Указанные устройства имеют низкую помехоустойчивость, так как искажение кода коррекции призаписи его в регистр сдвига, наприме Pi вследствие воздействия помех приводит к ошибке в коррекции формируемой в устройстве шкалы времени. Кроме того, под дейстивем помех возможно несанкционированное проведение коррекции на произвольную величину, что приводит к ошибке формирования времени..

Наиболее близким к предлагаемому является устройство для коррекции шкалы времени, которое содержит последовательно соединенные генератор, фазосдвигающий блок и делитель частоты, а также реверсивный счетчик, регистр сдвига, преобразователь кода коррекции, элемент И, счетчик, дешифратор, формирователь одиночных импульсов (ОИ) и формирователь сигнала управления (СУ). Входы преобразователя являются входом сигнала Код коррекции устройства {информационным входом устройства). Информационный и тактовый выход преобразователя подключены к соответствующим входам регистра, выход младшего разряда которого подключен к первому управляющему входу фазосдвигающего блока, а выходы старших разрядов соединены с входами записи счетчика. Тактовый выход преобразователя подключен к счетному входу счетчика, вход установки которого является входом сигнала Ввод коррекции устройства. Выходы разрядов счетчика через дешифратор подключены к первому входу формирователя

ОИ, второй вход которого соединен с первым входом элемента И и с выходом фазосдвигающего блока. Выход элемента И подключен к входу вычитания счетчика, выход которого через формирователь СУ соединен с вторым управляющим входом фазосдвигающего блока и с вторым входом элемента И. Выход формирователя ОИ подключен к второму входу формирователя СУ

0 и к входу предварительной записи счетчика. Известное устройство работает следующим образом.

Генератор является источником импульсов стабильной частоты, например, 5

5 МГц для запуска фазосдвигающего блока, который выполнен в виде делителя частоты С переменным коэффициентом деления. В исходном состоянии коэффициент деления фазосдвигающего блока равен К, что опре0 деляется наличием на его втором управ; ляющем входе сигнала О с выхода формирователя СУ независимо от уровня сигнала на первом управляющем входе. Импульсы с выхода фазосдвигающего блока

5 поступают на вход делителя.

Делитель производит дальнейшее деление частоты генератора 1, например, до 1 /60 Гц и осуществляет счет времени (минут и часов). Формируемая делителем шкала

0 времени представляет собой совокупность импульсных сигналов с частотами от частоты входного сигнала делителя до 1 /60 Гц и кода времени (минут и часов).

Коррекция шкалы времени происходит

5 следующим образом.

На вход Ввод коррекции устройства, т.е. на вход R счетчика подается импульс. При этом-счетчик сбрасывается и на выходе дешифратора появляется сигнал О, который подготавливает к работе формирователь ОИ. На информационный вход устройства, т.е. на первый и второй входы преобразователя, подается последовательный код коррекции, имеющий следующую

5 структуру: младший разряд- знак, старшие разряды - величина коррекции в двоичном коде. Код коррекции поступает по двум линиям связи, например, в виде кода единиц и кода нулей. При этом 1 кода коррекции

0 соответствует наличие импульса на линии связи кода единиц и отсутствие импульса на линии связи кода нулей, а О - отсутствие импульса на линии связи кода единиц и наличие импульса на линии связи

5 кода нулей. На информационном выходе преобразователя формируется прямой последовательный код коррекции, который записывается в регистр под воздействием тактовых импульсов, формирующихся на тактовом выходе преобразователя. Одновременно счетчик подсчитывает число тактовых импульсов, т.е. число записанных в регистр разрядов кода коррекции. При записи в регистр всех разрядов кода на выходе дешифратора появляется сигнал 1. который запускает формирователь. Формирователь ОИ выделяет второй с момента своего запуска импульс из последовательности импульсов, поступающих на его первый вход с выхода блока фазосдвигающего. Импульс с выхода формирователяОИ поступает на вход предварительной записи счетчика и на второй вход формирователя СУ. При этом по переднему фронту импульса с выхода формирователя ОИ код, определяющий величину коррекции, из старших разря дов регистра записывается в счетчик, на выходе которого появляется сигнал К. Этот сигнал 1 поступает на первый формирователя СУ, разрешая формирование сигнала управления. Сигнал управления в виде сигнала 1 появляется на выходе формирователя СУ по заднему фронту импульса на выходе формирователя ОН. Сигнал управления с выхода формирователя СУ поступает на второй управляющий вход блока фазосдвигающего и изменяет его коэффициент деления на Ktl в зависимости от знака коррекции, поступающего на первый управляющий вход фазосдвигающего блока с выхода младшего разряда регистра. Изменение коэффициента деления фазосдвигающего блока приводите сдвигу формируемой делителем шкалы времени. Одновременно сигнал управления разрешает прохождение импульсов с выхода блока через элемент И на вход вычитания счетчика. Двоичный код величины коррекции, записанный в счетчике, начинает считываться. По окончании считывания, когда счетчик обнуляется на его выходе появляется сигнал О, который возвращает формирователь СУ в исходное состояние. Сигнал О с выхода формирователя СУ восстанавливает исходный коэффициент деления К фазосдвигающего блока и запрещает прохождение импульсов через элемент И на вход вычитания счетчика. На этом коррекция шкалы времени заканчивается.

Величина сдвига шкалы времени равна Д t ± N Т, где N - число, соответствующее двоичному коду величины коррекции; Т период повторения импульсов генератора.

Известное устройство имеет низкую помехоустойчивость, так как искажение вводимого в устройство кода коррекции, например, в результате воздействия помех приводит к ошибке коррекции. Кроме того, из-за слабой защищенности входа сигнала Код коррекции устройства импульсы помех могут привести к записи в устройство произвольного кода коррекции и запуску формирователя ОИ, что приводит к несанкционированной коррекции шкалы времени 5 на произвольную величину.

Таким образом, недостаток известного устройства для коррекции шкалы времени обусловлен низкой помехоустойчивостью. Цель изобретения - повышение помехо0 устойчивости.

Сущность изобретения состоит в том, что в устройство для коррекции шкалы времени, содержащее последовательно соединенные генератор, фазосдвигающий блок и

§ делитель частоты, реверсивный счетчик,

.регистр сдвига, преобразователь кода коррекции, элемент И, последовательно соей ненные счетчик, дешифратор и формирователь одиночных импульсов, а

0 также формирователь сигнала управления, причём выход элемента И подключен к входу вычитания реверсивного счетчика, выход которого соединен с первым входом формирователя сигнала управления, выход младшего разряда регистра сдвига подключен к первому управляющему входу фазосдвигающего блока, выход которого соединен с первым входом элемента И и с вторым входом формирователя одиночных импульсов,

0 выход формирователя сигнала управления подключен к второму управляющему входу фазосдвигающего блока и к второму входу элемента И, выходы старших разрядов регистра сдвига подключены к входам записи

5 реверсивного счетчика, информационный и тактовый выходы преобразователя кода коррекции подключены к соответствующим входам регистра сдвига, тактовый выход преобразователя кода коррекции прдклю0 чен к счетному входу счетчика, введены три дополнительных элемента И, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и три триггера, при этом первые входы первого и второго дополнительных элементов И

5 являются входом сигнала Код коррекции, вторые входы подключены к выходу первого триггера, а выходы подключены соответственно к первому и второму входам преобразователя кода коррекции, выход

0 формирователя одиночных импульсов через третий дополнительный элемент И соединен с входом предварительной записи реверсивного счетчика и с вторым входом формирователя сигнала управления, а также подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом делителя частоты, выход дополнительного старшего разряда регистра сдвига подключен к входу синхронизации второго триггера, выход младшего разряда и выход

дополнительного старшего разряда регистра сдвига через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к первому входу установки третьего триггера, второй вход установки которого соединен с выходом второго триггера и с входом установки счетчика, дополнительный выход преобразователя кода коррекции подключен к входу синхронизации третьего триггера, выход которого подключ.ен к второму входу третьего дополнительного элемента И, первый вход установки первого триггера является входом СИГ1Нала Ввод коррекции, выход дешифратора подключен к третьему, входу третьего дополнительного элемента И, вход установки второго триггера соединен с первым входом установки первого триггера, второй вход установки которого подключен к выходу элемента ИЛИ.

Повышение помехоустойчивости достигается за счет разрешения записи в регистры сдвига только на время передачи кода и контроля правильности приема кода,

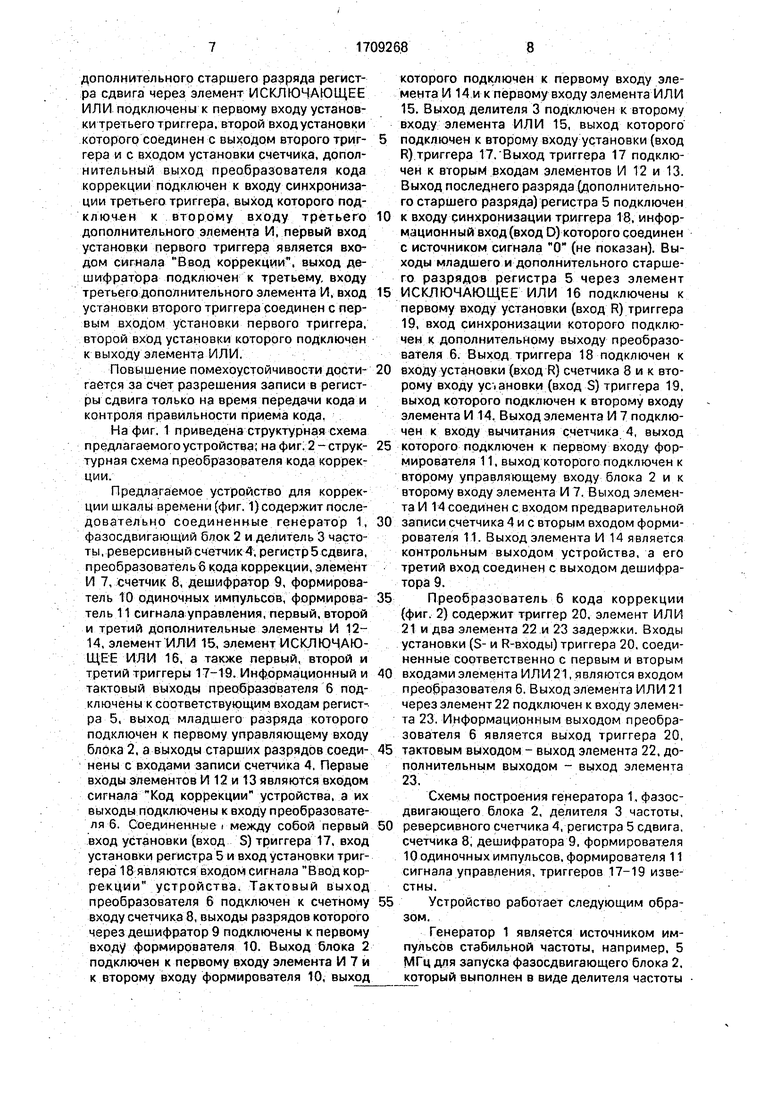

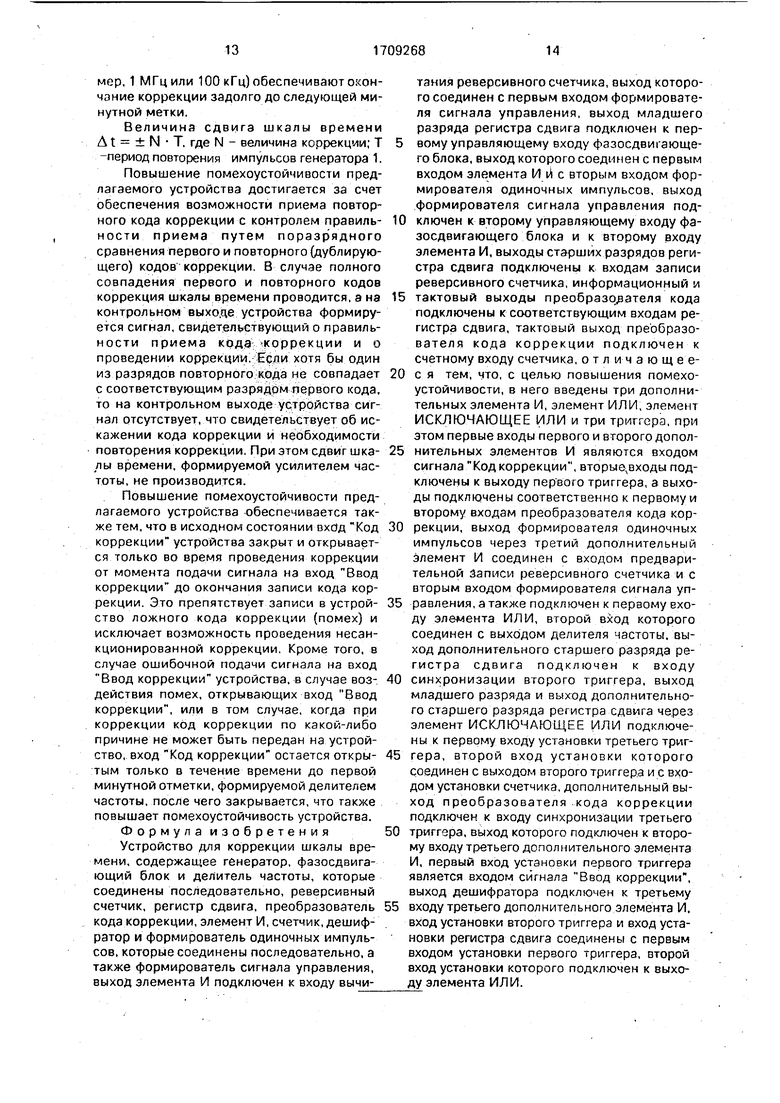

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг;2-структурная схема преобразователя кода коррекции.

Предлагаемое устройство для коррекции шкалы времени (фиг. 1) содержит последовательно соединенные генератор 1, фазосдвигающий блок 2 и делитель 3 частоты, реверсивный счетчик 4, регистр 5 сдвига, преобразователь6 кода коррекции, элемент И 7. счетчик 8, дешифратор 9. формирователь 10 одиночных импульсов, формироваталь 11 сигнала управления, первый, второй и третий дополнительные элементы И 1214, элемент ИЛИ 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16. а также первый, второй и третий триггеры 17-19. Информационный и тактовый выходы преобразователя 6 подключены к соответствук)Щим входам регистра 5, выход младшего разряда которого подключен к первому управляющему входу блока 2, а выходы старших разрядов соединены с входами записи счетчика 4. Первые входы элементов И 12 и 13 являются входом сигнала Код коррекции устройства, а их выходы подключены к входу преобразователя 6. Соединеннью I между собой первый вход установки (вход S) триггера 17. вход установки регистра 5 и вход установки триггера 1В являются входом сигнала Ввод коррекции устройства. Тактовый выход преобразователя 6 подключен к счетному входу счетчика 8, выходы разрядов которого через дешифратор 9 подключены к первому входу формирраателя 10. Выход блока 2 подключен к первому входу элемента И 7 и к второму входу формирователя 10, выход

которого подключен к первому входу элемента И 14 и к первому входу элемента ИЛИ 15, Выход делителя 3 подключен к второму входу элемента ИЛИ 15, выход которого подключен к второму входу установки (вход R) триггера 17.Выход триггера 17 подключен к вторым рходам элементов И 12 и 13. Выход последнего разряда Дополнительного старшего разряда) регистра 5 подключен к входу синхронизации триггера 18, информационный вхрд (вход D) которого соединен с источником сигнала О (не показан). Выходы младшего и дополнительного старшего разрядов регистра 5 через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16 подключены к первому входу установки (вход R) триггера 19. вход синхронизации которого подключен к дополнительному выходу преобразователя 6. Выход триггера 18 подключен к входу установки (вход R) счетчика 8 и к второму входу ус1ановки (вход S) триггера 19, выход которого подключен к второму входу элемента И 14. Выход элемента И 7 подключен к входу вычитания счетчика 4, выход которого подключен к первому входу формирователя 11. выход которого подключен к второму управляющему входу блока 2 и к второму входу элемента И 7. Выход элемента И 14 соединен с входом предварительной записи счетчика 4 и с вторым входом формирователя 11. Выход элемента И 14 является контрольным выходом устройства, а его третий вход соединен с выходом дешифратора 9.

Преобразователь 6 кода коррекции (фиг. 2) содержит триггер 20. элемент ИЛИ 21 и два элемента 22 и 23 задержки. Входы установки (S- и R-входы) триггера 20. соединенные Соответственно с первым и вторым входами элемента ИЛИ 21, являются входом преобразователя 6. Выход элемента ИЛИ 21 через элемент 22 подключен к входу элемента 23. Информационным выходом преобразователя 6 является выход триггера 20, тактовым выходом - выход элемента 22, дополнительнцм выходом - выход элемента 23.

Схемы построения генератора 1. фазосдвигающего блока 2, делителя 3 частоты, реверсивного счетчика 4, регистра 5 сдвига, счетчика 8; дешифратора 9, формирователя 10 одиночных импульсов, формирователя 11 сигнала управления, триггеров 17-19 известны.

Устройство работает следующим образом.

Генератор 1 является источником импульсов стабильной частоты, например, 5 МГц для запуска фазосдвигающего блока 2, который выполнен в виде делителя частоты

с переменным коэффициентом деления. В исходном состоянии коэффициент деления блока 2 равен К, что определяется наличием на его втором управляющем входе сигнала О с выхода формирователя 11 независимо от уровня сигнала на первом управляющем входе. Импульсы с выхода блока 2 поступают на вход делителя 3.

Делитель 3 производит дальнейшее деление частоты генератора 1 до 1/60 Гц и осуществляет счет времени (минут и часов). Формируемая делителем 3 гикала времени представляет собой совокупность импульс ных сигналов с частотами от частоты входного сигнала делителя 3 до 1/60 Гц и кода времени (минут и часов).

Коррекция-шкалы времени в предлагаемом устройстве производится следующим образом.

На вход Ввод коррекции устройства подается импульс, который поступает на вход S триггеров 17 и 18 и на вход установки регистра 5. При этом триггеры 17 и 18 устанавливаются в единичное состояние. 1 с выхода триггера 17, поступая на вторые входы элементов И 12 и 13, разрешает прохождение сигналов с входа Код коррекции устройства на вход преобразования 6. 1 с выхода триггера 18 сбрасывает счетчик 8, блокируя его работу. При этом на выходе дешифратора 9 появляется О, который подготавливает к работе формирователь 10 и блокирует элемент И 14. При поступлении импульса на вход установки регистра 5 на выходе его младшего разряда устанавливается сигнал Гч на выходах старших разрядов - сигнал О.

На вход Код коррекции устройства пог дается код коррекции. Код коррекции имеет следующую структуру: младший разряд знак коррекции, старшиеразряды-величина коррекции в двоичном коде. Код коррекции передается два . Код передается по двум линиям связи в виде кода единиц и кода нулей. При этом 1 кода коррекции соответствует наличие импульса на линии связи кода единиц и отсутствие импульса на линии связи кода нулей, а О кода коррекции соответствует отсутствие импульса на линии связи кода единиц и наличие импульса на линии связи кода нулей. Код единиц и код нулей через элементы И 12 и 13 соответственно поступают на первый и второй входы преобразователя 6.

Источником кода коррекции, передаваемого таким образом, может служить аппаратура 17Н617, 17Н676 и др.

В преобразователе 6 (фиг. 2) импульсы кода единиц и кода нулей поступают соответственно на входы S и R триггера 20 и на входы элемента ИЛИ 21. При этом на выходе триггера 20 формируется прямой последовательный код коррекции, поступающий на информационный выход преобразователя 6. На выходе элемента ИЛИ 21 из импульсов кода единиц и кода нулей путем их логического сложения формируется тактовая серия импульсов, которая 10 через элемент 22 задержки поступает на тактовый выход преобразователя 6. При этом задержку ri элемента 22 устанавливают дрстэтрчной для надежной записи кода коррекции в регистр 5. Тактовая серия им15 пульсоас в| «|РОДа элемента 22 через элемент 23 поступитмадополнительный выход преобразова трял задержку Г2 элемента 23 уст9 м4 -|в к 3 меньшезадержки срабатывания региртра 5. 0 Прямой код коррекции и тактовая серия импульсов с информационного и тактового выходов преобразователя 6 поступают на соответствующие входы регистра 5. При этом разряды кода коррекции поочередно 5 записываются в регистр 5.

Одновременно тактовая серия импульсов с дополнительного выхода преобразователя 6 поступает на вход синхронмзации триггера 19, при этом на его выходе поддерживается сигнал Г так как на его входе S присутствует сигнал 1 с выхода триггера 18.

По мере записи кода коррекции 1, первоначально установленная в младшем 5 разряде регистра 5, перемещается к старЩему разряду. Как только весь код коррекции записывается в регистр. 5 (во все его разряды, кроме последнего - дополнительного старшего разряда) на выходе дополнительного старшего разряда регистра 5 появляется 1, которая поступает на вход синхронизации триггера 18. При этом в триггер 18 записывается О, который поступает на вход S триггера 19 и на вход R 5 счетчика 8, разрешая счет импульсов счетчиком 8.На вход Код коррекции устройства подается повторный код коррекции, который через преобразователь 6 записывается в регистр 5. Запись каждого разряда повторного кода коррекции в регистр 5 вызывает сдвиг ранее записанного в регистр 5 кода коррекции. При этом на выходе дополнительного старшего разряда регистра 5 последовательно появляются разряды ранее записанного кода, соответствующие разрядам повторного кода, которые в данный момент записываются в младший разряд регистра. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

16 производит сравнение каждого разряда повторного кода коррекции с соответствующим разрядом ранее записанного кoдav В cjJfyMae их несовпадения на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 появляется , поступающая на вход R триггера 19 и вызывающая его обнуление под действием импульсов на входе синхронизации с дополнительного выхода преобразовате

. : /,; . . , ,/ ., ,,, ,

Одновременно с записью повторного кода коррё эдии в регистр 5 счетчик 8 подсчитывает число импульсов тактовой серии. т,€. число записанных в регистр 5 р азрядрв повторного кода коррекции. Как в регистр 5 записываются все разряды повторного кода на выходе деш 1фратора 9 появляется повторного кода1 на выходе дешифратора 9 появляется 1 . которая поступает на третий вход элементами 14, разрещая прохождение через него сигна лов, а также запускает формирователь 10. Последний выделяет на выХОДе второй после запуска имг1ульс из последовате льности импульсов, поступающих ка его второй вход с выхода Ьлока 2. Импульс с выхода Формирователя ЛО через элемент ИЛИ 15 поступает на вход R триггера 17 и сбрасывает его: О с выхода триггера 17 блокирует элементы И 12и 13. запрещая прохождение сигналов с входа Код коррекции устройства на вход преобразователя 6.

Импульсе выхода формирователя 10 поступает также на первый вход элемента И 14. на третьем входе которого присутствует сигнал 1 с выхода дешифратора 9, а на второй вход поступает сигнал свыхода триггера 19. Если все разряды первого и повторного кода коррекции совпадают, те. код коррекции передан и записан в регистр 5 без искажений, состояние триггера 19 при записи повторного кода коррекции не изменяется и на его выходе поддерживается сигнал 1. П ри этом импул ьс ев ыхода формирователя 10 через элемент И 14 проходит на контрольный выход устройства, свидетельствуя о том. что код коррекции записан верно и коррекция шкалы времени состоится. Если хотя бы один из разрядов первого и повторного кодов коррекции не совпадают, то триггер 19 устанавливается в нулевое состояние. При этом элемент И 14 остается закрытым и импульс с выхода фор мирователя 10 не проходит на контрольный выход устройства. Отсутствие импульса на контрольном выходе устройства свидетельствует о том. что код коррекции записан в регистр 5 с искажениями, коррекция шкалы времени не состоится, требуется повторение записи.

В случае записи кода коррекции без искажений импульс с выхода формирователя 10 через элемент И 14 проходит на вход предварительной записи 4 и на второй вход

формирователя 11. При этом по переднему фронту этого импульса двоичный код величины коррекции из старших разрядов регистра 5. кроме последнего (дополнительного), записывается в счетчик 4. На выходе счетчика 4 появляется сигнал Г, который поступает на первый вход формирователя 11. разреШая формирование На его выходе сигнала управления. Сигнал управления в виде 1 появляется на выходе

формирователя 11 по заднему фронту импульса с выхода элемента И 14.

Сигнал управления с выхода формирователя 11 поступает на второй управляющий вход блока 2 и изменяет его

коэффициент деления на Ktl в зависимости от знака коррекции, поступающего на первый управляющий вход блока 2 с выхода младшего разряда регистра 5. Изменение коэффициента деления блока 2 приводит к

сдвигу шкалы времени, формируемой делителем 3.:

Сигнал управления поступает также на второй вход элемента И 7. При этом последний начинает пропускать импульсы с выхода блока 2 на вход вычитания счетчика 4. Код. эаписанный в счетчик 4, начинает считываться. По окончании считывания, когда счетчик4 обнуляется, на его выходе появляется О, который возвращает формирователь 11 в исходное состояние. Сигнал О с выхода формирователя 11 восстанавливает исходный коэффициент деления блока 2 и запрещает прохождение сигналов через элемент И 7 на вход вычитания счетчика 4. На этом коррекция заканчивается.

На выходе делителя 3 формируются импульсы с частотой 1 /60 Гц (минутные метки), которые поступают через элемент ИЛИ 15 на вход R триггера 17. Это обеспечивает

периодическую установку триггера 17 в нулевое состояние, что обеспечивает закрытие элементов И 12 и 13 (закрытие входа Код коррекции) в случае, если импульс на вход Ввод коррекции подан, а код коррекции по какой-либо причине не может быть передан или триггер 17 установлен в единичное состояние под воздействием помех на входе Ввод коррекции. Такое построение устройства ограничивает момент

проведения коррекции, которая должна проводиться предпочтительно сразу после формирования минутной метки на выходе делителя 3, При этом высокая частота передачи кода коррекции (например, 100 кГц) и высокая частота считывания кода (например, 1 МГц или 100 кГц) обеспечивают окончание коррекции задолго до следующей минутной метки.

Величина сдвига шкалы времени Д t ± N Т. где N - величина коррекции; Т -период повторения импульсов генератора 1.

Повышение помехоустойчивости предлагаемого устройства достигается за счет обеспечения возможности приема повторного кода коррекции с контролем правильности приема путем поразрядного сравнения первого и повторного (дублирующего) кодов коррекции. В случае полного совпадения первого и повторного кодов коррекция шкалы времени проводится, а на контрольном выходе устройства формируется сигнал, свидетел ствующий о лравильности приема кода коррекции и о проведении коррекции. Если хотя бы один из разрядов повторного кода не совпадает с соответствующим разрядом первого кода, то на контрольном выходе устройства сигнал отсутствует, что свидетельствует об искажении кода коррекции и необходимости повторения коррекции. При этом сдвиг шкалы времени, формируемой усилителем частоты, не производится.

Повышение помехоустойчивости предлагаемого устройства обеспечивается также тем, что в исходном состоянии вход Код коррекции устройства закрыт и открывается только во время проведения коррекции от момента подачи сигнала на вход Ввод коррекции до окончания записи кода коррекции. Это препятствует записи в устройство ложного кода коррекции (помех) и исключает возможность проведения несанкционированной коррекции. Кроме того, в случае ошибочной подачи сигнала на вход Ввод коррекции устройства, в случае воздействия помех, открывающих вход Ввод коррекции, или в том случае, когда при коррекции код коррекции по какой-либо причине не может быть передан на устройство, вход Код коррекции остается открытым только в течение времени до первой минутной отметки, формируемой делителем частоты, после чего закрывается, что также повышает помехоустойчивость устройства.

Формула изобретения

Устройство для коррекции шкалы времени, содержащее генератор, фазосдвигающий блок и делитель частоты, которые соединены последовательно, реверсивный счетчик, регистр сдвига, преобразователь кода коррекции, элемент И, счетчик, дешифратор и формирователь одиночных импульсов, которые соединены последовательно, а также формирователь сигнала управления, выход элемента И подключен к входу вычитания реверсивного счетчика, выход которого соединен с первым входом формирователя сигнала управления, выход младшего разряда регистра сдвига подключен к пер5 вому управляющему входу фазосдвигающего блока, выход которого соединен с первым входом элемента И и с вторым входом формирователя одиночных импульсов, выход формирователя сигнала управления под0 ключен к второму управляющему входу фазосдвигающего блока и к второму входу элемента И, выходы старших разрядов регистра сдвига подключены к входам записи реверсивного счетчика, информационный и 5 тактовый выходы преобразователя кода подключены к соответствующим входам регистра сдвига, тактовый выход преобразователя кода коррекции подключен к счетному входу счетчика, отличающее0 с я тем, что, с целью повышения помехоустойчивости, в него введены три дополнительных элемента И, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и три триггера, при этом ггервые входы первого и второго допол5 нительных элементов И являются входом сигнала Код коррекции, вторые входы подключены к выходу первого триггера, а выходы подключены соответственно к первому и второму входам преобразователя кода кор0 рекции, выход формирователя одиночных импульсов через третий дополнительный Элемент И соединен с входом предварительной Записи реверсивного счетчика и с вторым входом формирователя сигнала уп5 равления, а также подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом делителя частоты, выход дополнительного старшего разряда регистра сдвига подключен к входу 0 синхронизации второго триггера, выход младшего разряда и выход дополнительного старшего разряда регистра сдвига через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к первому входу установки третьего триг5 гера, второй вход установки которого соединен с выходом второго триггера и с входом установки счетчика, дополнительный выход преобразователя.кода коррекции подключен к входу синхронизации третьего 0 триггера, выход которого подключен к второму входу третьего дополнительного элемента И, первый вход установки первого триггера является входом сигнала Ввод коррекции, выход дешифратора подключен к третьему 5 входу третьего дополнительного элемента И, вход установки второго триггера и вход установки регистра сдвига соединены с первым входом установки первого триггера, второй вход установки которого подключен к выходу элемента ИЛИ.

Фи2.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1413590A2 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости. Устройство содержит генератор 1. фазосдвигающий блок 2, делитель 3 частоты, реверсивный счетчик 4, регистр 5 сдвига, преобразователь 6 кода коррекции, элемент И 7, счетчик 8, дешифратор 9, формирователь 10 одиночных импульсов, формирователь 11 сигнала управления. В устройство введены три дополнительных элемента И 12-14, элемент ИЛИ 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, три триггера 17- 19, позволяющие обеспечить прием повторного кода коррекции. Устройство может найти применение в системах синхронизации, синхронизирующих устройствах для коррекции шкалы времени. 2 ил.сл

| Устройство для коррекции шкалы времени | 1984 |

|

SU1185307A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-01-30—Публикация

1990-04-27—Подача