Известны устройства для согласования входных цепей ЭВМ с выходными цепями управляемых установок, содержащие две групцы схем разрешения, входы первой из которых соединены с передающими кодовыми шинами управляемой установки, и дешифратор адресов исполнительных устройств. Вход управления последнего подключен через схему формирования к выходам ЭВМ. Такие устройства не обладают достаточной универсальностью.

Предлагаемое устройство отличается тем, что оно содержит буферный регистр, выходы которого соедииены с приемными кодовыми шинами управляемой установки, а входы подключены к выходам второй группы схем разрешения, и блок Переключателей информации. Выходы и входы последнего соединены соответственно с приемными и передающими кодовыми шинами ЭВМ и с входами и выходами второй и первой групп схем разрешения. Кроме того, устройство содержит блок переключателей адресов схем разрешения, выходами присоединенный к управляющим входам схем разрешения; дешифратор адресов, входы и выходы которого соединены соответственно с кодовыми шинами адреса ЭВМ, с выходом схемы формирования и с входами блока переключателей адресов схем разрешения, а также блок переключателей кодовых

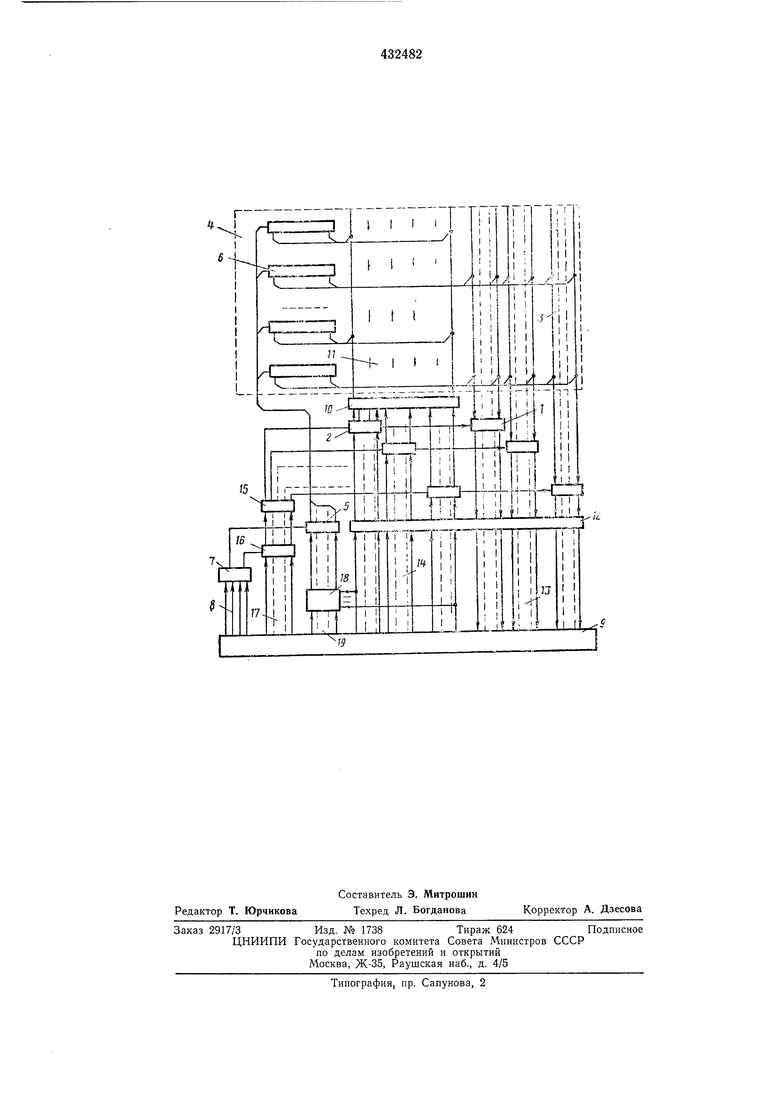

щнн адреса. Одна группа входов блока переключателей кодовых шин адреса подключена к передающим кодовым щинам адреса ЭВМ, другая - к передающим кодовым шинам ЭВМ, а выходы -соединены с входами дешифратора адресов исполнительных устройств. Это позволяет повысить универсальность устройства. На чертеже показана функциональная

блок-схема предлагаемого устройства.

Устройство содержит две группы схем 1 и 2 разрешения, входы первой из которых соединены с передающими кодовыми щинами 3 управляемой установки 4, и дешифратор 5 адресов исполнительных устройств 6. Вход управления дешифратора 5 подключен через схему 7 формирования к выходам 8 схемы сигналов сопровождения информации ЭВМ 9. Выходы буферного регистра 10 соединены с

приемными кодовыми шинами И установки 4, а входы подключены к выходам схем 2 разрешения. Выходы и входы блока 12 переключателей информации соединены соответственно с приемными 13 и передающими 14 кодовыми щинами ЭВМ и с входами и выходами схем 2 и 1 разрешения. Выходы блока 15 переключателей адресов схем разрешения присоединены к управляющим входам схем разрешения. Входы и выходы дешифратора 16

адресов схем разрешения соединены соответственло с кодовыми шинами 17 адреса ЭВМ, с выходом схемы 7 и с входами блока 15. Кроме того, устройство имеет блок 18 переключателей кодовых шин 19 адреса, одна группа ьходов которого подключена к передающим кодовым шинам 19 адреса ЭВМ, другая - к передающим кодовым шинам 14 ЭВМ, а выходы соединены с входами дешифратора 5. Устройство подключено к управляемой технологической установке 4 и к ЭВМ 9. Для приема выбран ряд ЭВМ 9, имеющий 8, 12, 16, 20 и т. д. разрядов выходных передающих 14 и приемных 13 кодовых шин числа. Программа работы управляемой от ЭВМ технологической установки или измерительной станции системы для контроля электрических параметров электронных схем состоит из командных, адресных, информационных слов и сигналов сопровождения, тактирующих передачу из ЭВМ или прием в ЭВМ информации. Командные слова поступают с ЭВМ по шипам 17 на дешифратор 16, который расшифровывает код командного Слова. Выходной сигнал дешифратора 16 подготавливает к работе определенные узлы устройства. Адресные слова, несущие код адреса исполнительного устройства 6, через блок 18 переключателей с передающих кодовых шин ЭВМ поступают на дешифратор 5 исполнительных устройств установки. Информационные слова, содержащие информацию о работе исполнительных устройств, для первых восьми разрядов поступают непосредственно с передающих кодовых шин 14 ЭВМ па входы схем 2 разрешения (первой в ряду выбрана ЭВМ, имеющая восемь приемных и передающих кодовых шин). Второе Еосьмиразрядцое информационное слово через блок 12 переключателей подается на входы соответствующих .схем 2 разрешения и т. д. Соединения в блоках 12, 15 и 18 переключателей выполнены так, чтобы в зависимости от положения переключателей можно было в случае применения ЭВМ с числом кодовых шин 13 и 14 меньшим, чем число кодовых шин 3 и 11 установки, комбинируя подключением входов или выходов схем разрешения к передающим 14 или приемным 13 кодовым шинам, за несколько тактов занесения информации записать ее во все разряды буферного регистра 10 и далее в исполнительные устройства пли в ЭВМ, т. е. в случае применения ЭВМ с восемью разрядами передающих 14 и приемных 13 кодовых шин информацию можно занести в три такта, в случае применения ЭВМ с двенадцатью или шестнадцатью кодовыми шинами 13 и 14 - за два такта и т. д. Предмет изобретения Устройство для согласования входных цепей электронных вычислительных машин (ЭВМ) с выходными цепями унравляемых установок, содержащее две группы схем разрешения, входы первой из которых соединены с передающими кодовыми шинами управляемой установки, и дешифратор адресов исполнительных устройств, вход управления которого подключен через схему формирования к выходам ЭВМ, отличающееся тем, что, с целью повышения универсальности, оно содержит буферный регистр, выходы которого соединены с приемными кодовыми шинами управляемой установки, а входы подключены к выходам второй группы схем разрешения, блок переключателей информации, выходы и входы которого соединены соответственно с приемными и передающими кодовыми шинами ЭВМ и с входами и выходами второй и первой групп схем разрешения, блок переключателей адресов схем разрешения, выходы которого присоединены к управляющим входам схем разрешения, дешифратор адресов, входы и выходы которого соединены соответственно с кодовыми шинами адреса ЭВМ, с выходом схемы формирования и с входами блока переключателей адресов схем разрешения, а также блок переключателей кодовых шин адреса, одна группа входов которого подключена к передающим кодовым шинам адреса ЭВМ, другая - к передающим кодовым шинам ЭВМ, а выходы соединены с входами дешифратора адресов исполнительных устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения эвм с управляемыми объектами | 1978 |

|

SU733963A1 |

| Устройство для сопряжения вычислительной машины с объектами управления | 1979 |

|

SU1040482A1 |

| Устройство для программного сопряжения электронных вычислительных машин | 1976 |

|

SU641434A1 |

| Устройство для сопряжения электронной вычислительной машины с управляемыми объектами | 1982 |

|

SU1043623A2 |

| Цифровое коммутационное устройство | 1985 |

|

SU1378088A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения электрон-НыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809145A1 |

| Устройство для сопряжения | 1980 |

|

SU903853A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

Авторы

Даты

1974-06-15—Публикация

1971-06-13—Подача