СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство управления накопителями на магнитных дисках | 1988 |

|

SU1532956A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

Изобретение относится к цифровой вычислительной технике, в частности к локальным вычислительным сетям ЭВМ Цель изобретения - повышение производительности за счет реализации прямого доступа к памяти ЭВМ, а также упрощенно станции за счет исключения некоторых блоков Станция локальной сети содержит блок сопряжения с каналом связи, блок буферной памяти, первый и второй контроллеры прямого доступа блок сопряжения с ЭВМ, связанные внутренней шиной данных и внутренней шиной адреса, блок управления прямым доступом, приемопередатчик буфер Новым в станции является введение контроллера прямого доступа, приемопередатчика, буфера и блока управления прямым доступом, новое выполнение блока сопряжения с ЭВМ, а также связи названных блоков с другими блоками станции 1 з п ф-лы, 12 ил

Изобретение относится к цифровой вычислительной технике, может быть использовано для организации взаимодействия между компонентами сетей и систем

Целью изобретения является повышение производительности и упрощение станции локальной сети за счет введения блоков и связей, позволяющих реализовать режим прямого доступа к памяти ЭВМ, а также за счет реализации станции без микропроцессора.

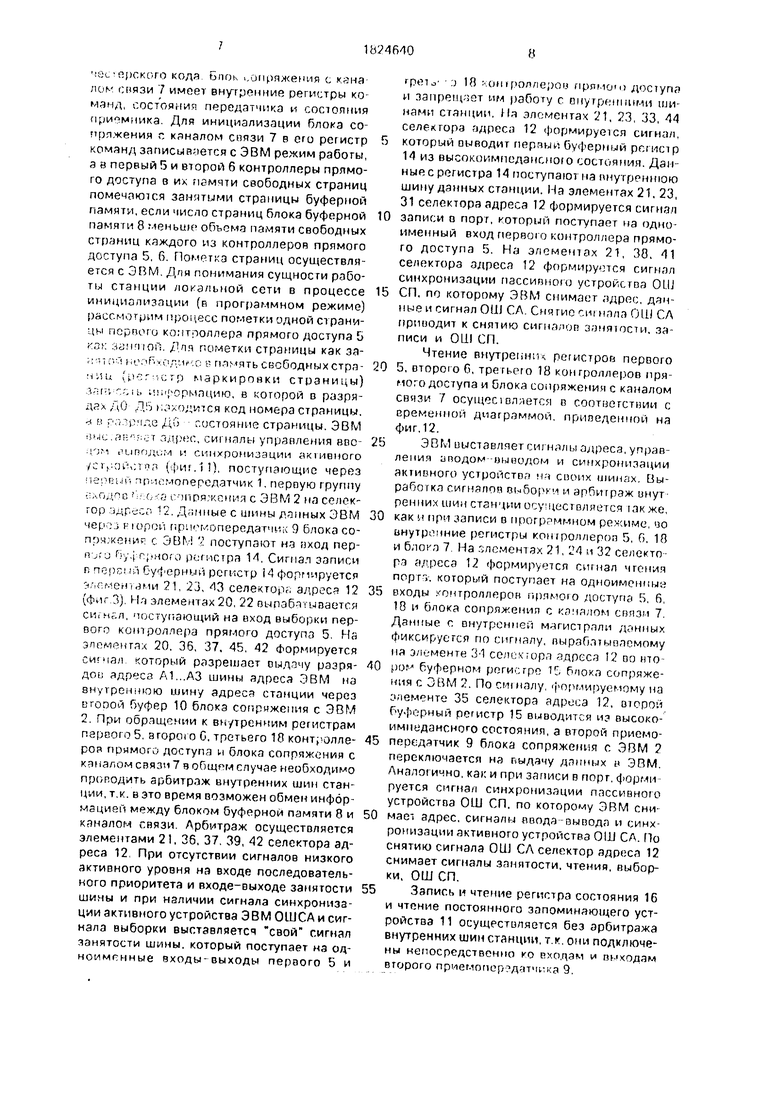

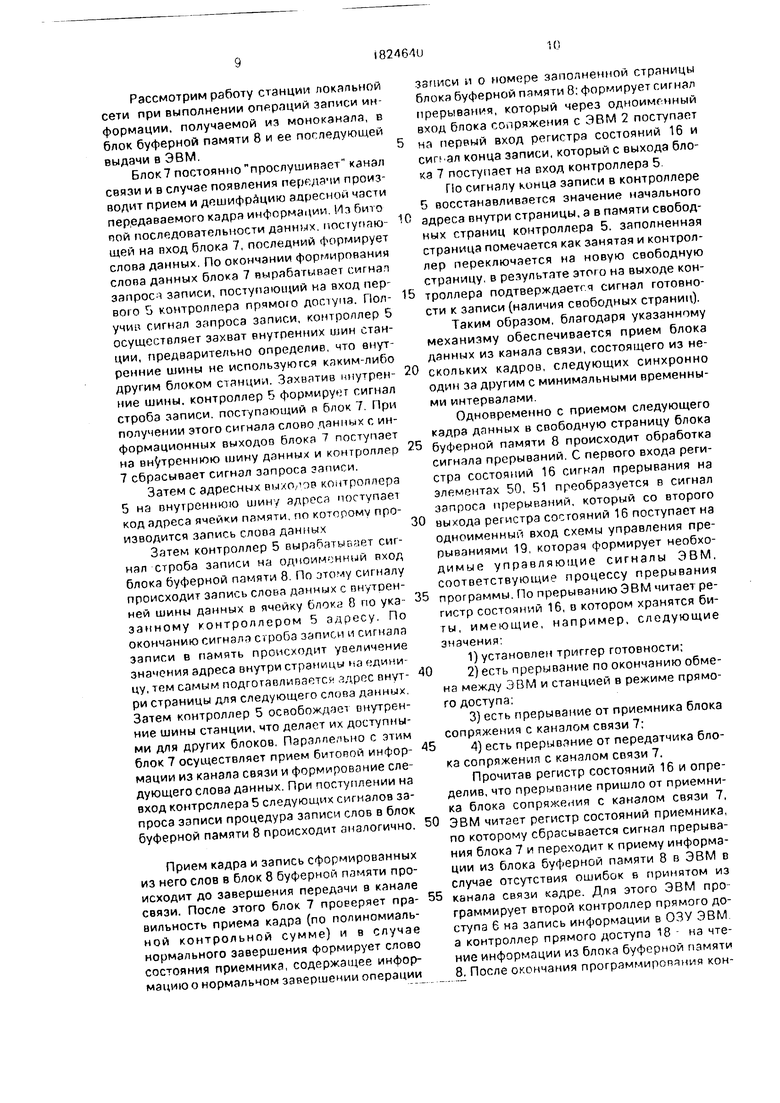

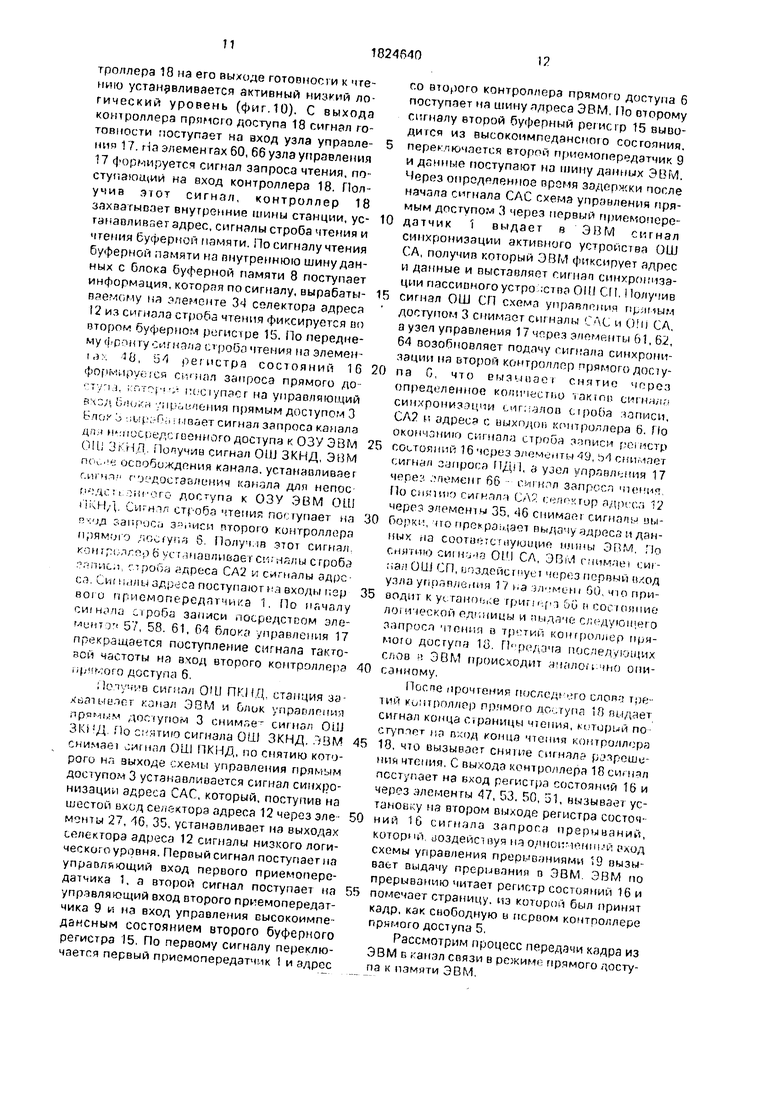

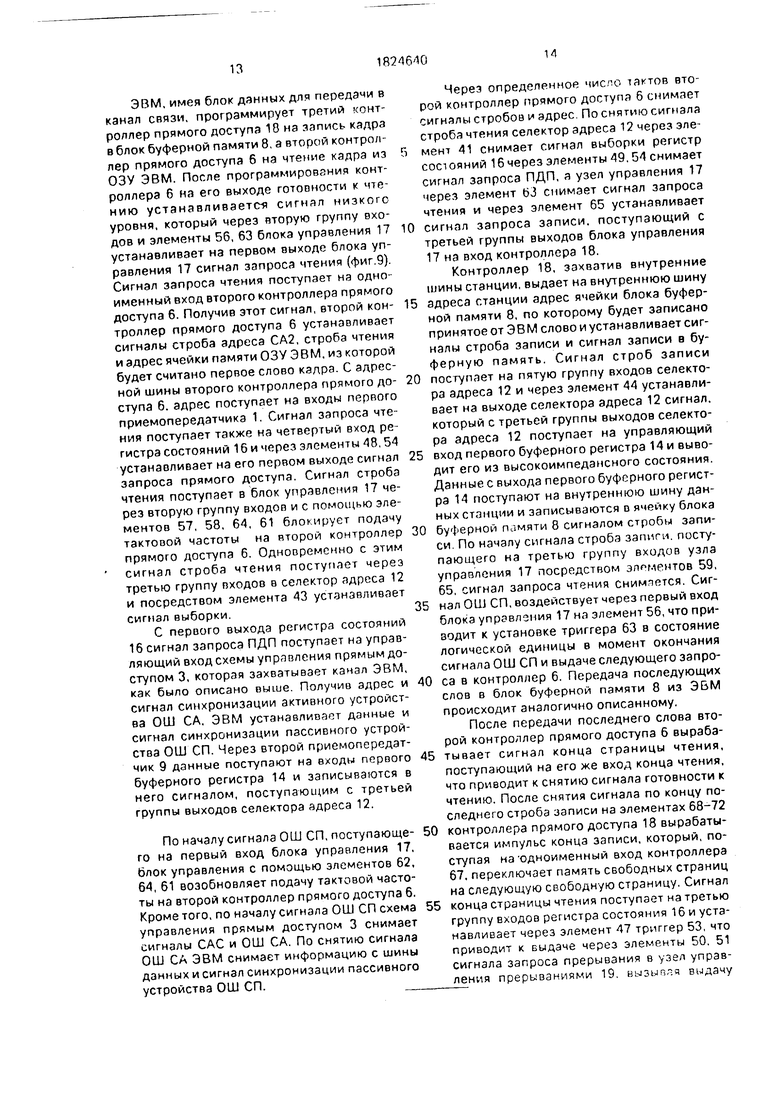

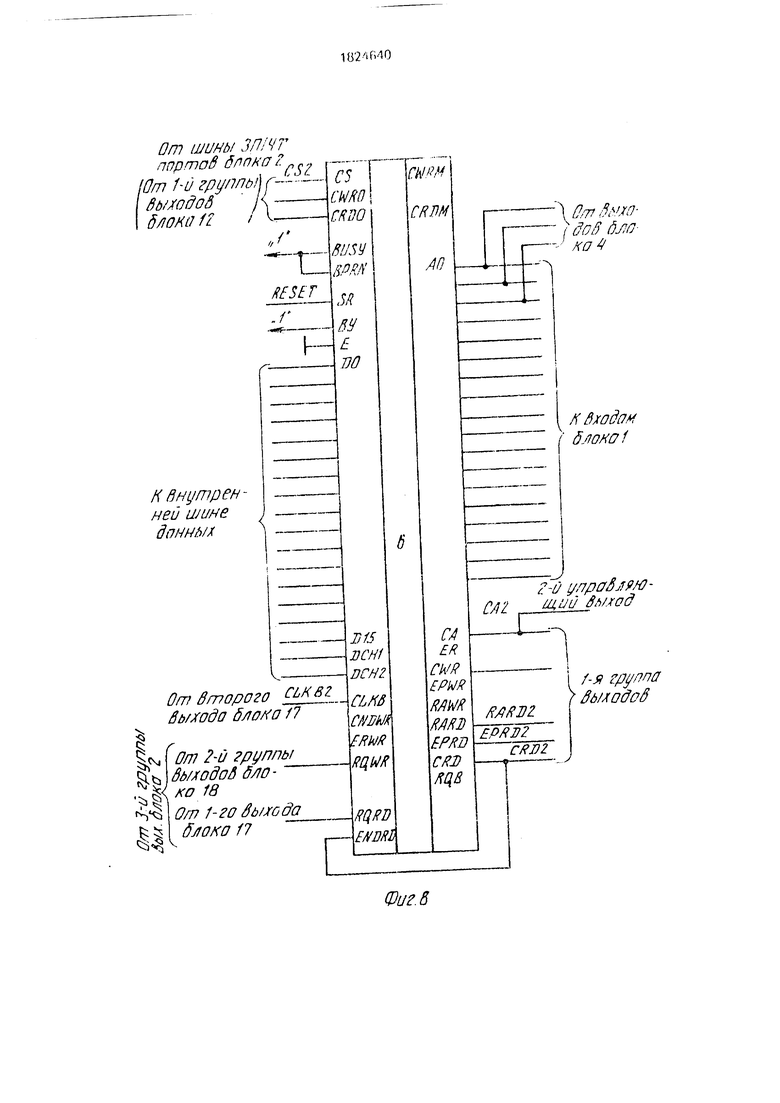

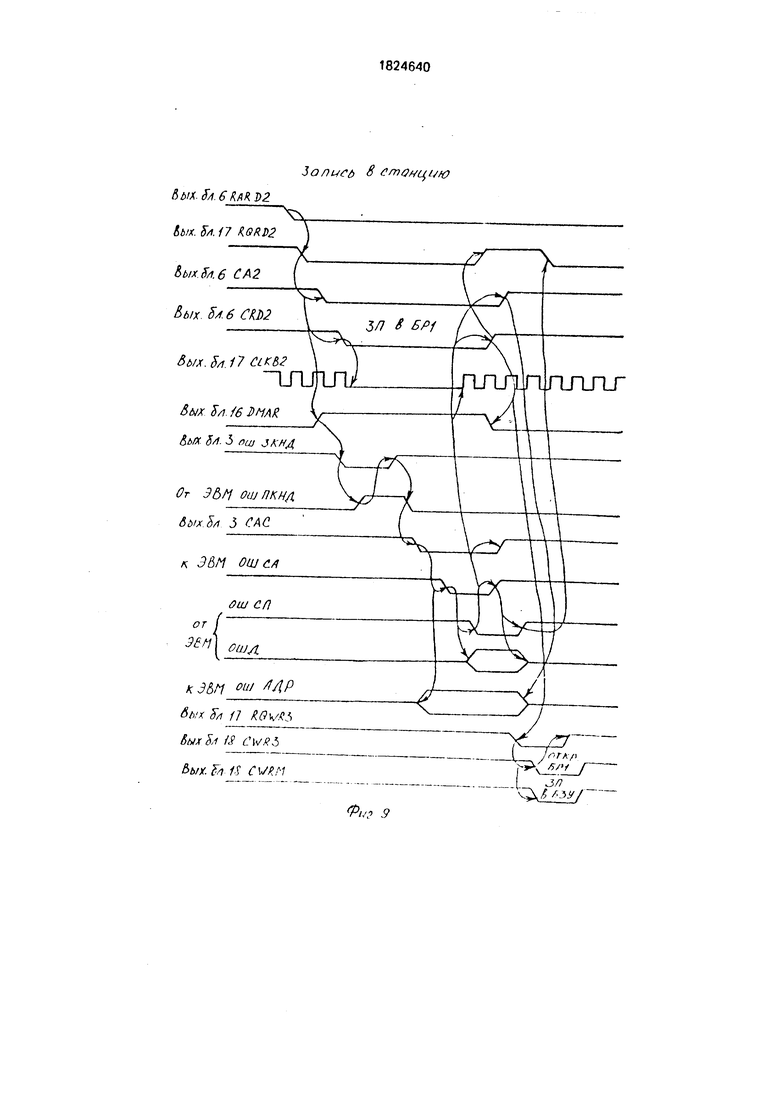

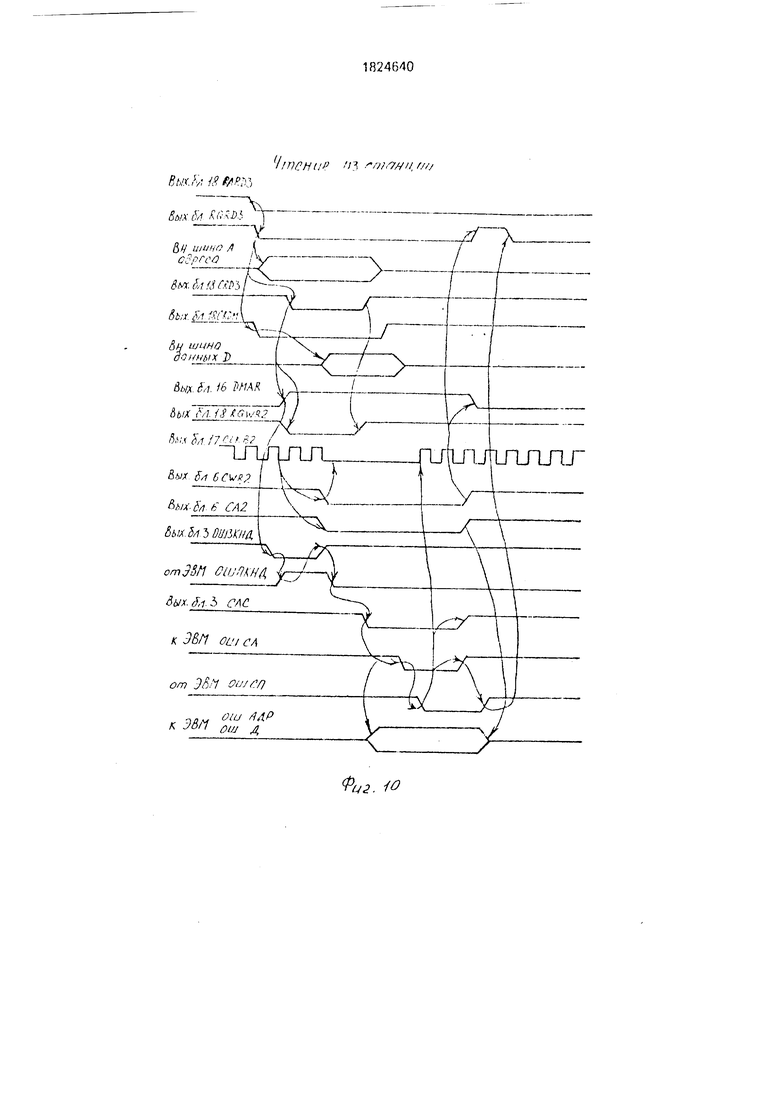

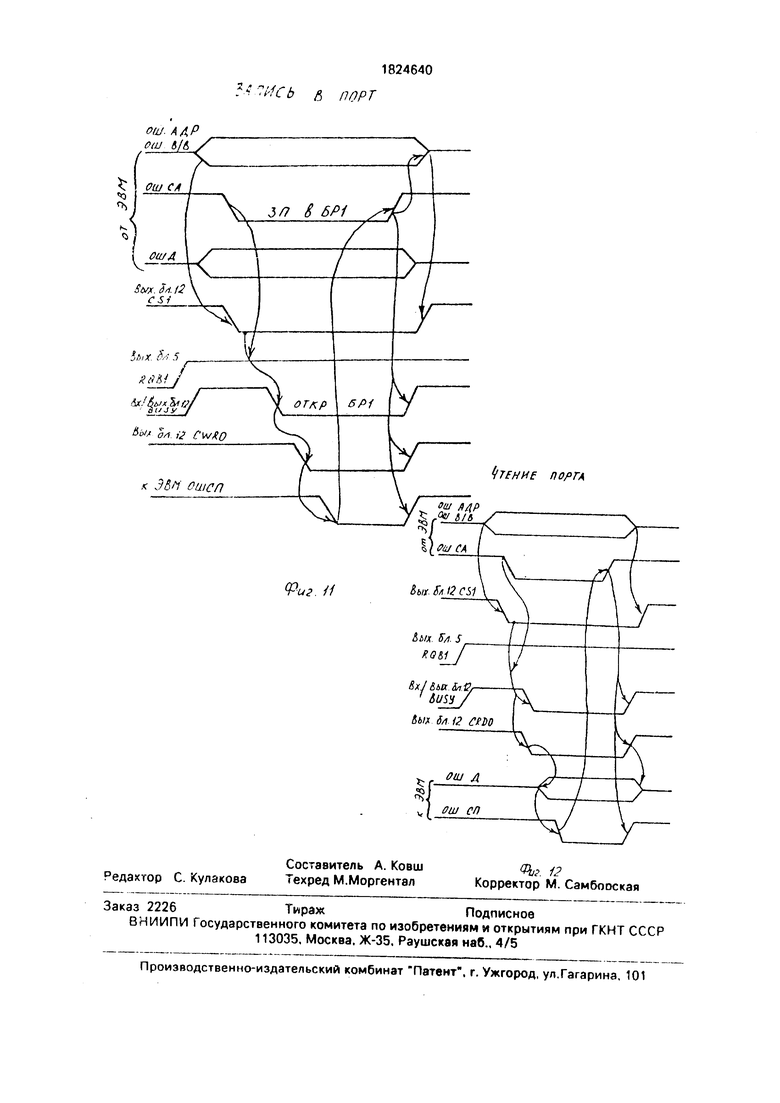

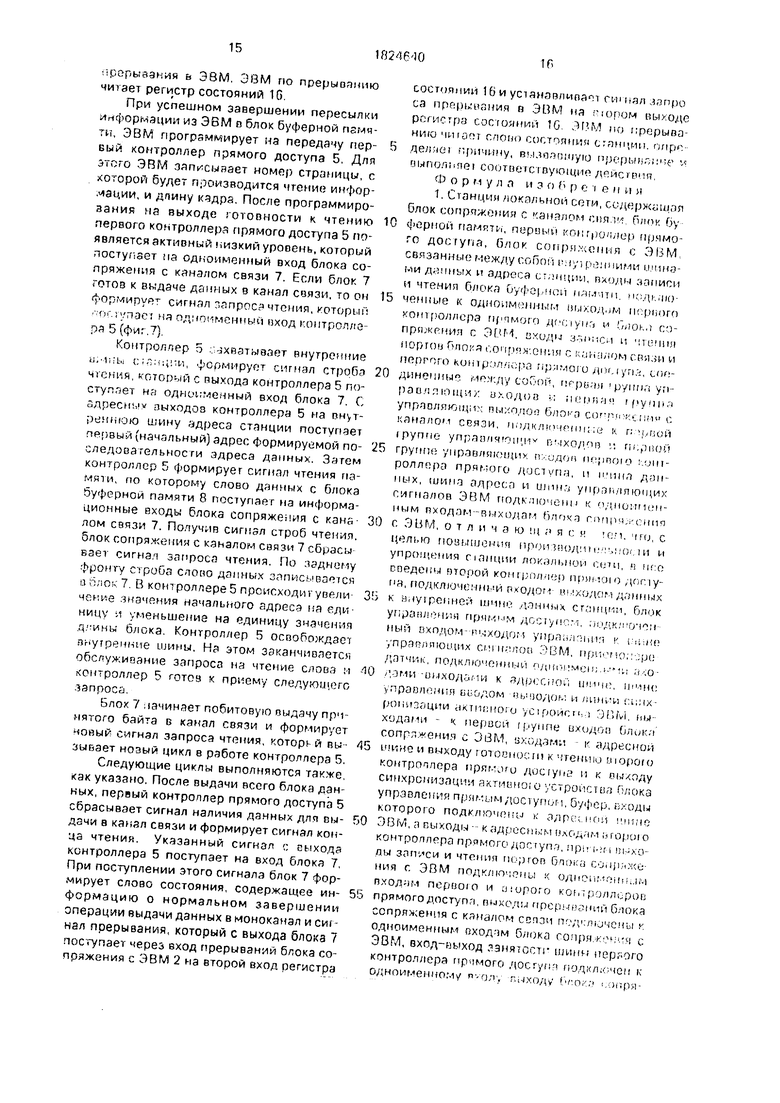

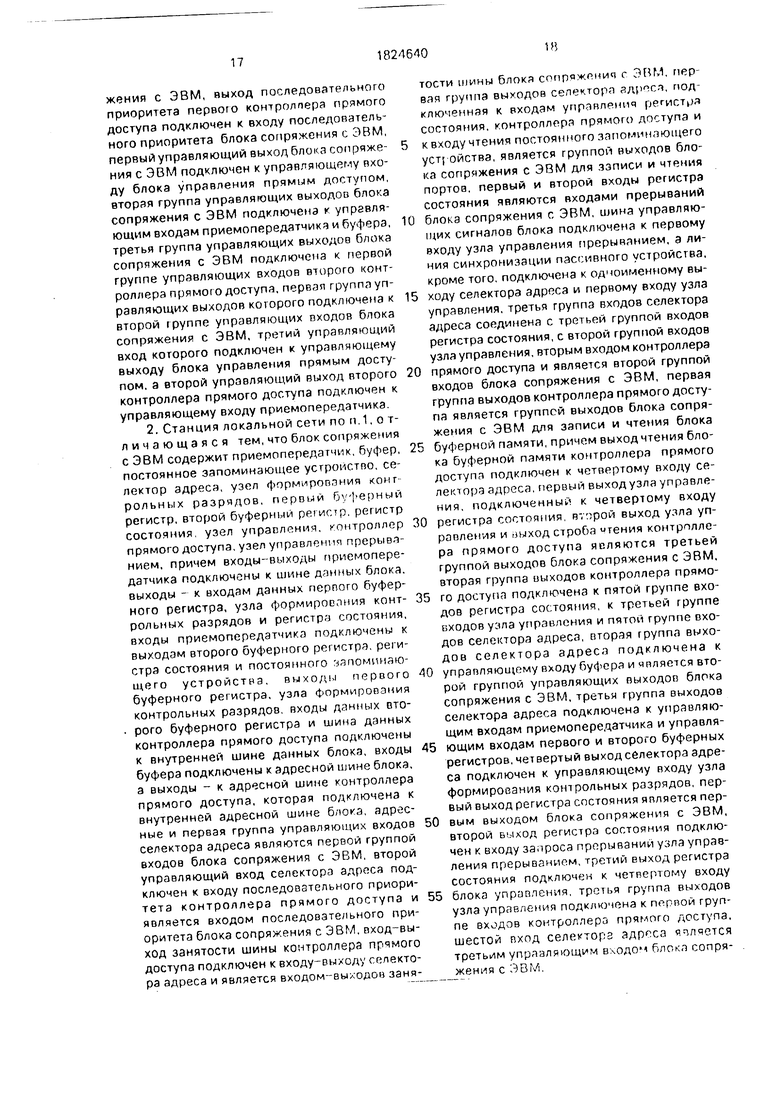

На фиг.1 представлена структурная схема станции локальной сети; на фиг 2 - структурная схема блока сопряжения с ЭВМ; на фиг.3-6 - примеры выполнения функциональных схем селектора адреса, регистра состояния, блока управления третьего контроллера прямого доступа, входящих в блок сопряжения с ЭВМ; на фиг.7,8 - функциональные схемы первого и второго контроллеров прямого доступа, на фиг.9 - временная диаграмма передачи информации из ЭВМ в блок буферной памяти в режиме прямого доступа, на фиг 10 - временная диаграмма приема информации в ЭВМ из блока буферной памяти в прямого доступа, на фиг.11 и 12 - временные диаграммы соответственно записи i« чтения в программном режиме.

Станция локальной сети (фиг,1) содержит первый приемопередатчик 1, блок сопряжения с ЭВМ 2, блок управления прямым доступом 3, буфер 4, первый контроллер прямого доступа 5, второй контроллер прямого доступа 6, блок сопряжения с каналом связи 7, блок буферной памяти 8 Блок связи с ЭВМ 2, первый контроллер прямого доступа 5, блок сопряжения с каналом связи 7, блок буферной памяти 8 и ото- рой контроллер прямого доступа 6

со ю

О Јк О

обьединены внутренней шиной данных, а первые четыре блока, кроме того, и внутренней шиной адреса. Входы-выходы первого приемопередатчика 1 подключены к адресной шине, шине управления вводом-выводом и цепи синхронизации активного устройства ЭВМ, выходы - к первой группе входов блока сопряжения с ЭВМ 2, входы - к адресной шине и цепи готовности к чтению второго контроллера прямого доступа 6 и к выходу синхронизации активного устройства схемы управления прямым доступом 3, а управляющий вход - ко второму управляющему пыходу второго контроллера прямого доступа 6. Шина данных, шина адреса ЭВМ подключена к блоку сопряжения с ЭВМ 2, шина управляющих сигналов ЭВМ подключена к блоку сопряжения с ЭВМ 2, схеме управления прямым доступом 3, уп- рапляющий оход которой подключен к первому выходу блока сопряжения с ЭВМ 2, вторая группа выходов которого подключена к управляющим входам первого приемопередатчика и первого буфера 4, третья группа выходов - к первой группе входов оторого контроллера прямого доступа G, выходы записи и чтения портов - к одноиме- ненным входам первого 5 и второго 6 контроллеров прямого доступа и блока сопряжения с каналом связи 7, выходы записи и чтения буферной памяти обьединены с одноименными выходами первого контроллера прямого доступа 5 и подключены к од- HenMCiifihiM входам блока буферной памяти 8, вход-выход занятости шины ко входу - выходу занятости шины первого контроллера прямого доступа 5. Вторая группа входов блока сопряжения с ЭВМ 2 подключена к первой группе выходов второго контроллера прямого доступа 6, входы прерываний - к выходам прерываний блока сопряжения с каналом связи 7, вход последовательного приоритета - к одноименным выходам первого контроллера прямого доступа 5. Первая группа управляющих входов и первая группа управляющих выходоэ блока сопряжения с каналом связи 7 подключены к первой группе управляющих выходов и первой группе управляющих входов первого контроллера прямого доступа 5.

Блок сопряжения с ЭВМ 2 содержит (фиг.2) второй приемопередатчик 9, буфер

10,постоянное запоминающее устройство

11,селектор адреса 12, схему формирования контрольных разрядов 13, первый и второй буферные регистры 14, 15, регистр состояния 16, узел управления 17, контроллер прямого доступа 18. узел управления прерыванием 19. Входы - выходы второго приемопередатчика 9 подключены к шине

данных ЭВМ, выходы - ко входам первого буферного регистра 14. узла формирования контрольных разрядов 13 и регистра состояния 16, оходы - к выходам второго буферного регистра 15, регистра состояния 16 и постоянного запоминающего устройства 11. Выходы первого буферного регистра 14, узла формирования контрольных разрядов 13, входы второго буферного регистра 15 и

шина данных контроллера прямого доступа 18 подключены к внутренней шине данных станции локальной сети. Входы буфера 15 подключены к адресной шипе ЭВМ, а выходы - к адресной шине контроллера прямого

5 доступа 18, которая подключена к внутренней адресной шине станции локальной сети. Адресные и первая группа упрзоляюа1их входов селектора адреса 12 подключены к выходам первого приемопередатчика 1 и яв0 ляюгся первой группой входов блока сопряжения с ЭВМ 2, оторой управляющий вход селектора адреса 12 подключен ко входу последовательного приоритета контроллера прямого доступа 18 и является входом

5 последовательного приоритета блока сопряжения с ЭВМ 2. Вход - выход занятости шины контроллера прямого доступа 18 подключен ко входу - выходу селектора адреса 12 и является входом - выходом занятости

0 шины блока сопряжения с ЭВМ 2. Первая группа выходов селектора адреса 12, подключенная ко входам регистра состояния 16, контроллера прямого доступа 18 и ко входу чтения постоянного запоминающего

5 устройства 11, является фуппой выходов блока сопряжения с ЭВМ 2 для записи и чтения портоо. Первый и второй входы регистра состояний 16 являются входами прерываний блока сопряжения с ЭВМ 2, шина

0 управляющих сигналов ЭВМ подключена к узлу управления прерывания 19, а цепь синхронизации пассивного устройства, кроме- того, подключена к одноименному выходу селектора адреса 12 и первому входу узла

5 управления 17, третья группа входов селектора здреса 12 соединена с третьей группой входов регистра состояния 16, со второй группой входов узла управления 17, вторым входом контроллера прямого доступа 18 и

0 является второй группой входов блока сопряжения с ЭВМ 2, первая группа выходов контроллера прямого доступа 18 является группой выходов блока сопряжения с ЭВМ 2 для записи и чтения блока буферной памя5 ти 8, причем выход чтения блока буферной памяти 8 подключен к четвертому входу селектора адреса 12. Первый выход узла управления 17. подключенный к четвертому входу регистра состояния 16. второй оыход узла управления 17 и выход строба чтения

контроллера прямого доступа 18 являются третьей группой выходов блока сопряжения с ЭВМ 2, вторая группа выходов контроллера прямого доступа 18 подключена к пятой группе входов регистра состояние 1C, к третьей группе входов узла управления 17 и пятой группе входов селектора адрес 12. второй выход селектора адреса 12 подключен к управляющему входу буфера 10 и яв ляется вторым управляющим выходом блока сопряжения с ЭВМ 2, третья группа выходов селекторов адреса 12 подключена к управляющим входом второго приемопередатчика 9 иуправпяющим входам первого 14 и второго 15 буферных регистров четвертый пыход селектора адреса 12 подключен к управляющему входу узла формирования контрольных разрядов 13, первый выход регистра состояний 12 является первым выходом блока сопряжения с ЭВМ 2, второй выход регистра состояния 16 подключен ко входу запроса прерываний узла управления прерываниями 19, третий выход регистра состояний 16 подключен к четвертому узла управления 17, третья группа выходов узла управления 17 подключена к первой группе входов контроллер. прпмого досгу- па 18.

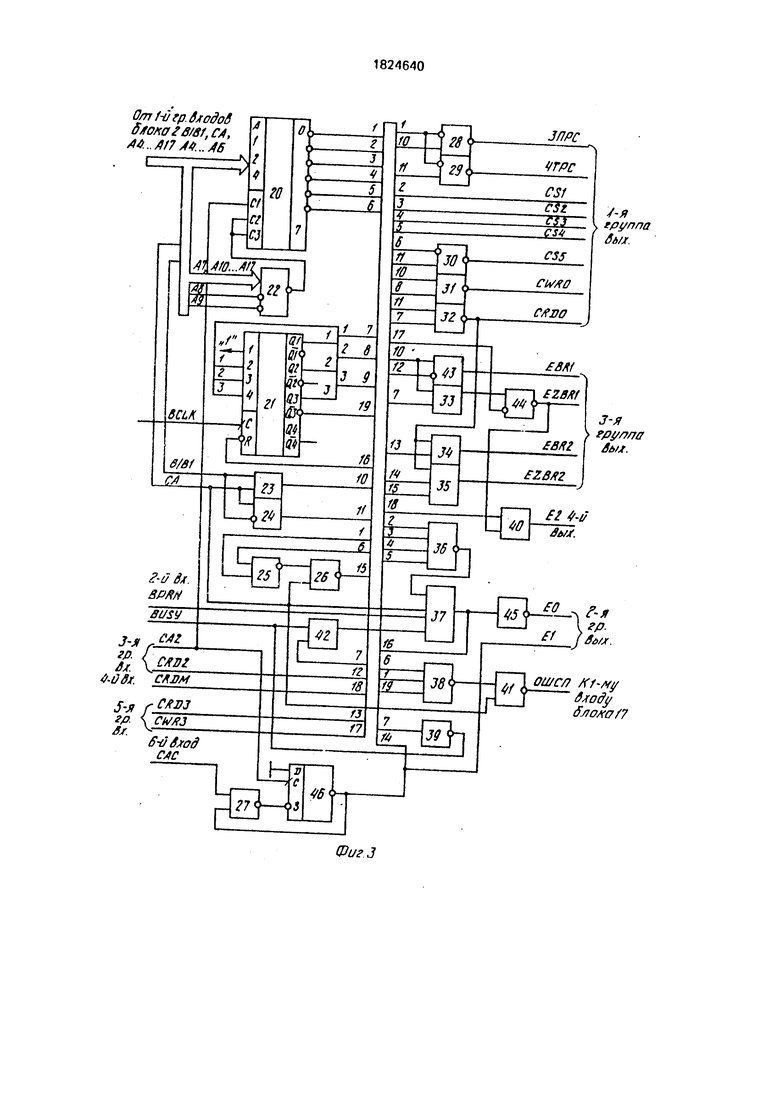

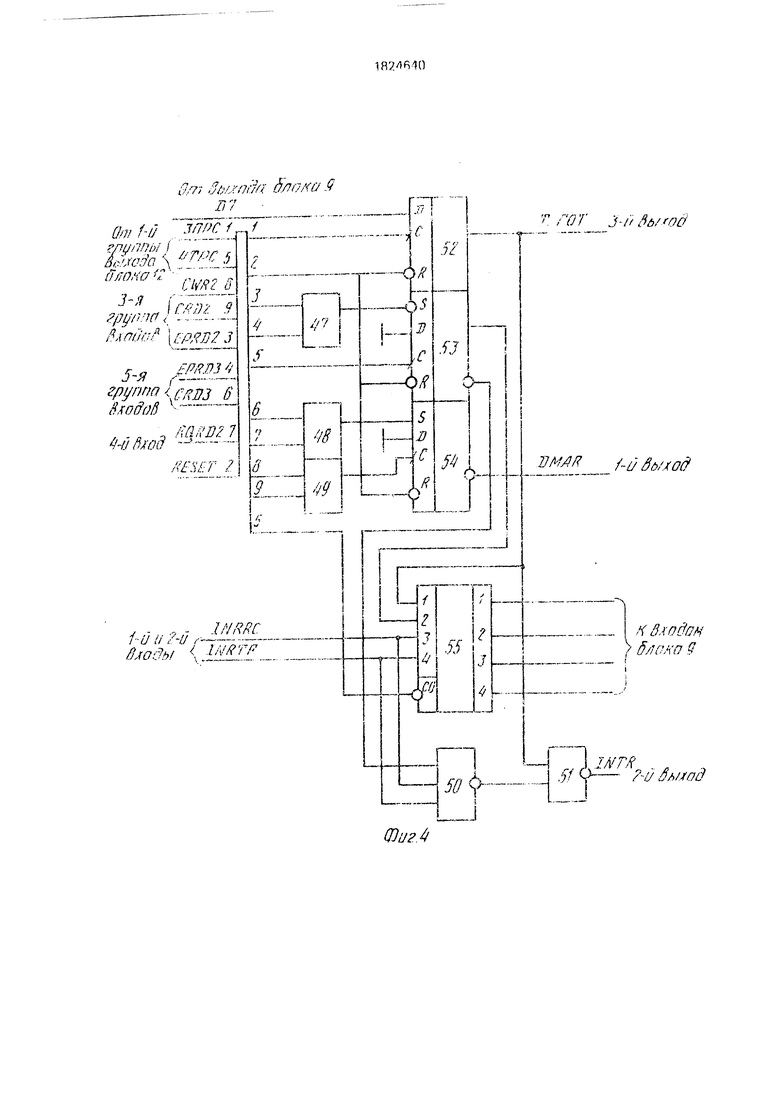

Селектор адреса 12 (фиг 1) блоклсопряжения с ЭВМ 2 содержи г дешифратор 20. сдвиговый регистр 21, элементы И 22 41, элементы ИЛИ 41...45, триггер 46

Регистр состояний (фиг 4) содержит эпе- менты И 47...51. триггеры 52...54, передатчик 55.

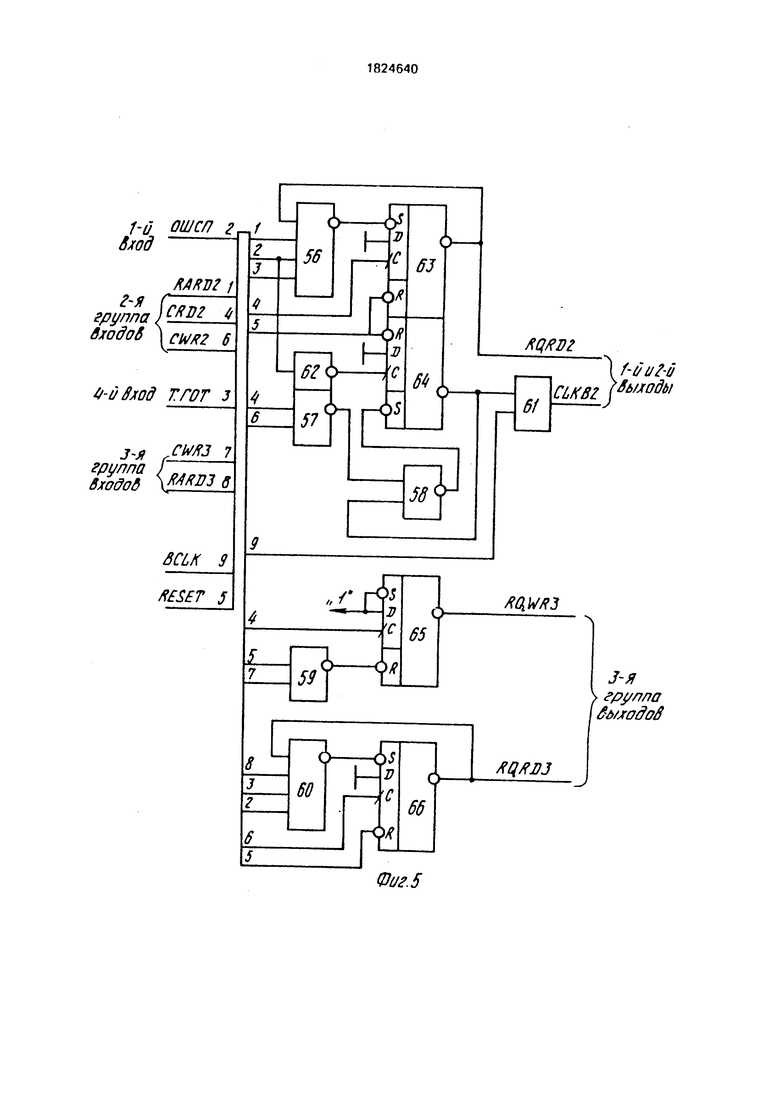

Блок управления (фиг,5) содержит зпе- менты И 56..61, элемент ИЛИ 62, триггеры 63-66.

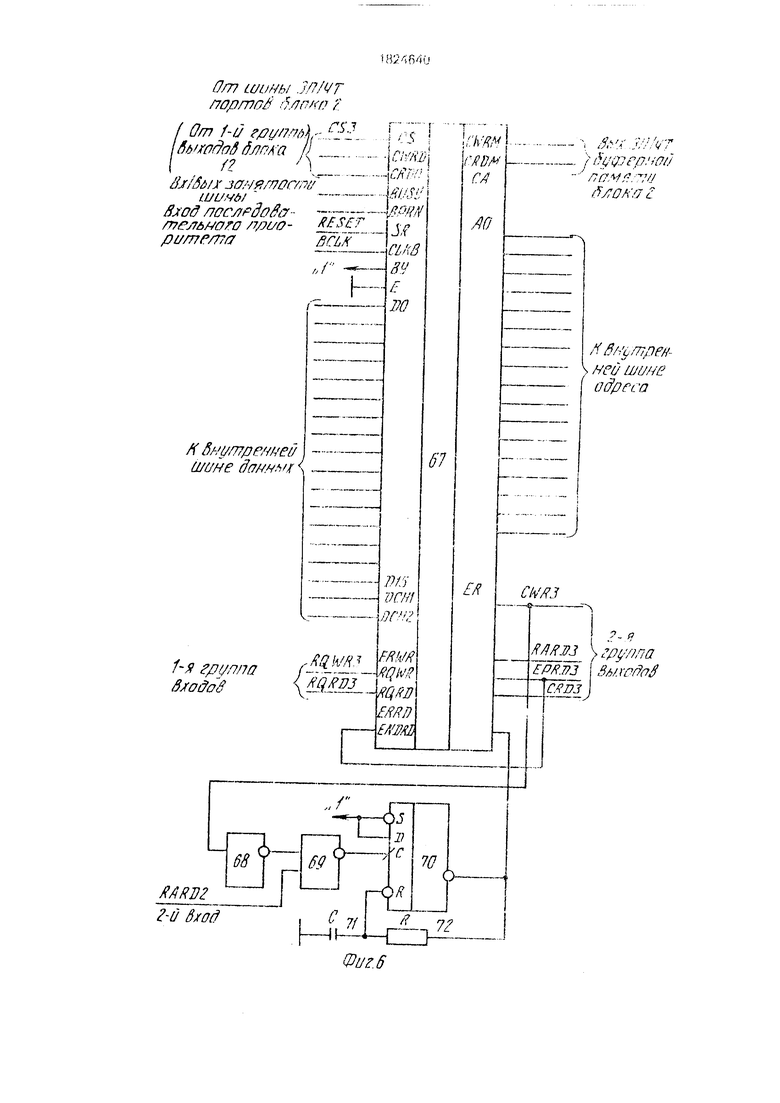

Контроллер прямого доступа 18 (фиг.6) содержит собственно контроллер прямого доступа 67, инвертор 68, элемент И 69, триггер 70, конденсатор 71, резистор 72

Приемопередатчик 1 предназначен для выдачи адреса из ЭВМ на станцию локальной сети в программном режиме работы ЭВМ и для приема адреса ЭВМ от станции в режиме прямого доступа к памяти ЭВМ.

Блок сопряжения с ЭВМ 2 обеспечивает логическое, электрическое и ргпъемное сопряжение станции с интерфейсом Общая шина.

Блок управления прямым доступом 3 формирует сигналы управления каналом ЭВМ в режиме прямого доступа к памяти ЭВМ.

Буфер 4 предназначен для подключения адресной шины ЭВМ к адресной шине второго контроллера прямого доступа 6 при обращении к внутренним регистрам второго контроллера прямого доступа б.

Первый контролпер прямот доступа 5 предназначен для управления записью информации, получаемой из моноканала через блок сопряжения с. каналом связи 7, в блок буферной памяти 8, а также для управления чтением данных из блока буферной памяти 8 для последующей их выдачи через блок связи с каналом связи 7 в моноканал.

Второй контроллер прямого доступа 6

0 осуществляет управление доступом к памяти ЭВМ.

Блок связи с каналом связи 7 предназначен для приема кэдра данных, поступающего из канала связи, и выдачу

5 сформированного кадра данных в канал.

Блок буферной памяти 8 служит для хранения данных, получаемых из канала связи (моноканала) или от ЭВМ.

Станция локальной сети работает сле0 дующим образом.

При включении питания или при подаче сигнала сброса с ЭВМ производится установка всех блоков станции в исходное состояние. По сигналу начальной установки

5 первый 5 и второй 6 контроллеры прямого доступа, а также контроллер прямого доступа 18, входящий в блок опряженич с, каналом ЭВМ 2, устонаклирартся в такое состояние, при котором на их выходах го0 точности к записи устянавпивгэечся активный высокий логический уровень. Триггер готовности52 регистра состояния 16, входящего в блок сопряжения с ЭВМ 2, устанавливается в состояние логического нуля на

5 его прямом выходе, блокируя подачу запросов записи и запросов чтения на третий контроллер прямого доступа 18 и запроса чтения на второй контроллер прямого доступа 6, а также выдачу сигнопа запроса преры0 ваний с выхода элемента И 49 регистра состояний 16 (второй выход регистра состояний 16) на вход запроса прерываний схемы управления прерываниями 19 блока сопряжения с ЭВМ 2.

5Перед началом работы производится

инициализация блока сопр жения с каналом связи 7, первого 5. второго 6 и третьего 18 контроллероа прямого доступа. Для выполнения операции записи первый 5, вто0 рой б и третий 18 контроллепы прямого доступа имеют память свободных страниц, которая предназначена для хранения таблицы с номерами свободных и занятых стра ниц. Для выполнения операции чтения и

5 записи данных с помощью контроллеров прямого доступа 5, 6, 18, в них с ЭВМ записываются начальный адрес, включая номер страницы, и дойна массинь.

Блок сопряжения с каналом связи 7 содержит контроллер и преобразователь ман Gv. -ярского кода ьпок сопряжения L лом спязи 7 имеет внутренние регистры команд, состояния передатчика и состояния приемника Для инициализации блока сопряжения с каналом соязи 7 в его регистр команд записывается с ЭВМ режим работы, я в первый 5 и второй б контроллеры прямого доступа в их помчти свободных страниц помечаются занятыми страницы буферной памяти, если число страниц блока буферной памяти 8 меньше объема памяти свободных страниц каждого из контроллеров прямого доступа 5, G. ПОМРТКЭ страниц осуществляется с ЭВМ. Дня понимания сущности работы станции локальной сети в процессе инициализации (R программном режиме) рассмотрим процесс пометки одной страницы первого контроллера прямого доступа ; Gf. -idimmfi Для пометки страницы как за- ,; м .-, he. fi O/yvr У п л мять свободных стра- ч,ш ,,- -1,тр маркировки страницы)

V-Г ., i ь П. и СрМаЦИЮ, В КОГОрОЙ В рЭЗрЯдад ДО Д -j (.сходится код номера страницы. R n / vi.;o До состояние страницы. ЭВМ .ii, аг- ..т адрес, cm налы управления ввс- г;м иппдчм и синхронизации активного /oij.rbvtnri (иг.Н), поступающие через rj T..n-. тр и-мопередатчик 1. первую группу .,. с & о мтря кения с ЭВМ 2 населек- гор . 12. Д ;нные с тины данных ЭВМ чер ь Fiopon приемопередатчик 9 блока со- поч.кениг с ЭВМ поступают из нход пер- J f j i г;.но. о регистра 14. Сигнал записи г, перс) i i буферный регистр 14 формируется v.rMCHidMn 21, 23, 43 селекторг, адреса 12 (фиг 3J На элементах 20, 22 выпобл-ывается cniMf-л, поступающий на «ход выборки первого контроллера прямого доступа 5 На элементах 20. 36, 37, 45, 42 Формиоуется си нал который разрешает выдачу разрядов адреса А1...АЗ шины адреса ЭВМ на внутреннюю шину адреса станции через вгооой буфер 10 блока сопряжения с ЭВМ 2. При обращении к вь/тренним регистрам первого 5. агорою С. третьего 10 контроллеров прямого доступа и блока сопряжения с каналом связч 7 а общем случае необходимо прогюдить арбитраж внутренних шин станции, т.к. в это время возможен обмен информацией между блоком буферной памяти 8 и каналом связи Арбитраж осуществляется элементами 21, 36, 37. 39, 42 селектора адреса 12 При отсутствии сигналов низкого активного уровня на входе последовательного приоритета и входе-выходе занятости шины и при наличии сигнала синхронизации активного устройства ЭВМ ОШСА и сигнала выборки выставляется свой сигнал занятости шины, который поступает на од- ноимгнные входы-выходы первого 5 и

гретд ; 18 -отроллерои прямою доступа и запрещает им работу с пнутрениими шинами станции. Ия элементах 21, 23, 33, 44 селектора адреса 12 формируется сигнал,

который выводит первые буферный регистр 14 из высокоимпедэноного состояния. Данные с регистра 14 поступают на пну (рентою шину данных станции. На элементах 21, 23, 31 селектора адреса 12 формируется сигна/i

0 записи о пор г, который поступает на одноименный вход перяо о контроллера прямого доступа 5. На элементах 21, 30, 41 селектора адреса 12 формируется сигнал синхронизации пассивно и устройства OLIJ

5 СП, по которому ЭВМ снимает адрес, данные и сигнал ОШ СА Снятие cm нала ОШ СА прчоодит к снятию сигналов заняюсти. записи и ОШ СП.

Чтение внутренние регистров первого

0 5, второю Г), третьего 18 контроллеров прямого дос тупа и блока сопряжения с каналом связи 7 осущесюляется в соответствии с временной диаграммой, приведенной на фиг. 12.

5ЭВМ выставляет CHI нллы адреса, управления анодом выводом и синхронизации активного устройства ч-ч своих (линях. Выработка сигнапоп оыборь и арбитраж инут ренних шин стзнчииосуществляется также,

0 как 1 при записи в программном режиме, во внутренние регистры контроллеров 5, 0, 10 и блока 7 На элементах 21, 24 и 32 селекто гэ a/tpeca 12 формируется сигнал чтения nopn. который поступает на одноименный

5 входы контроллеров прямого доступа 5. 6, 18 и блока сопряжения с клчалом связи 7 Данные с внутренней магистрали донных Фиксируется по сигналу, тшрзОлтыолемому на элементе 34 сели ч-горл адреса 12 DO нто0 рог буферном регистре 1C, блока сопряжения с ЭВМ 2. По см)налу, формируемому на элементе 35 селектора адреса 12, отороп буферный регистр 15 выводится из высоко- имнедансного состояния, а второй приемо5 передатчик 9 блока сопряжения с ЭВМ 2 переключается на выдачу данных в ЭВМ. Анало( ично, как и при записи в порт, форми руется сигнал синхронизации пассивного устройства ОШ СП. по которому ЭВМ сни0 мает адрес, сигналы ввода-вывода и синхронизации активного устройства ОШ СА. По снятию сигнала ОШ СА селектор адреса 12 снимает сигналы занятости, чтения, выборки, ОШ СП.

5 Запись и чтение регистра состояния 16 и чтение постоянного запоминающего устройства 11 осуществляется без арбитража внутренних шин станции, т с. они подключены непосредственно ко рходам и выходам второго приемопер д-1тм1 ка 9.

Рассмотрим работу станции локальной сети при выполнении операций записи информации, получаемой из моноканала, в блок буферной памяти 8 и ее последующей выдачи в ЭВМ.

Блок постоянно прослушивает канал связи и в случае появления передачи производит прием и дешифрацию адресной части передаваемого кадра информации. Из бито пой последовательности данных, покупающей на вход блока 7, последний формирует слова данных. По окончании формирования слова данных блока 7 вырабатывает сигнал запроса записи, поступающий на вход первого Б контроллера прямот доступа. Получив сигнал запроса записи, контроллер 5 осуществляет захват внутренних шин станции, предварительно определив, что внутренние шины не используются каким-либо другим блоком станции. Захватив ннутрен- ние шины, контроллер 5 формирует сигнал строба записи, поступающий п блок 7. При получении этого сигнала слово данных г, информационных выходов блока 7 поступает на внутреннюю шину данных и контроллер 7 сбрасывает сигнал запроса записи.

Затем с адресных выходов контроллера 5 на внутреннюю шин/ адреса поступает код адреса ячейки памяти, по которому производится запись слова данных

Затем контроллер 5 вырабатывает сигнал строба записи на одноименный вход блока буферной памяти 8. По этому сигналу происходит запись слова данных с внутренней шины данных в ячейку блока 8 по указанному контроллером 5 адресу. По окончанию сигнала ci роба записи и сигнала записи в память происходит увеличение значения адреса внутри страницы на единицу, тем самым подготавливается адрес внутри страницы для следующего слова данных, Затем контроллер 5 освобождает внутренние шины станции, что делает их доступными для других блоков. Параллельно с этим блок 7 осуществляет прием битовой информации из канала связи и Формирование следующего слова данных. При поступлении на вход контроллера 5 следующих сигналов запроса записи процедура записи слов в блок буферной памяти 8 происходит аналогично.

Прием кадра и запись сформированных из него слов в блок 8 буферной памяти происходит до завершения передачи в канале связи. После этого блок 7 проверяет правильность приема кадра (по полиномиальной контрольной сумме) и в случае нормального завершения формирует слово состояния приемника, содержащее информацию о нормальном завершении операции

записи и о номере заполненной страницы блока буферной памяти 8; формирует сигнал прерывания, который через одноименный вход блока сопряжения с ЭВМ 2 поступает 5 на первый вход регистра состояний 16 и сигнал конца записи, который с выхода блока 7 поступает на вход контроллера 5

По сигналу конца записи в контроллере Б восстанавливается значение начального

О адреса внутри страницы, а в памяти свободных страниц контроллера 5. заполненная страница помечается как занятая и контроллер переключается на новую свободную страницу, в результате этого на выходе кон5 троллера подтверждается сигнал готовности к записи (наличия свободных страниц). Таким образом, благодаря указанному механизму обеспечивается прием блока данных из канала связи, состоящего из не0 скольких кадров, следующих синхронно один за другим с минимальными временными интервалами.

Одновременно с приемом следующего кадра данных в свободную страницу блока

5 буферной памяти 8 происходит обработка сигнала прерываний. С первого входа регистра состояний 16 сигнал прерывания на элементах 50, 51 преобразуется в сигнал запроса прерываний, который со второго

0 выхода регистра состояний 16 поступает на одноименный вход схемы управления прерываниями 19, которая формирует необходимые управляющие сигналы ЭВМ, соответствующие процессу прерывания

5 программы. По прерыванию ЭВМ читает регистр состояний 16, в котором хранятся биты, имеющие, например, следующие значения:

1)установлен триггер готовности;

0 2) есть прерывание по окончанию обмена между ЭВМ и станцией в режиме прямого доступа;

3) есть прерывание от приемника блока сопряжения с каналом связи 7;

5 4) есть прерывание от передатчика блока сопряжения с каналом связи 7.

Прочитав регистр состояний 16 и определив, что прерывание пришло от приемника блока сопряжения с каналом связи 7,

0 ЭВМ читает регистр состояний приемника, по которому сбрасывается сигнал прерывания блока 7 и переходит к приему информации из блока буферной памяти 8 в ЭВМ в случае отсутствия ошибок в принятом из

5 канала связи кадре. Для этого ЭВМ программирует второй контроллер прямого доступа 6 на запись информации в ОЗУ ЭВМ а контроллер прямого доступа 18 - на чтение информации из блока буферной памяти 8. После окончания программирования контраппера 18 на его выходе готовности к ч гению устанавливается активный ниокий логический уровень (фиг.10). С выхода контроллера прямою доступа 18 сигнал готовности поступает на вход узла упраоле- НИР 11. На элемен rax 60, 66 узла управления 17 формируется сигнал запроса чтения, ло- ступзюи(ий на вход контроллера 18. Получив этот сигнал, контроллер 18 захватывает внутренние шины станции, устанавливает адрес, сигналы строба чтения и чтения буферной памяти, По сигналу чтения буферной памяти на внутреннюю шину данных с блока буферной памяти 8 поступает информация, которая по сигналу, вырабатываемому на элементе 34 селектора адреса VI из сигнала строба чтения фиксируется во втором буферном регистре 15. По переднему фр ж ту сигнала (.тробо чтения на элемен- гэ 18, 54 регистра состояний 16 формируйся ся нал запроса прямого до- Tvi ), поступает на управляющий a G/i и/ил ,- /прилепил прямым доступом 3 bios о .ыр Пч-пваетсигнал запроса канала д/м непосредственного доступа к ОЗУ ЭВМ ОШ Зг НЛ Получив сигнал ОШ ЗКНД, ЭВМ ч освобождения канала, устанавливает г.шчт г уедоогавлинич кзнзля дол непос пятого доступа к ОЗУ ЭВМ ОШ ПкН/. Сигнал строба чтения по гупает на n-. jfl запрись эп1 иси пторою контроллера прямою , Hj iyn;i 6 Получ.ш этот сигнал к тшгч.лгррб м-мнаи/лшаегсЕинйлы с гроба °;jnnc.j r pood адреса СА 2 и сигналы адрс Сиг адреса посту паю г л входы г;ер SGI и приемопередатчика 1, По началу си/ила с i роба записи посредством элемент г 57, 58. 61, 64 блока управления 17 прекращается поступление сигнала тактовой частоты на вход второго контроллера Mp fix oro доступа 6.

iloT iii B сигнял ОШ ПКИЦ. станция за- Хьдтыилгт копал ЭВМ и блок упраплгмич прямом доЛ1упом 3 снимав сигнал ОШ ЗК1- Д По снятию сигнала ОШ ЗКНД. .IBM снимав оигнал ОШ ПКНД, по снятию которого на выходе схемы управления прямым доступом 3 устанавливается сигнал синхронизации адреса САС, который, поступив на шестой вход селектора адреса 12 через элементы 2, -10, 35, устанавливает ня выходах селектора адреса 12 сигналы низкого логического уровня. Первый сигнал поступает на управляющий вход первого приемопередатчика 1, а второй сигнал поступает на управляющий вход второго приемопередатчика 9 и на вход управления сысокоимпе- дансным состоянием второго буферного регистра 15. По первому сигналу переключается первый приемопередатчик 1 и адрес

со второго контроллера прямого доступа б поступает на шину я/ipeca ЭВМ. По второму сигналу второй буферный perncip 15 выводится из высокоимпеданснпго состояния.

переключается второй приемопередатчик 9 и данные поступают на шину данных ЭВМ. Через определенное время задержки после начала сигнала СЛС схема управления прямым доступом 3 через первый приемопере0 датчик 1 выдает в ЭВМ сигнал синхронизации активного устройства ОШ СА, получив который ЭВМ фиксирует адрес и данные и выставляет сиг пап синхронизации пассивного устро :стп 01П СП. Получив

5 сигнал ОШ СП схема управления прямым доступом 3 снимает сигналы СЛС и Oili CA, а узел управления 17 чорез элементы 61, 62, 64 возобновляет подачу гигиала синхронизации на второй контроллер прямого лооу0 па 0, что еызииао снятие чпроя определенное количестьо такгпи CMIHH/K) синхронизации сигналов строОа iani/icn, СА и адреся с оыхг)доп контроллера 6. По окончанию сигнала строба записи р«рмстр

5 ооогояний 16 через элементы 49, Ь4 снимает (,И1нал запроса ИДИ, а yJeл улрявлышя 17 через . леменг 66 запроса чнм ит По CHP1MIO сигнллгЧ СА : -;nt -v.rup а/(рсса 12 через элемент 35, 16 снимай сигналы иы0 Ооркп, fro npcKpasijaoi выдачу чдресд п данных на сооти ггсгнующие нлп«ы ЭПМ. Мо сняпио CHiHj-ig OL I CA, ЭВгИ гним.че CHI- :;ал ОШ СП, иоздейсп уит через первый оход узла yriprin/ietiiTH Г/ьа л -меш 60, чюпри5 водит к установке григ.м.рт 00 с сосгояиие логической одчницы и пидлче сл -/1У 0|| го запросл пония о третий контроллер прямого доступа 10. (Vi J4a последующих слов ;; ЭВМ происходит лчалои но опи0 санному.

После прочтения после/и го слопч третий кинтроллор прямого лО .гупа 18 пидает сигнал конца сфаницы чтения, маорый по стутег но пхг)д конца чтения контроллера

5 18, что вызывает сннше сигнал рлрешс- ний чтения. С выхода контроллера 18 ciu нял поступает на вход регистра состояний 16 и через элементы 47, 53. 50, 31, нызываег установку на втором выходе регистра состоя0 ний 16 сигнала запрога прерываний, которой взденет иуя наолнопчриш- й РАОД схемы управления прерываниями 19 вызывает выдачу прерывания о ЭВМ ЭВМ по прерыванию читает регистр состояний 16 и

5 помечает страницу, из которой был принят кадр, как свободную в первом контполлере прямого доступа 5.

Рассмотрим процесс передачи кадра из ЭВМ в ганзл связи в режимг- прямого доступа к памяти ЭВМ,

ЭВМ, имея блок данных для передачи в канал связи, программирует третий контроллер прямого доступа 18 на запись кадра в блок буферной памяти 8, а второй контроллер прямого доступа 6 на чтение кадра из ОЗУ ЭВМ. После программирования контроллера 6 на его выходе готовности к чтению устанавливаетс-я сигнал низкого уровня, который через вторую группу входов и элементы 56, 63 блока управления 17 устанавливает на первом выходе блока управления 17 сигнал запроса чтения (фиг.9). Сигнал запроса чтения поступает на одноименный вход второго контроллера прямого доступа 6. Получив этот сигнал, второй контроллер прямого доступа 6 устанавливает сигналы строба адреса СА2, строба чтения и адрес ячейки памяти ОЗУ ЭВМ. из которой будет считано первое слово кадра. С адресной шины второго контроллера прямого доступа 6. адрес поступает на входы первого приемопередатчика 1. Сигнал запроса чтения поступает также на четвертый вход регистра состояний 16 и через элементы 48,54 устанавливает на его первом выходе сигнал запроса прямого доступа. Сигнал строба чтения поступает в блок управления 17 через вторую группу входов и с помощью элементов 57, 58, 64, 61 блокирует подачу тактовой частоты на второй контроллер прямого доступа 6. Одновременно с этим сигнал строба чтения поступает через третью группу входов в селектор адреса 12 и посредством элемента 43 устанавливает сигнал выборки.

С первого выхода регистра состояний 16 сигнал запроса ПДП поступает на управляющий вход схемы у правления прямым доступом 3, которая захватывает качал ЭВМ, как было описано выше. Получив адрес и сигнал синхронизации активного устройства ОШ СА, ЭВМ устанавливает данные и сигнал синхронизации пассивного устройства ОШ СП. Через второй приемопередатчик 9 данные поступают на входы первого буферного регистра 14 и записываются в него сигналом, поступающим с третьей группы выходов селектора адреса 12,

По началу сигнала ОШ СП, поступающего на первый вход блока управления 17, блок управления с помощью элементов 62, 64, 61 возобновляет подачу тактовой частоты на второй контроллер прямого доступа 6. Кроме того, по началу сигнала ОШ СП схема управления прямым доступом 3 снимает сигналы САС и ОШ СА. По снятию сигнала ОШ СА ЭВМ снимает информацию с шины данных и сигнал синхронизации пассивного устройства ОШ СП.

Через определенное число тактов второй контроллер прямого доступа 6 снимает сигналы стробов и адрес. По снятию сигнала строба чтения селектор адреса 12 через эле- мент 41 снимает сигнал выборки регистр состояний 16 через элементы 49.54 снимает сигнал запроса ПДП, а узел управления 17 через элемент ЬЗ снимает сигнал запроса чтения и через элемент 65 устанавливает

0 сигнал запроса записи, поступающий с третьей группы выходов блока управления 17 на вход контроллера 18.

Контроллер 18, захватив внутренние шины станции, выдает на внутреннюю шину

5 адреса станции адрес ячейки блока буферной памяти 8, по которому будет записано принятое от ЭВМ слово и устанавливает сигналы строба записи и сигнал записи в буферную память. Сигнал строб записи

0 поступает на пятую группу входов селектора адреса 12 и через элемент 44 устанавливает на выходе селектора адреса 12 сигнал, который с третьей группы выходов селектора адреса 12 поступает на управляющий

5 вход первого буферного регистра 14 и выводит его из высокоимпедансного состояния. Данные с выхода первого буферного регистра 14 поступают на внутреннюю шину данных станции и записываются в ячейку блока

0 буферной памяти 8 сигналом стробы записи. По началу сигнала строба записи, поступающего на третью группу входов узла управления 17 посредством элементов 59, 65, сигнал запроса чтения снимается. Сиг5 нал ОШ СП, воздействует через первый вход блока управления 17 на элемент 56, что приводит к установке триггера 63 в состояние логической единицы в момент окончания сигнала ОШ СП и выдаче следующего запро0 са в контроллер 6. Передача последующих слов в блок буферной памяти 8 из ЭВМ происходит аналогично описанному.

После передачи последнего слова второй контроллер прямого доступа 6 выраба5 тывает сигнал конца страницы чтения, поступающий на его же вход конца чтения, что приводит к снятию сигнала готовности к чтению. После снятия сигнала по концу последнего строба записи на элементах 68-72

0 контроллера прямого доступа 18 вырабатывается импульс конца записи, который, поступая на одноименный вход контроллера 67. переключает память свободных страниц на следующую свободную страницу, Сигнал

5 конца страницы чтения поступает на третью группу входов регистра состояния 16 и устанавливает через элемент 47 триггер 53, что приводит к выдаче через элементы 50, 51 сигнала запроса прерывания в узел управ- ления прерываниями 19, вызывая выдачу

;;рерь. 8зния в ЭВМ. Э8М по прерыванию читает регистр состояний 10.

При успешном завершении пересылки информации из ЭВМ п блок буферной памяти, ЭВМ программирует на передачу первый контроллер прямого доступа 5. Для этого ЭВМ записывает номер страницу, с которой будет производится чтение информации, и длину кадра. После программирования на выходе готовности к чтению первого контроллера прямого доступа 5 появляется активный низкий уровень, который поступает па одноименный вход блока сопряжения с каналом связи 7. Если блок 7 готоз к выдаче данных в канал связи, то он формируе сигнал запрос чтения, KOTopt.u ( р/паег на одноименныи вход контроллера 5 (фиг.7)

Контроллер 5 охватывает внутренние ij.-ti. i.i , формирует сигнал строба HI синя, который с выхода контроллера 5 поступает на одноименный вход блока 7. С адресмы выходов контроллера 5 на внутреннюю шину адреса станции поступает ПРАВЫЙ (начальный) адрес Формируемой по- следовагельмосги адреса данных. Зятем контроллер 5 формирует сигнал чтения памяти, по которому слово данных с блока буферной памяти 8 поступает на информационные входы блока сопряжения с каналом связи 7. Получив сигнал строб чтения, блок сопряжения с каналом связи 7 сбрасы взет сигнал запроса чтения. По заднему фронту el роба слово данных записывается а;тло. 7 В кот роллере 5 происходит увели чоиие значения начального адреса иа единицу и уменьшение на единицу значения ц -ины блока. Контроллер 5 освобождает внутренние шины. На этом заканчивается обслуживание запроса на чтение слова м контроллер 5 готов к приему следующего .запроса.

Блох 7 начиняет побитовую выдачу принятого байта в канал связи и формирует новый сигнал запроса чтения, которой вызывает нозый цикл в работе контроллера 5.

Следующие циклы выполняются также, как указано. После выдачи всего блока данных, первый контроллер прямого доступа 5 сбрасывает сигнал наличия данных для выдачи в канзл связи и формирует сигнал конца чтения. Указанный сигнал с еыходз контроллера 5 поступает на вход блока 7, При поступлении этого сигнала блок 7 формирует слово состояния, содержащее информацию о нормальном завершении операции выдачи данных в моноканал и сигнал прерывания, который с выхода блока 7 посгупает через еход прерываний блока сопряжения с ЭВМ 2 на второй вход оегистра

состоянии 16 и устанавливает гш мял злпро са прерывания в ЭВМ на г юром выходе регистра состояний 1G ЭПМ по прерыванию чигао спопо состояния станции.ппрг

де/пй причину, вчлпашкую преры1 г,;: ;е v rjuno.ii.nei соитоегсшующп длисншп Формула и з о 6 р с i о н и я 1. Станция /юкллкной сети, содерхашля блок сопряжения с каналом спя vt блок Оу

формой памяти, периыи косгро ер прямого доступа, блок сопряжения с ЭВМ связанные между собоп iMyi ргг.чними шинэ- ми дымных и адреса станции, входы записи и чтения блока Оуфе| чоп нлмип м,,.,|| ,по

ченные к одноименным оы/.одлм

КОНТрОЛЛОрЭ ПрПМОГО ДГЧ, iym И Г/;ЮК,1 СО- ГфЯ;КРНИЛ С ЭПН. СХиДЫ 3ol itCil И ЧИ МПЯ гЮрГОВ (,ОПГ1( СНЧЯ С , .ЧгиЫОМ ГВЯ-iH И

пепгого контр,л к.ра г.рямаш днмупл, uwдинемны0 соПпГ , г. руип.ч упрао шюици/ uxo/ioo ;: JIIMHUJ (пучнп

уПрЯОЛЯЮЩН4 ПЫХО/IOiJ О/ТОЬ П С(5 Т -.. 1 Ч С

каналом связи, молклкмгпи;, к г; N/ПОЙ ipynne ynfjrTE)/i4 iiIli/|V пмхо/1/in ;: fi,f)iioi

грут|по упрэвляюи(иу n-идои нерпою :oni- роллкро прямого /{.jCTvna, и пита донных, шина адреса и шин;. управляющих сигналов ЭВМ подк.нг)чс-п|| к ,nu:in n- ным пходам - выходам блоча ,.Ч ннп

г, ЗИМ, отличают ; я с и ч.м. if о, с цел,ю поаынтопия ироиз о/ 1 1). in и упрощения счамции лпк.зльион г.етч, ч иго сведе1;ы второй конфшивр nfun чию дг/riy- пя, гюдключенш и п«одом н /содом данных

к н,(у|рснней шине /данных сгпнцмм, блок yripatUi Hini прчммм доступам, .юдк очон

НЫЙ «ХОДОМ ГМХОДОГ yilpn.bl -lill i , ,i HP

/прагляющих с/м H. J7(Ki , ЛВМ, ,1 ,рс; датчик, подключенный fi/iHiii cH; ,о

-ОЫХОДС.МИ К ЗДиССг) и ПЧГ. Ш КН уПраПЛОНПЯ Ы ОДОМ (lb JO/lOM И /illHi H I4.HXрон злции ити, :| о;о vcipoiicn i , (1Ы ходами - к первой группе ) Оликл сопряжения с ЭВМ, входами i адресной

шине и выходу г стоимости к мению гпорого контроллера пряг-м и доступа и к пыхпду синхронизации активноюустроиства блока управления прямим/юстусоп, буфер, ii/оды которото подключены к адр. мои IKHO

ЭВМ, а пыходы к адресн м плодим агорою контроллера прямого доступа, npi i-jn m-xo ды записи и чтении тк-рюп 6noi(a coiip

НИЯ Г. ЭВМ ПОДКЛЮЧЕНЫ К ОДНОИМ. М ММ

пходчм псроою и jioporo KOFI ;ролл рои прямого доступ,), прер.инсишй блока сопряжения с каналом сспзч под1 личечи Y одноименным оход-чм блока со.чря ,{ с. ЭВМ, вход-иыход энятостг шинк первого контроллера прямого досгупч подкл..чеп к одноименному п--ол, г.ходу- то, , . iip/iжения с ЭВМ, выход последовательного приоритета первого контроллера прямого доступа подключен к входу последовательного приоритета блока сопряжения с ЭВМ, первый управляющий выход блока сопряжения с ЭВМ подключен к управляющему входу блока управления прямым доступом, вторая группа управляющих выходов блока сопряжения с ЭВМ подключена к управляющим входам приемопередатчика и буфера, третья группа управляющих выходов блока сопряжения с ЭВМ подключена к первой группе управляющих входов второго контроллера прямого доступа, первая группа управляющих выходов коюрого подключена к второй группе управляющих входов блока сопряжения с ЭВМ, третий управляющий вход которого подключен к управляющему выходу блока управления прямым доступом, а второй управляющий выход второго контроллера прямого доступа подключен к управляющему входу приемопередатчика.

0 блока сопряжения с ЭВМ, шина управляющих сигналов блока подключена к первому входу узла управления прерыванием, а линия синхронизации пассивного устройства, кроме того, подключена к одноименному вы5 ходу селектора адреса и первому входу узла управления, третья группа входов селектора адреса соединена с третьей группой входов регистра состояния, с второй группой входов узла управления, вторым входом контроллера

0 прямого доступа и является второй группой входов блока сопряжения с ЭВМ, первая группа выходов контроллера прямого доступа является группой выходов блока сопряжения с ЭВМ для записи и чтения блока

5 буферной памяти, причем выход чтения блока буферной памяти контроллера прямого доступа подключен к четвертому входу селектора адреса, первый выход узла управления, подключенный к четвертому входу

0 регистра состояния, второй выход узла управления и строба чтения контроллера прямого доступа являются третьей группой выходов блока сопряжения с ЭВМ. вторая группа выходов контроллера прямо5 го доступа подключена к пятой группе входов регистра состояния, к третьей группе «ходов узла управления и пятой группе входов селектора адреса, вторая группа выходов селектора адреса подключена к

О управляющему входу буфера и является второй группой управляющих выходов блока сопряжения с ЭВМ, третья группа выходов селектора адреса подключена к управляющим входам приемопередатчика и управля5 ющим входам первого и второго буферных регистров, четвертый выход селектора адреса подключен к управляющему входу узла формирования контрольных разрядов, первый выход регистра состояния является пер0 вым выходом блока сопряжения с ЭВМ, второй выход регистра состояния подключен к входу запроса прорывании узла управления прерыванием, третий выход регистра состояния подключен к четвертому входу

5 блока управления, третья группа выходов узла управления подключена к первой группе входов контроллера прямого доступа, шестой пход селектора адроса является третьим управляющим входом блока сопряжения с ЭВМ,

X гУ rf

IfS

I

Lg

l

l

.

l-li

1

xt

i

Золить 8 етонцию

&Ш $А 6ШЪ2

Вых. fa. 17 KSRD2

Ьых$л.6 СА2

&ых fa б CKD2

вых. CL к №

6ш Я/1 /6 VHAR.

5/1 3 aw JKH4

От 36/1 ош пкнд

SuuS/t J С АС

л ЭЬП ОЩ Ы

ош сп

от

ЭЈП

ошл

ЭЬП ош ЛР

fa П

Вых & 1$ Сикъ

bbrx.fa 1S CWM

Фн 9

о f

iD Т см

ОС

(

ош АДР oai S/&

| Ветряный двигатель | 1925 |

|

SU1839A1 |

| Техническое описание, инструкция по эксплуатации 662451090507 ТО, 1988 | |||

| Станция локальной сети | 1987 |

|

SU1478221A1 |

Авторы

Даты

1993-06-30—Публикация

1990-12-20—Подача