Изобретение относится к области полупроводигиковой имнульсной техники II может найти нр1име.нен.ие нр.и создании различных устройств .наносекундного диапазона, в вычислительной и .радиоизмерителыюй технике.

По основному авт. овид. N° 345600 известно устройство задержки .импульсов.

С целью расшдрен:ия диалазона регулирования, возможности работы в режиме одновибратора и предотвращения прохождения выходных .имиульсо.в в цепь источника входных сигналов предлагаемое уст ройство снабжено дошолнительно источником имиульсного питаиия диода с накоплением заряда, выполненного на п-р-п транзисторном ключе, эмиттер которого через индуктивность соеди нен с анодом диода с иакоплением заряда, коллектор подсоединен к резлстивному делителю источника иап-ряжения смещения, нри этом анод диода с наконлением заряда через реэлстор соединен с выходом быстродействующего триггер.ного каскада.

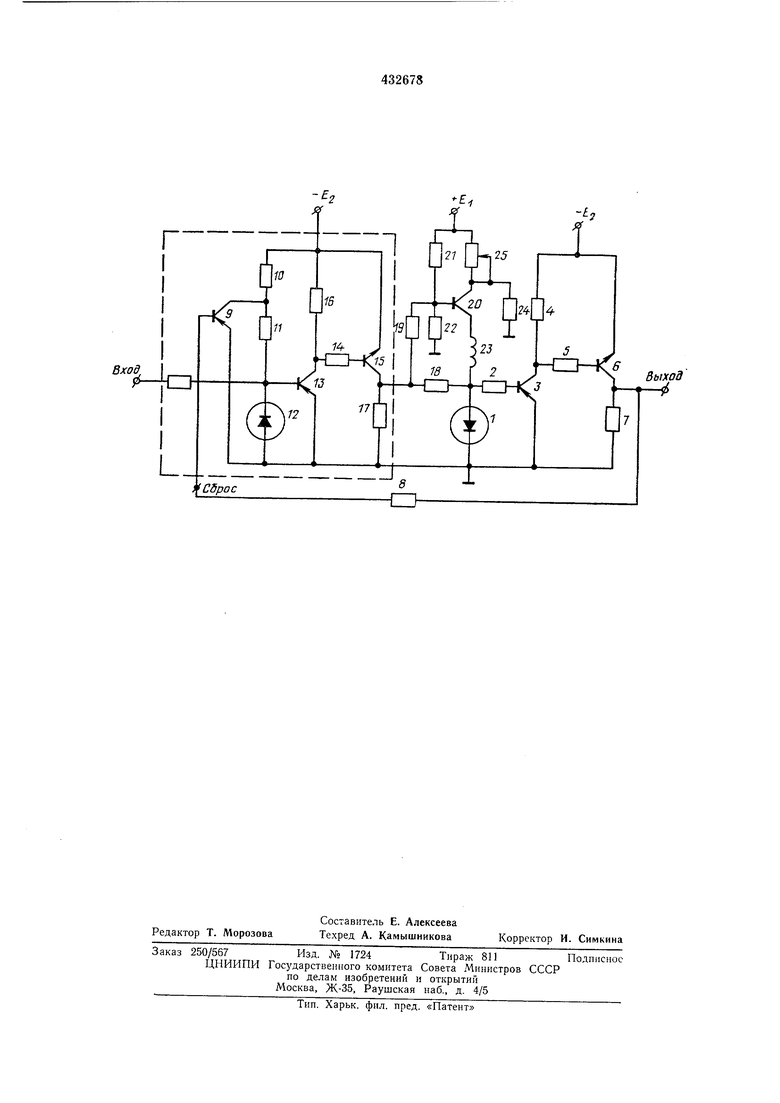

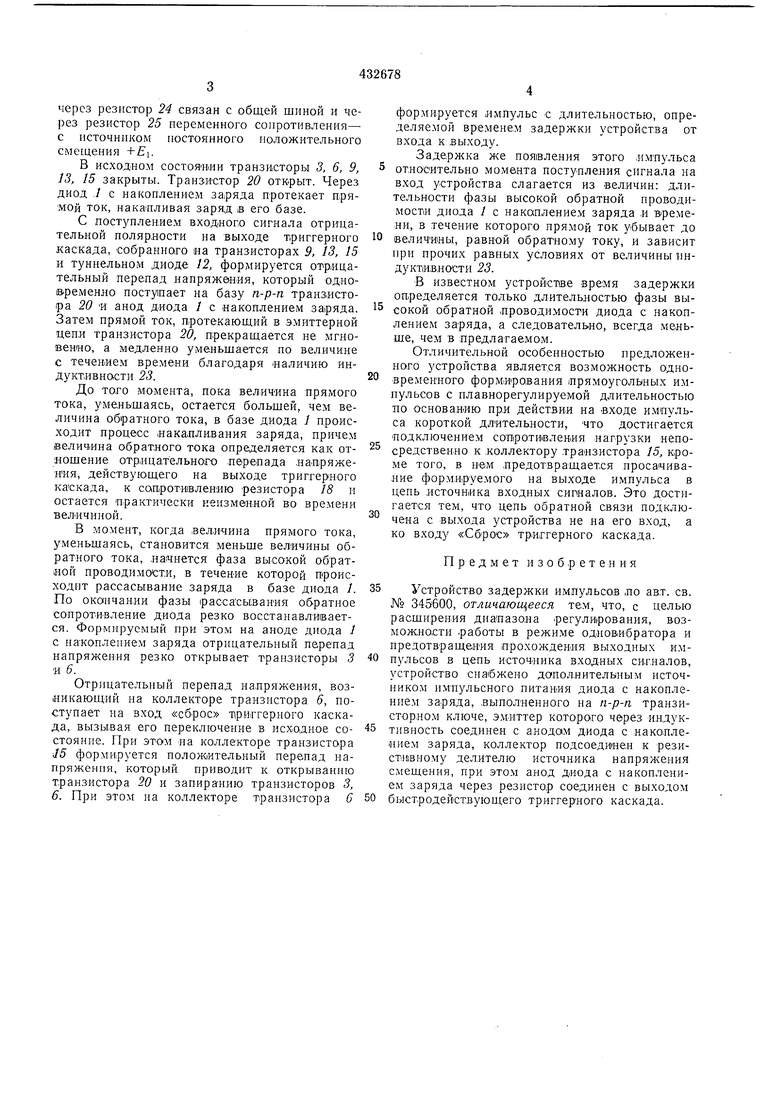

На чертеже представлена прннциниальная схема н,редлагаемого устройства.

Анод диода / с накоплейие.м заряда через резистор 2 связан с базой р-п-р транзистора 3, эмиттер которого подключен к общей шине, коллектор через резистор 4 - к источнику постоянного отрицательного смещения

-Е2, а через резистор о - к базе п-р-п транзистора 6.

Эмиттер транзистора 6 непосредственно связан с ,источ иком ностоянного отрицательного смещения , а коллектор соединен через резистор 7 с общей ши)1ой и через резистор 8 с базой р-п-р транзистора 9. Эмиттер последнего подключен к общей шине, а коллектор через резистор 10 - к источ нику

постоянного отрицательного смещения И через резистор }} к катоду туннельного диода 12, связанного непосредственно с базой р-п-р транзистора 13. Анод туннельного диода 12 и эмиттер транзистора 13 подключены

к общей шине, а коллектор транзистора 13 через рез 1стор 14 подсоединен к базе п-р-п транзистора 15, змнттер которого связан с источником постоянного отрицательного смещеиия -EZ, а через резистор 16 - к тому же

.источнику.

Коллектор транзистора 15 подключен через резистор 17 к общей щине, через резистор 18 - к аноду диода 7 с наконленнем заряда и через резистор 19 - к базе п-р-п транзистора 20. Одно,Бреме}1но база транзнстора 20 через делитель на резисторах 21 и 22 соединена с источником ностоянного положительного смещения +. Эмиттер транзистора 20 через индуктивность 23 подсоединен к аноду диода / с накоплением заряда, а коллектор

через резистор 24 связан с общей шиной и через резистор 25 переменного сопротивления- с источником иостоянного иоложительного смещения +Ei.

В исходном состоящий транзисторы 3, 6, 9, 13, 15 закрыты. Транзистор 20 открыт. Через диод ./ с накоилением заряда иротекает прямой ток, накапливая заряд в его базе.

С лоступлен;ием входного сигнала отрицательной полярвости на выходе триггериого каскада, собранного на транзисторах 9, 13, 15 и туннельном диоде 12, формируется отрицательный перепад напряжения, который одноаременло посту1пает на базу п-р-п транзистора 20 И анод диода / с накоплением заряда. Затем прямой ток, протекающий в эмиттерной цепи транзистора 20, прекращается не мгновенно, а медленно уменьшается по величине с течением времени благодаря «аличию индуктивнасти 23.

До того момента, пока величина прямого тока, уменьшаясь, остается большей, чем величина обратного тока, в базе диода / происходит процесс накапливания заряда, причем величина обратного тока определяется как отношение отрицательного перепада .напряжения, действующего на выходе триггерного каскада, к сапроти1влен ню резистора 18 и остается практически неизменной во времени величиной.

В момент, когда величина прямого тока, уменьшаясь, становится меньше величины обратного тока, начнется фаза высокой обратной проводимости, в течение которой происходит рассасывание заряда в базе диода /. По окончании фазы рассасывания обратное сопротивление диода резко восстанавливается. Формируемый при этом на аноде диода 1 с накоплением заряда отрицательный перепад напряжения резко открывает транзисторы 3 и 6.

Отрицательный перепад напряжения, возникающий на коллекторе транзистора 6, поступает на вход «сброс трштерного каскада, вызывая его переключение в исходное состояние. При этом на коллекторе транзистора 16 формируется положительный перепад иапряжения, который приводит к открыванию транзистора 20 и запиранию транзисторов 3, 6. При этом на коллекторе транзистора 6

формируется импульс с длительностью, определяе.мой временем задержки устройства от входа к выходу.

Задержка же появления этого импульса относительно момента поступления сигнала иа вход устройства слагается из величин: длительности фазы высокой обратной проводимости диода / с накоялением заряда и Времени, в течение которого прямой ток убывает до

величины, равной обратному току, и зависит при прочих равных условиях от величины индукти.вности 23.

В известном устройстве время задержки определяется только длительностью фазы высокой обратной проводимости диода с накоплением заряда, а следовательно, всегда меньше, чем в предлагаемом.

Отличительной особенностью предложенного устройства является возможность одновременного формирования прямоугольных импульсов с плавнорегулируемой длительностью по основанию при действии на входе импульса короткой длительности, -что достигается подключением сопротивления нагрузки непосредствеино к .коллектору транзистора 15, кроме того, в нем .предотвращается иросачивание форм.нруемого на выходе импульса в цеиь источника входных сипналов. Это достигается тем, что цепь обратной связи подключена с выхода устройства не на его вход, а ко входу «Сброс триггерного каскада.

Предмет изобретения

Устройство задержки импульсов по авт. св. № 345600, отличающееся тем, что, с целью расширения диапазона регулирования, возможности работы в режиме одноВ|Ибратора и предотвращения прохождения выходных импульсов в цепь источника входных си.г.налов, устройство сиа1бжено доиол.нительным источником н.мпульсного питания диода с накоплением заря.да, выполненного на п-р-п транзисторном ключе, э.миттер которого через индуктлвность соединен с а.нодам диода с нако.плением заряда, коллектор подсоединен к резистивному дел.ителю источника напряжения смещения, при этом ано.д диода с накоплением заряда через резистор соединен с выходом

быстродействующего триггерного каскада.

Ma

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ЗАПРЕТ» | 1972 |

|

SU423251A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| ОДНОТАКТИЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU291246A1 |

| ОДНОВИБРАТОР | 1973 |

|

SU366554A1 |

| -ГСО-ОЗНАЯ | 1973 |

|

SU369688A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВБИБЛ;10.: КЛ | 1972 |

|

SU350140A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВВ ПТ Бi1П п!?рr-^rfi'"''- ' >& | 1971 |

|

SU422094A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ | 1972 |

|

SU345600A1 |

| ВСЕСОЮЗНАЯ ПАТГ..,.Ч?СКАЙбиблиотека wsBAВ. Е. Мельник | 1972 |

|

SU336812A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU235817A1 |

Даты

1974-06-15—Публикация

1972-08-14—Подача