Изобретение относится к области цифровой Ызгчислительной техники.

Известна логическая схема «ИЛР1-И, содержаш,ая диод с накоплеинем заряда, один вывод которого соединен с выходом л-вхадовой диодной схемы «ИЛИ и через диод- с источником синхронизирующих имнульсов, а другой вывод через разделительный диод соединен с триггером на туннельном диоде.

Цель изобретения - повышение быстродействия и иомехоустойчивости.

Цель достигается тем, что между точкой соединения диода с накоилением заряда и разделительного диода и общей щиной ащтания включен туннельный диод.

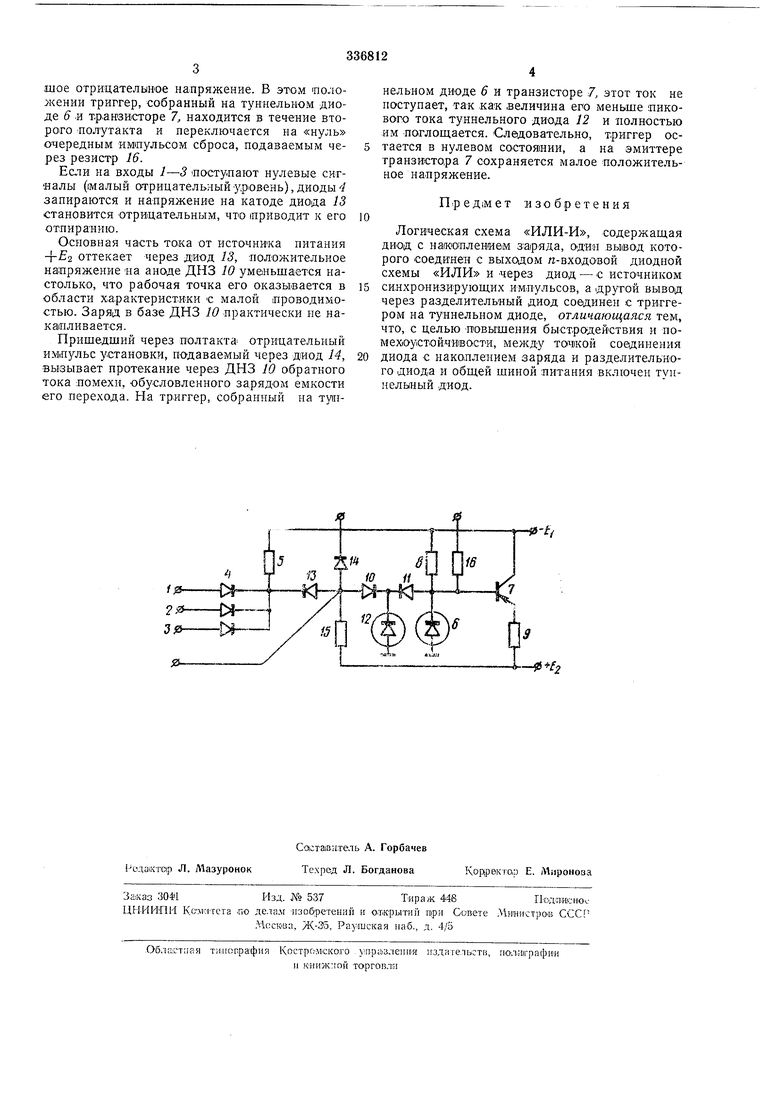

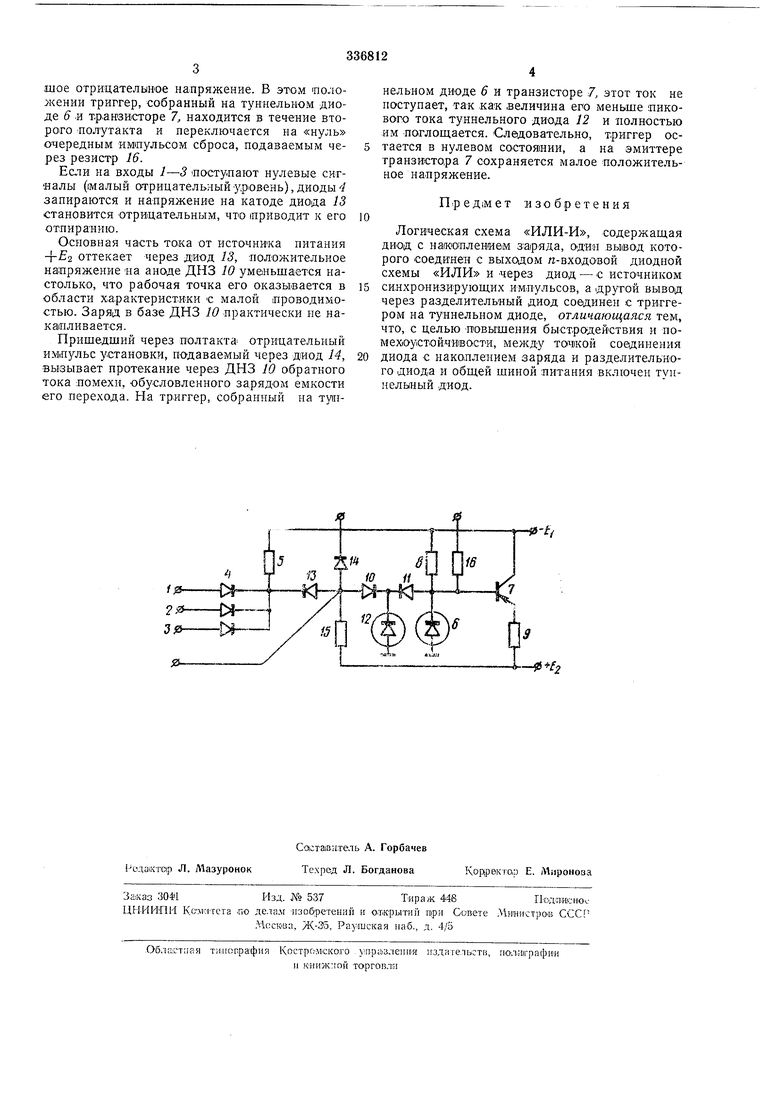

Иа чертеже приведена схема «Р1ЛИ-И, входные сигналы которой имеют положительную полярность, а выходн 1е - отрицательную.

Устройство содержит три входа /, 2 и 5; схему Сборки положительных уровней, образованную па входных диодах 4 и резисторе 5, триггер, собранный на туннель гом диоде 6, транзисторе 7 и резисторах 8 и 9 между диодом с пакоплением заряда (ДНЗ) 10 и разделительном диодом 11 включен туннельный диод 12, выполняющий роль дискримииатора. Кроме того, схема содержит диоды 13 и 14, резисторы 15 и 16 и источники питапия - EI и - -Ezна туннельном диоде 6 и транзисторе / устанавливается в нулевое состояние импульсом сброса, подаваемым через резистор 16. Если в течение первого полутакта на входы I-3 приходит хотя бы один единичный сигнал, то соответствующий диод 4 открыт и на катоде диода 13 также оказывается положительное напряжение, запирающее его. Диод 14 - кремниевый диод, имеющий сравнительно большую протяженность начального участка вольт-а|м0перной характеристики, в результате чего ои также оказывается закрытым. Ток от источника питания протекает через смещенный в обратном направлении и обладающий малым сопротивлением туннельный диод 12 и ДИЗ 10.

В базе ДНЗ 10 происходит наконление заряда неравновеаных носителей. Ириходящнй через полтакта отрицательный ИМПУЛЬС установки, подаваемый через диод 14, рассасывая накопленный заряд, вызывает протекание боль0щого обратного тока через ДНЗ 10. Этот ток намного превышает величину пикового тока туннельного диода 12, в результате чего последний переключается в состояние с больщим сопротивлеиием и основная часть обратного

5 тока протекает через разделительный диод 11 па туннельный диод 6, производя его переключение в высоковольтное (единичное) состояние.

шое отрицательное напряжение. В этом положении триггер, собранный на туннельном диоде 6 .и т.р.анзисторе 7, находится в течение второго полутакта и переключается на «нуль очередным импульсом сброса, подаваемым через резистр 16.

Если на входы /-3 поступают нулевые сигналы (малый отрицательный уровень), диоды запираются и напряжение на катоде диода 13 становится отрицательным, что триводит к его отпиранию.

Основная часть тока от источника питания оттекает через диод 13, положительное напряжение па аноде ДНЗ 10 уменьшается настолько, что рабочая точка его оказывается в области характеристики с малой проводимостью. Заряд в базе ДНЗ 10 практически не накапливается.

Пришедший через полтакта отрицательный им1пульс установки, подаваемый через диод 14, вызывает протекание через ДНЗ 10 обратного тока помехи, обусловленного заря/дом емкости его перехода. На триггер, собранный на ту1ннельном диоде 6 и транзисторе 7, этот ток не поступает, так как .величина его меньше пикового тока туннельного диода 12 и полностью им поглощается. Следовательно, триггер остается в нулевом состоянии, а на эмиттере транзистора 7 сохраняется малое положительное напряжение.

Предмет изобретения

Логическая схема «ИЛИ-И, содержаш,ая диод с накоплением заряда, одии вывод которого соединен с выходом п-входовой диодной схемы «ИЛИ и Через диод - с источником синхронизирующих импульсов, а другой вывод через разделительный диод соединен с триггером на туннельном диоде, отличающаяся тем, что, с целью повышения быстродействия и помех1аустойчи1вости, между точкой соединения диода с накоплением заряда и разделительного диода и общей шиной питания включен туннельный диод.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1974 |

|

SU572930A2 |

| Логическая схема или-и-не | 1973 |

|

SU474109A1 |

| ОЗНАЯ ПАТЕНТШ-г^АН^Г'Е^ИАЯ | 1971 |

|

SU304700A1 |

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

| Быстродействующий датчик случайных импульсов | 1974 |

|

SU519729A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU235817A1 |

| ПАТ?Ш'Ш-[1ХСГ'Е^:чДП | 1973 |

|

SU362487A1 |

| Формирователь импульсов наносекундной длительности | 1978 |

|

SU705659A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДЛИТЕЛЬНОСТИ ИМПУЛЬСОВ ТОКА В НАПРЯЖЕНИЕ | 1971 |

|

SU301843A1 |

Даты

1972-01-01—Публикация