1

Изобретение относится к области автоматики и вычислительной техники и может найти применение в цифровых устройствах различного назначения, например в цифровых системах автоматического управления и контроля, в электронных цифровых вычислительных машинах при повышенных требованиях к их надежности.

Известно мажоритарно-резервированное импульсное устройство, содерл ащее в каждом канале резервируемое устройство, например счетчик, запоминающий элемент, входные и выходные схемы «ИЛИ. Первый выход счетчика в каждом канале известного устройства соединен с цепью записи запомипающего элемента в том же канале, а второй выход соединен с цепью считывания запоминающих элементов двух других каналов через входные схемы «ИЛИ. Выход запоминающего элемента в каждом канале соединен через выходные схемы «ИЛИ с цепями сброса счетчиков всех каналов, а через входные схемы «ИЛИ - с цепями считывания запомипающих элементов двух других каналов.

Однако известное устройство недостаточно надежно вследствие того, что сигнал с выхода запоминающего элемента любого одного канала поступает через выходные схемы «ИЛИ на вход сброса счетчиков всех каналов, а через входные схемы «ИЛИ - на входы считывания запоминающих элементов двух других каналов. В связи с этим неисправность, налри.мер, запоминающего элемента в одном из каналов, заключающаяся в формировании ложного выходного сигнала, приводит к нарушению работоспособности всего резервирогзанного устройства.

Целью изобретения является повышение надежности устройства.

Это достигается тем, что предлагаемое устройство содержит три схемы «И в каждом канале, причем первые в.ходы схем «И в каждом канале соединены с выходом запоминающего элемента, а вторые входы - с выходом

входной схемы «ИЛИ в том же канале, выход первой схемы «И в калсдом канале соединен с входом выходной схемы «ИЛИ в том же канале, выход второй схемы «И соединен с входами входной п выходной схем

«ИЛИ другого канала, а выход третьей схемы «И соединен с входами входной и выходной схем «ИЛИ третьего канала.

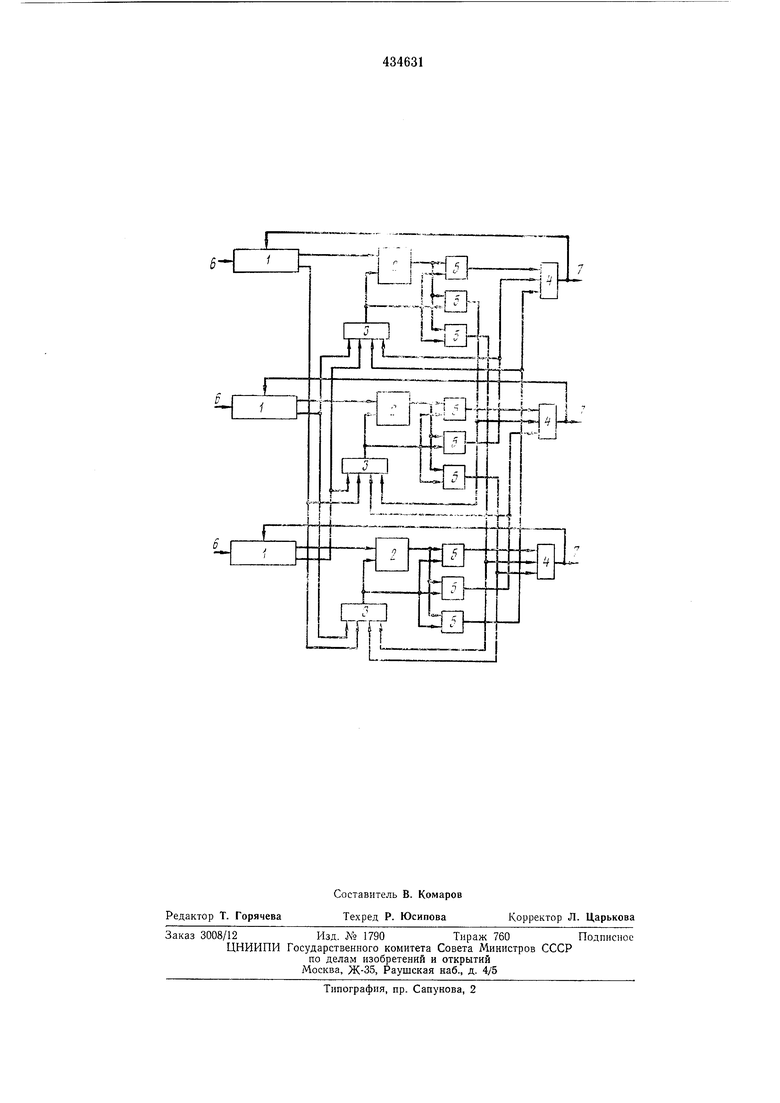

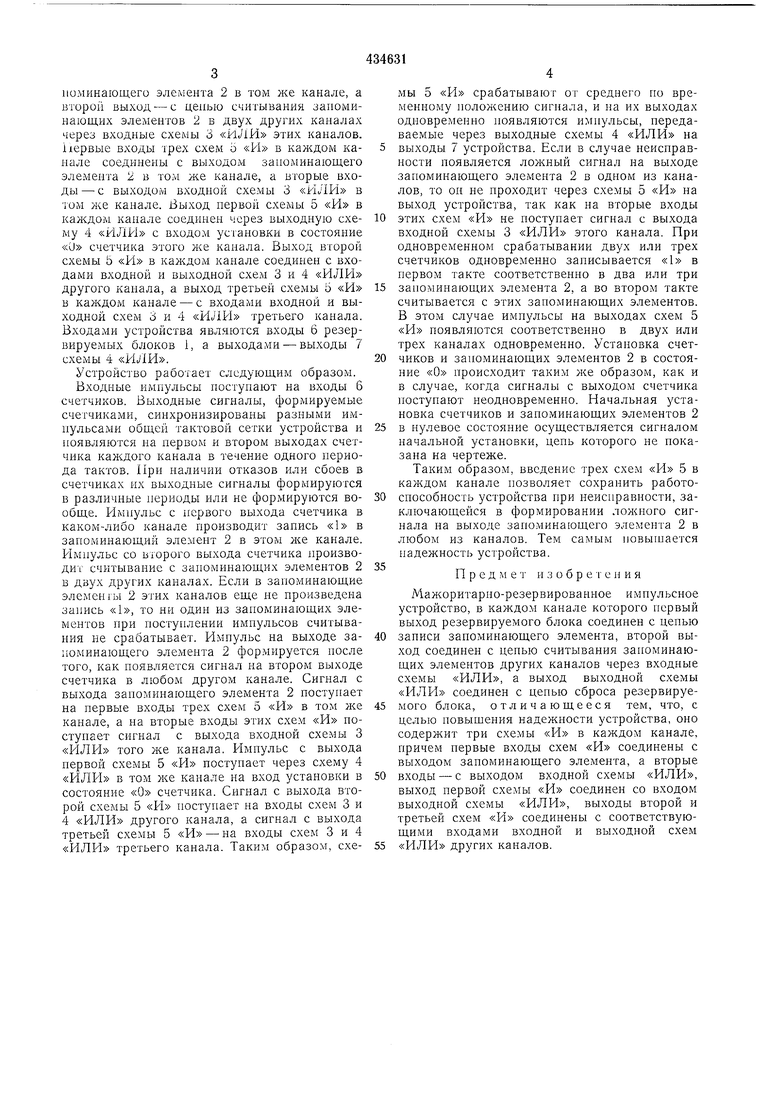

На чертеже показана функциональная схема описываемого устройства.

Оно содержит в каждом из трех каналов резервируемый блок 1, например счетчик импульсов, запоминающий элемент 2, входную схему 3 «ИЛИ, выходную схему 4 «ИЛИ и три схемы 5 «И. Первый выход счетчика в

каждом канале соединен с цепью записи запоминающего элемента 2 в том же канале, а второй выход - с цепью считывания запоминающих элементов 2 в двух других каналах через входные схемв 3 «ИЛИ этих каналов. Иервые входы трех схем о «И в каждом канале соединены с выходом заноминающего элемента 2 в том же канале, а вторые входы - с выходом входной схемы 3 «ИЛИ в том же канале. Выход первой схемы 5 «И в каждом канале соединен через выходную схему 4 «ИЛИ с входом установки в состояние «и счетчика этого же канала. Выход второй схемы 5 «И в каждом канале соединен с входами входной и выходной схем 3 и 4 «ИЛИ другого канала, а выход третьей схемы 5 «И в каждом канале - с входами входной н выходной схем 3 и 4 «ИЛИ третьего канала. Входами устройства являются входы 6 резервируемых блоков 1, а выходами - выходы 7 схемы 4 «И/Ш.

Устройство работает следующим образом.

Входные импульсы постунают на входы 6 счетчиков. Выходные сигналы, формируемые счетчиками, синхронизированы разными имнульсами общей тактовой сетки устройства и появляются на первом и втором выходах счетчика канала в течение одного периода тактов. Ири наличии отказов или сбоев в счетчиках их выходные сигналы формируются в различные периоды или не формируются вообще. Импульс с первого выхода счетчика в каком-либо канале производит запись «1 в запоминающий элемент 2 в этом же канале. Импульс со второго выхода счетчика производит считывание с запоминающих элементов 2 в двух других каналах. Если в запоминающие элементы 2 этих каналов еще не произведена запись «1, то ни один из заноминающих элементов при поступлении импульсов считывания не срабатывает. Импульс на выходе запоминающего элемента 2 формируется после того, как появляется сигнал на втором выходе счетчика в любом другом канале. Сигнал с выхода запоминающего элемента 2 поступает на первые входы трех схем 5 «И в том же канале, а на вторые входы этих схем «И поступает сигнал с выхода входной схемы 3 «ИЛИ того же канала. Имнульс с выхода первой схемы 5 «И поступает через схему 4 «ИЛРЬ в том же канале на вход установки в состояние «О счетчика. Сигнал с выхода второй схемы 5 «И поступает на входы схегм 3 и 4 «ИЛИ другого канала, а сигнал с выхода третьей схемы 5 «И - на входы схем 3 и 4 «ИЛИ третьего канала. Таким образом, схемы 5 «И срабатывают от среднего по временному положению сигнала, и на их выходах одновременно ноявляются имиульсы, передаваемые через выходные схемы 4 «ИЛИ на выходы 7 устройства. Если в случае неисправности появляется ложный сигнал на выходе запоминающего элемента 2 в одном из каналов, то он не проходит через схемы 5 «И на выход устройства, так как на вторые входы

этих схем «И не ноступает сигнал с выхода входной схемы 3 «ИЛИ этого канала. При одновременном срабатывании двух или трех счетчиков одновременно записывается «1 в первом такте соответственно в два или три

заноминающих элемента 2, а во втором такте считывается с этих запоминающих элементов. В этом случае импульсы на выходах схем 5 «И появляются соответственно в двух или трех каналах одновременно. Установка счетчиков и заноминающих элементов 2 в состояние «О происходит таким же образом, как и в случае, когда сигналы с выходом счетчика поступают неодновременно. Начальная установка счетчиков и заноминающих элементов 2

в нулевое состояние осуществляется сигналом начальной установки, цепь которого не показана на чертеже.

Таким образом, введение трех схем «И 5 в каждом канале позволяет сохранить работоспособность устройства при неисправности, заключающейся в формировании ложпого сигнала на выходе запоминающего элемента 2 в любом из каналов. Тем самым повышается надежность устройства.

„

И р е д м е т и з о о р е т е н и я

Мажоритарно-резервированное импульсное устройство, в каждом канале которого первый выход резервируемого блока соединен с цепью

записи запоминающего элемента, второй выход соединен с ценью считывания заноминающих элементов других каналов через входные схемы «ИЛИ, а выход выходной схемы «ИЛИ соединен с цепью сброса резервируемого блока, отличающееся тем, что, с целью повышения надежности устройства, оно содержит три схемы «И в каждом канале, причем первые входы схем «И соединены с выходом запоминающего элемента, а вторые

входы - с выходом входной схемы «ИЛИ, выход первой схемы «И соединен со входом выходной схемы «ИЛИ, выходы второй и третьей схем «И соединены с соответствующими входами входной и выходной схем

«ИЛИ других каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ТОНКИХ Л1АГКИТНЫХ | 1973 |

|

SU404131A1 |

| Мажоритарно-резервированное устройство | 1978 |

|

SU742940A1 |

| Трехканальное резервированное импульсное устройство | 1979 |

|

SU921132A1 |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1981 |

|

SU1058097A1 |

| Мажоритарное устройство | 1981 |

|

SU1019636A1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Адаптивное резервированное устройство | 1980 |

|

SU1003403A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1215113A1 |

| Многоканальный индикатор отказов | 1984 |

|

SU1169207A1 |

Даты

1974-06-30—Публикация

1972-03-16—Подача