I

Изобретение относится к автоматике и вычислительной технике и может найти применение в цифровых устройствах различного назначения,например в цифровых системах автоматического управления и контроля, в электронных цифровых вычислительных машинах,при повышенных требованиях к их надежности.

Известно мажоритарно-резервированное устройство, содержащее в каждом канале резервируемое устройстро, запоминающий элемент И, выход которого через элементы ИЛИ подключен к входам считывания двух других запоминающих элементов l Недостаток устройства заключается в том, что оно работоспособно то.пько при использовании шин синхронизации, общих для всего резервированного устройства. В связи с этим один отказ в цепи синхроимпульсов приводит к прекращению функционирования всего резервированного устройства.

Кроме того,. устройство недостаточно надежно вследствие того,что сигнал с выхода запоминающего злемейта одного из каналов поступает через элементы ИЛИ на выходы устройства,а

следовательно, и на вход сброса счетчиков всех каналов. В связи с этим неисправность запоминающего элемента J в одном из каналов заключается,например, в формировании ложного выходного сигнала, что приводит к нарушению работоспособности всего резервирюванного устройства.

10 Наиболее близким по технической сущности к предлагаемому является мажоритарно-резервированное устройство, содержащее в каждом канале резервируемый блок с двумя выходами,

15 первый элемент ИЛИ, выход которого соединен с первыми входами первого, второго и третьего элементов И и с нулевым входом первого элемента памяти, выход первого элемента И соеди.20 нен с соответствующим входом второго элемента ИЛИ в данном канале, выходы второго и третьего э.пементов И соединены с соответствукяцими двумя входами первого и второго элементов ИЛИ

25 в других каналах, а выход второго элемента ИЛИ соединен с установочным входом резервируемого блока в данном канале 2 .

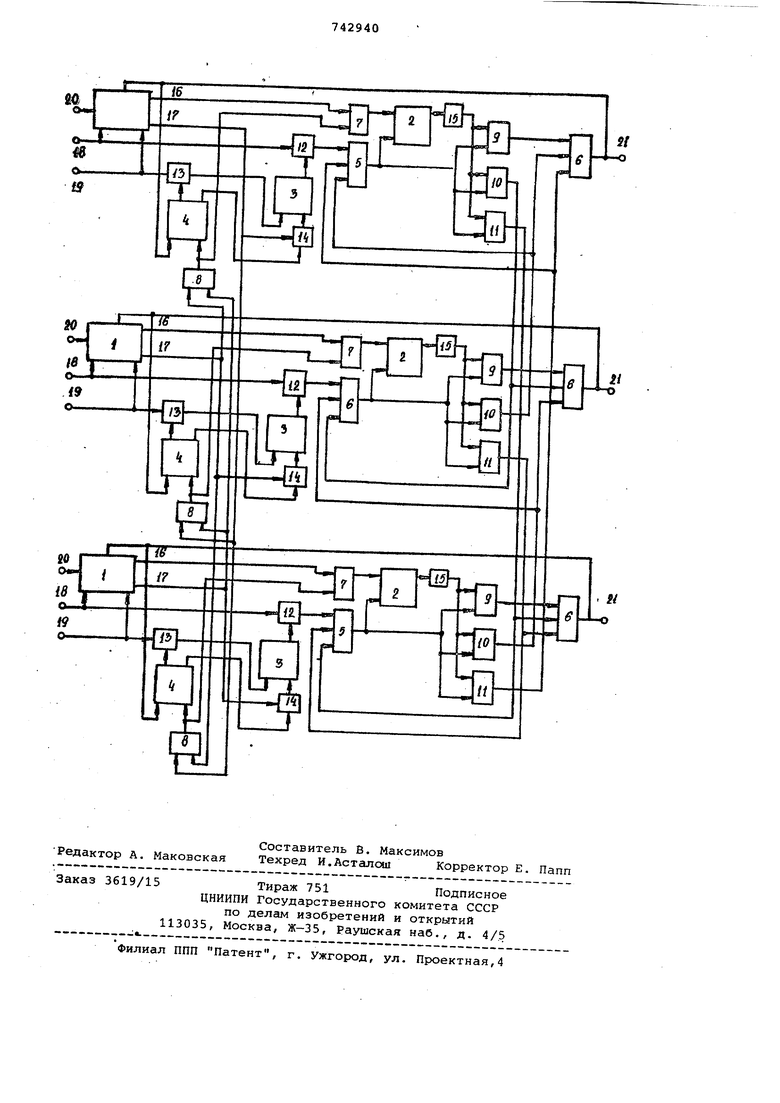

Известное устройство также недостаточно нгшежно вследствие того,что теряет работоспособность при одном отказе в цепи синхронизации,посколь щины синхронизации являются общими для всего мажоритарно-резервированно ро устройства. Кроме того, в извест ном устройстве недостаточно надежно формируются выходные сигналы.Это обусловлено тем, что при отказе одно го элемента И возможно отсутствие сигнала на одном из соответствующих выходов устройства. Цель изобретения - повышение на Дежности устройства. Указанная цель достигается тем, что мажоритарно-резервированное устройство содержит в каждом канале второй и третий элементы памяти,четвертый, пятый и шестой элементы И, третий и четвертый элементы ИЛИ,интегрирующий элемент и две шины син хронизадии, первая из которых соединена с первым входом синхронизации резервируемого блока и через четвертый элемент И - с третьим входом первого элемента ИЛИ, вторая шина синхронизации соединена с вторым входом синхронизации резервируемого блока и через пятый элемент И - с нулевым входом второго элемента памяти, единичный выход которого соед нен с вторым входом четвертого элемента И, первый выход резервируемог ; блока в каждом канале соединен с ; единичным входом первого элемента памяти через третий элемент ИЛИ, вт рой вход которого соединен с выходо четвертого элемента ИЛИ и с единичным входом третьего элемента памяти а единичный выход первого элемента памяти соединен через интегрирующий элемент с первым входом первого, второго и третьего элементов И,второй выход резервируемого блока в каждом канале соединен с первым вх,о дом шестого элемента И в данном каНбше и с соответствующими входами четвертых элементов ИЛИ в друг каналах, второй вход шестого элемен та И соединен с единичным выходом третьего элемента памяти,выход шестого элемента И - с единичным входо .второго элемента памяти, а выход вт рого элемента ИЛИ соединен с нулевым входом третьего элемента памяти нулевой выход которого соединен с вторам входом пятого элемента И. На чертеже приведена функциональ ная блок-схема мажоритарно-резервированного устройства. Устройство содержит в каждом из трех каналов резервируемые блоки 1, например счетные устройства , первый второй и третий элементы 2-4 памяти первый, второй, третий и четвертый элементы 5-8 ИЛИ, первый,второй, третий, четвертый, пятый и шестой элементы 9-14 И, интегрирующий элемент 15, первый и второй выходы 16 и 17 резервируемых блоков 1,первую и вторую шины 18, 19 синхронизации, входы 20 и выходы 21 устройства. Устройство работает следующим образом. В исходном состоянии элементы 2-4 и блоки 1 устанавливаются в состояние О сигналом установки,цепь которого не показана на чертеже.Вход- , ные импульсы поступают на входы 20 блоков 1, а синхроимпульсы, сдвинутые по времени друг относительно друга, - соответственно на шины 18,19 синхронизации и, далее, на первый и второй входы синхронизации резервируемых блоков 1 и на первые входы элементов 12, 13 И. Выходной сигнал, формируемый блоком 1 на выходе 16 каждом канале, синхронизирован инхроимпульсами, поступающими на ину 18 синхронизации импульсов, выходной сигнал на выходе 17 блока 1 - синхроимпульсами,поступающими на шину 19 синхронизации. При наличии отказов или сбоев ,в блоках 1 их выходные сигналы формируются в различные периоды времени или не формируются вообще. Импульс с выхода 16 блока 1 одного из каналов, который срабатывает первым,проходит через элемент 7 ИЛИ и устанавливает в состояние 1 элемент 2, который так же, как и элемент 3,4, может быть выполнен на импульсно-потенциальных элементах или на потенциальных элементах, например, в базисе И-ИЛИ-И. При установке элемента 2 в состояние 1 с его единичного выхода через элемент 15 поступает разрешающий сигнал на вторые входы элементов 9-11 И. Следующий импульс с выхода 17 блока 1, синхронизированный синхроимпульсом, поступающим на шину 19, в свою очередь, проходит через элементы 8 ИЛИ в двух других каналах и устанавливает в состояние 1 элементы 2 и 4. Кроме того, импульс с выхода 17 блока 1 поступает на первый вход элемента 14 И. Так как элемент 4 в рассматриваемом канале находится в состоянии О, то поступивший на первый вход элемента 14 И импульс не проходит на единичный вход элемента 3 памяти. При появлении импульса на выходе 16 блока 1 в другом канале,например во втором, подтверждается состояние 1 элемента 2 памяти в этом канале. Следующий импульс с выхода 17 блока 1 в этом канале проходит через элемент 14 И,поскольку он подготовлен сигналом с единичного выхода элемента 4 , который установлен в состояние 1 импульсом из ранее сработавшего, например, первого канала. Элемент 3 памяти при этом устанавливается в состояние 1 и подготавливает элемент 12 И. Очередной синхроимпульс с шины 18 проходит через элемент 12 И и элемент 5 ИЛИ на нулевой вход элемента 2 памяти и устанавливает его в состояние О, Одновременно импульс с выхода элемента 5 ИЛИ поступает на первые входы элементов 9-11 И и далее - на их выходы, поскольку сигнал на их вторых входах,формируемый на выходе элемента 15, остается разрешающим. Элемент 15 может быть выполнен, например, в виде RC-цепочки и предназначен для задержки спада разрешающего сигнала на вторых входах элементов 9-11 И при установке элемента 2 памяти в состояние О. Импульсы с выходов элементов 9-11 И поступают черезэлементы б ИЛИ на выходы 21 устройства.Одновременно импульс с выхода элемента 10 И поступает в первый канал,а с элемента 11 И в третий канал на соответствующие входы элементов 5 ИЛИ и устанавливает элементы 2 памяти в этих каналах в состояние О, что приводит к формирова-нию импульсов на выходах элементов 9-11 И в этих каналах. Сигналы с выходом элементов 6 ИЛИ в каждом канале осуществляют установку блоков 1 и элементов 4 памяти в сосО

и тем самым подготавлитояние

вают устройство к следующему циклу работы. Элемент 3 памяти при этом устанавливается в состояние О сигналом с выхода элемента 13 И,поскольку последний подготавливается сигна|Лом с нулевого выхода элемента 4 памяти. Аналогичным образом происходит функционирование устройства и при других вариантах появления сигналов на выходах резервируемых блоков 1. В результате формирование сигнала на выходах 21 устройства происходит от среднего по временному положению сигнала одновременно на всех выходах 21 устройства.

Если при неисправности какого-либ элемента 9-11 И в одном из каналов, например элемента 10 И в рассматриваемом, втором канале,сигнал на его выходе, а следовательно, на соответствующем входе элемента 6 ИЛИ и на нулевом входе элемента 2 памяти в первом канале отсутствует, это не сказывается на работоспособности устройства, поскольку установка элемента 2 памяти первого канала в состояние О осуществляется сигналом с выхода элемента 11 И третьего канала. При этом на других входах элемента 6 ИЛИ в первом канале появляются сигналы с выхода элемента 9 ИЛИ первого канала и с выхода элемента 11 И третьего канала. Аналогичная ситуация складывается и при других вариантах появления сигналов на выходах блоков 1 и сочетаниях неисправных элементов 9-11 И. Работоспособность устройства сохраняется также и при полном отказе одного из каналов. В этом случае сигналы на всех выходах 21 устройства продолжают формироваться двумя оставшимися работоспособными каналами. Если оказывается, что формирование сигнала на выходах 21 устройства по двум ранее сработавшим каналам осуществляется в тот момент, когда в оставшемся третьем канале формируется сигнал на выходе 16 резервируемого блока 1, то резервируемый блок 1 в этом канале устанавливается в состояние О сигналом с выхода 21 устройства, а элемент 2 памяти в этом канале усталом, поступающим на один из выходов 5 ИЛИ этого канала с выхода элемента 11 И первого и второго каналов. В связи с этим длительность сигнала на выходе элементов 9-11 И должна превьняать время установки в состояние О резервируемого блока 1,что обеспечивается выбором времени задер1хки интегрирующего элемента 15.

Таким образом, введение дополнительных элементов 3 и 4 памяти, элементов 7,8 ИЛИ элементов 12-14 И, интегрирующего элемента 15 и шин 18,19 синхронизации в каждом канале, во-первых, позволяет обеспечить одновременное формирование сигналов

на входах всех трех каналов устройств при независимой (асинхронной) работе каналов от несин сронных источников, синхроимпульсов. В связи с этим отказ или сбой источника

синхроимпульсов, соединенного с шинами 18 и 19 в каком-либо канале приводит к отказу только этого канала и не влияет на работоспособность остальных каналов устройства. Тем са-- ,

мым повьвиается надежность устройства. Во-вторых, как показывает схемотехнический анализ, надежность устройства повышается и за счет того, что при отказе любого из элементов 9-11 И в одном из каналов на всех трех выходах 21 устройства продолжают правильно формироваться сигналы за счет соответствующих элементов 9-11 И двух других каналов. Тем самым, при одной неисправности в данном устройстве обеспечивается надежное включение последующих устройств, подключаемых к выходам 21. Технико-экономический эффект от использования изобретения определяется, во-первых, существенным снижением требований к надежности, а следовательно, и снижением стоимости задающего генератора, используемого для формирования синхроимпульсов,

поступаккцнх на шины синхронизации, поскольку в каждый канал предлагаемого устройства синхроимпульсы поступают от автономного нерезервированного задающего генератора. Вовторых, за счет исключения влияния

отказов элементов И в каждом канале на работоспособность устройства устраняются те потери, которые могут в той системе, где используется устройство.

Формула изобретения

Мажоритарно-резервированное устройство, содержащее в каждом канале ре1зервируемый блок с двумя выходами, первый элемент ИЛИ, выход которого со|единен с первыми входами первого, второго и третьего элементов И и с нуйевым входом первого элемента памяти, выход первого элемента И соединен с соответствующим входом второго элемента ИЛИ в данном канале, ВЬОсоды второго и третьего элементов сс(единены с соответствующими двумя входами первого и второго элементсэв ИЛИ в других каналах, а выход второго элемента ИЛИ соединен с установочным входом резервируемого блока в данном канале, отличающееся тем, что, с целью повышения надежности устройства, оно содержит в каждом канале второй и третий элементы памяти, четвертый,пятцй и шестой элементы И, третий и четвертый элементы ИЛИ, интегрирующий элемент и две шины синхронизации, первая из которых соединена с первым входом синхронизации резервируемого блока и через четвертый элемент И - с третьим входом первого элемента ИЛИ, вторая шина синхронизации соединена с вторыг-i входом синхронизации резервируемого блока и через пятый элемент И - с нулевым входом второго элемента памяти,единичный выход которого соединен с 5 вторым входом четвертого элемента И, первый выход резервируемого блока в каждом канале соединен с единичным входом первого элемента памяти через третий элемент ИЛИ,второй вход

л которого соединен с выходом четвертого элемента ИЛИ и с единичным вхо|дом третьего элемента памяти, а единичный выход первого элемента памяти соединен через интегрирующий элемент с первьлм входом первого, второго и

5 третьего элементов И, второй выход резервируемого блока в каждом канале соединен с первым входом шестого элемента И в данном канале и с соответствующими входами четвертых элементов ИЛИ в других каналах,второй вход шестого элемента И соединен с единичным выходом третьего элемента памяти, выход шестого элемента И - с единичным входом второго элемента

5 памяти, а выход второго элемента ИЛИ соединен с нулевым входом третьего элемента памяти, нулевой выход которого соединен с вторым входом пятого элемента И.

0 Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 271396, кл. Н 05 К 10/00, 1969.

2.Авторское свидетельство СССР 5 f 434641, кл. Н 05 К 10/00, 1972

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

| Резервированное устройство | 1978 |

|

SU805319A2 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Резервированное устройство | 1991 |

|

SU1785089A1 |

| Четырехканальная резервированная система | 1990 |

|

SU1746383A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Трехканальный резервированный распределитель импульсов | 1980 |

|

SU930318A2 |

Авторы

Даты

1980-06-25—Публикация

1978-02-16—Подача