Изобретение относитя к автомати- ке и вычислительной технике и может найти применение в цифровых устройствах различного назначения, например в цифровых вычислительных и управляющих комплексах, устройствах передачи данных, системах автоматического контроля п-ри повышенных требованиях к их надежности.

Известно адаптивное мажоритарное устройство, содержащее три резервируемых блока, блоки контроля, вхо- . ды которых соединены с выходами резервируемых блоков и имходом восстанавливающего блока, блоки адаптации, выходы которых соединены с соответствующими управляющими входами восстанавливающего блока, первый и второй выходам каждого блока контроля соединены с одноименными входами соответствующего блока гщаптации, а выходы резервируемых блоков соединены с соответствующими информационными входами восстанавливающего блока .

.Недостатком данного устройства является то, что для использования его в больших вычислительных и управляющих комплексах, имеющих большое количество резервируемых блоков.

в системе значительно увеличивается плотность элеьгентов, сконцентрированных, например, на печатныхплатах. Причем элементы (и, ИЛИ, счетчики и триггеры)имеют невысокую степень интеграции, что, в свою очередь, приводит к большим объемам и весам. Кроме того, устройство не обладает достаточно высокими показателями

10 надежности из-за избыточности элементов и сложности методов самоконтроля в процессе выполнения алгоритма основной программы.

Наиболее близким по технической

15 сущности к предлагаемому является адаптивное резервированное устройство, содержащее в каждом канале блок несовпадения, вход которого соединен с выходом резервируемого блока и

20 входом первого элемента И, выход которого подключен к входу восстанавливающего блока, выход которого подключен к -вторым входам блоков несовпадения, накопитель, второй

25 элемент И, формирователь импульсов, Генератор тактовых импульсов и делитель, входы формирователя импульсов соединены с выходами накопителя, а выход - с вторым входом элемента

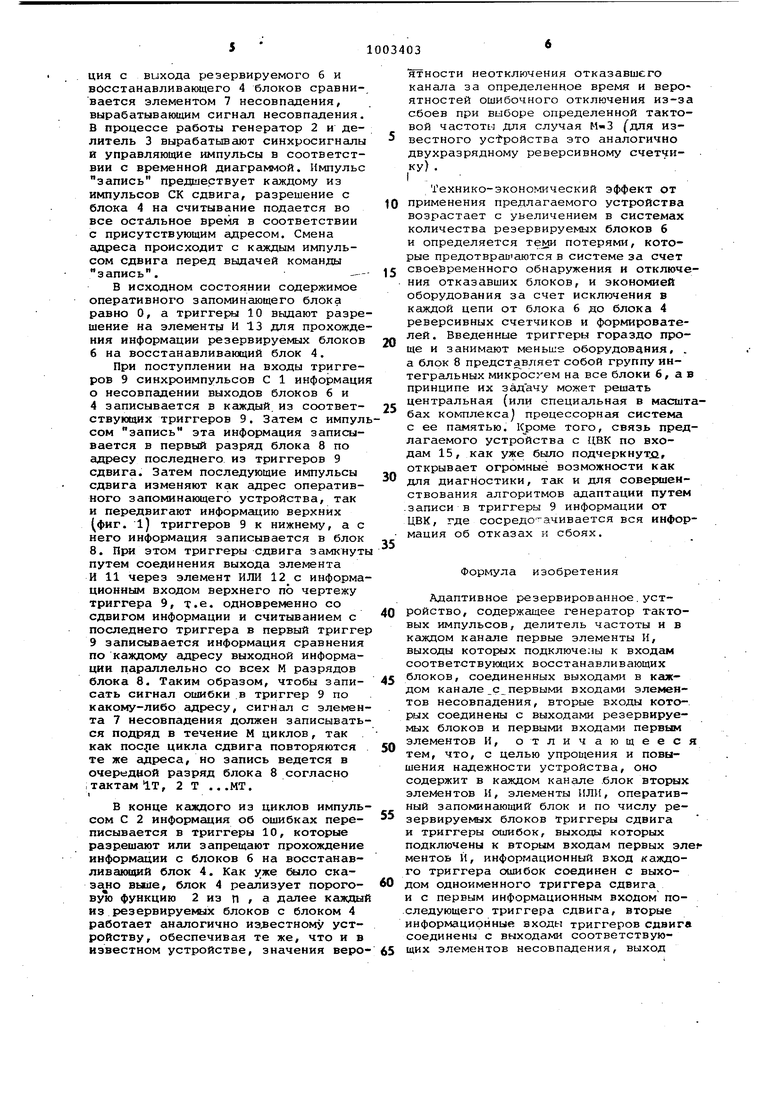

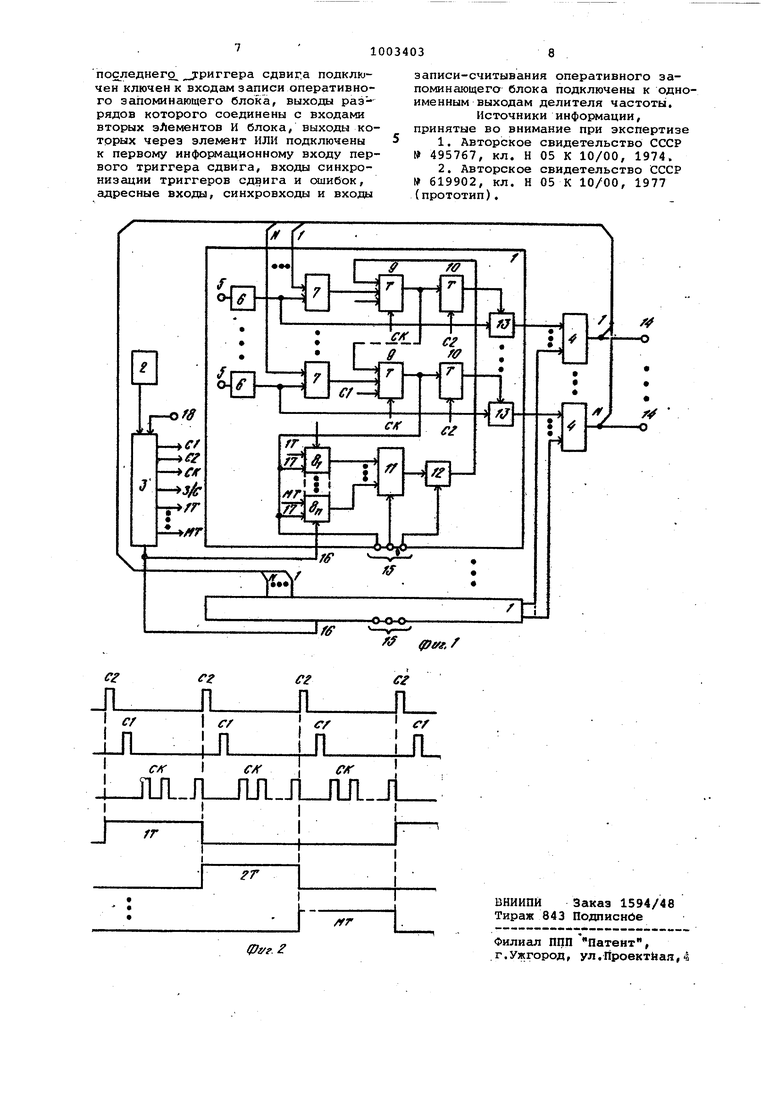

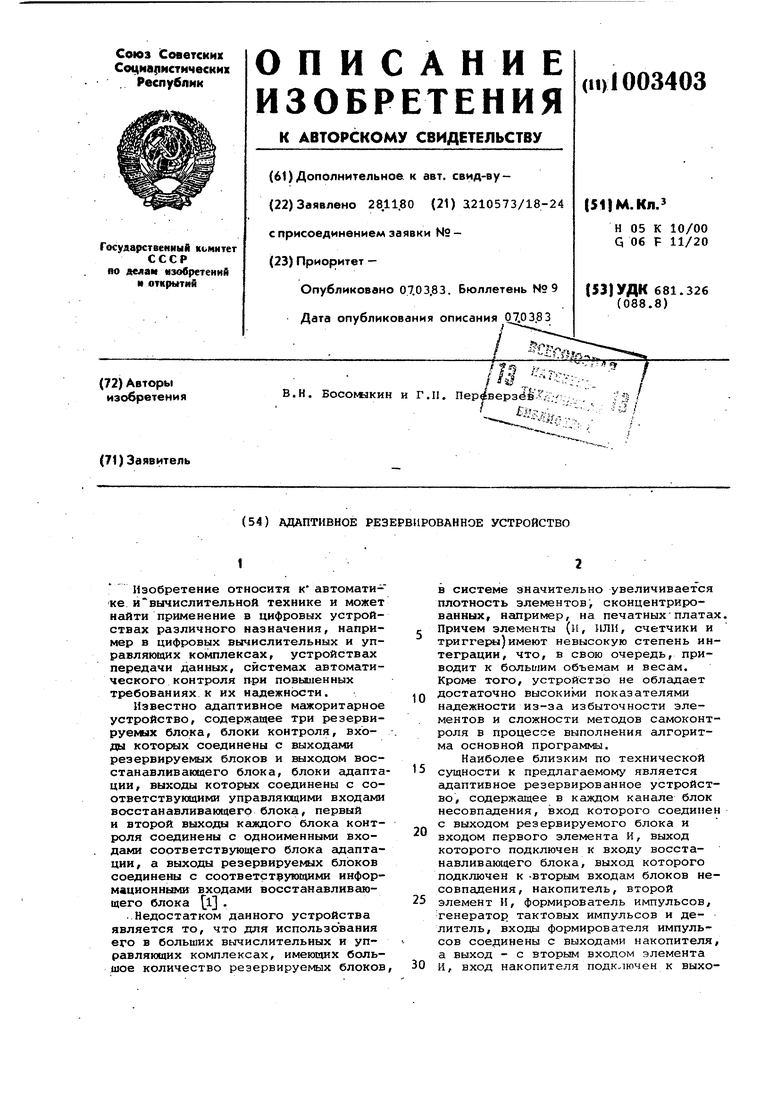

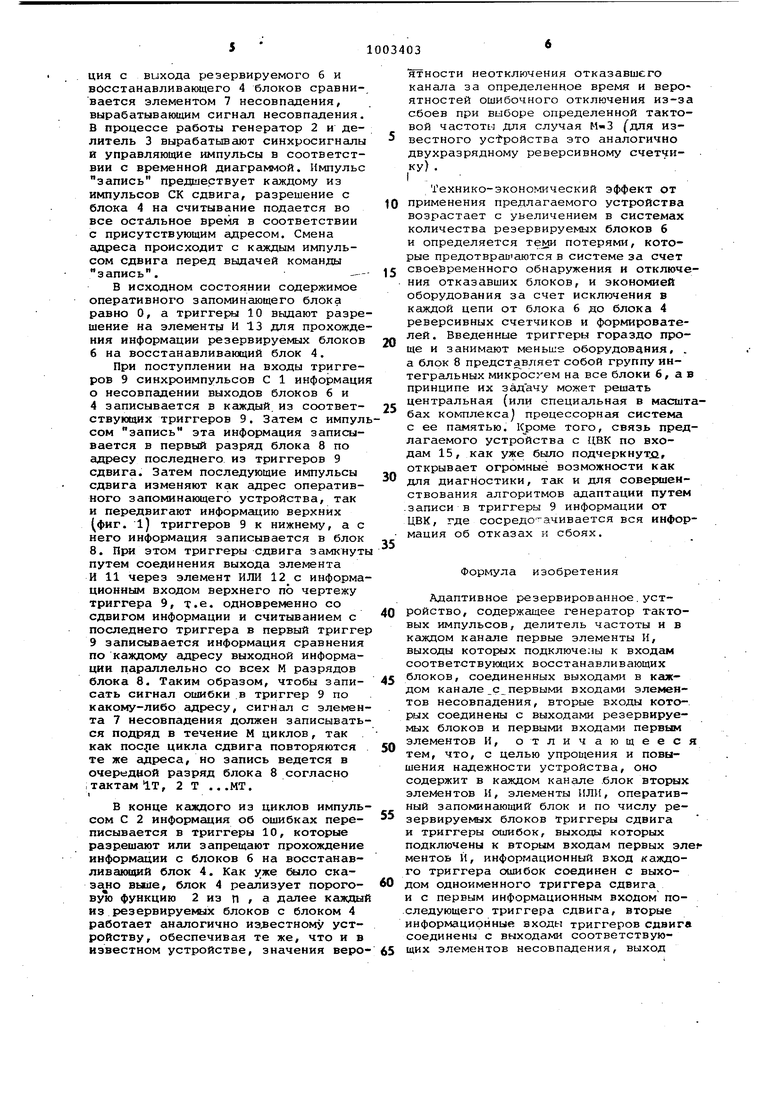

30 И, вход накопителя подключен к выходу второго элемента И, первый вход которого соединен с выходом блока несовпадения, второй вход - с выходом формирователя импульсов, а тр тий - с выходом делителя, вход которого соединен с выходом генератора тактовых импульсов 2j В известном устройстве проблема непрерывного контроля, ошибок резервируемых блоков решена тем, что такие ошибки подсчитываются и накапливаются до определенного предела, после чего информация с отказавшего блока отключается и не поступает с этого момента на восстанавливающий орган. Однако в больших цифровых вы числительных и управляющих комплексах, в устройствах передачи данных, в системах автоматического контроля и других дискретных устройствах, решающих достаточно сложные задачи, информация прежде чем поступить на управляющие (исполнительные) органы проходит целый ряд резервируелих блсжов, объединяелвлх в систему (комплекс), через восстанавливающие органы. В таком случае для обеспечения требуемых показателей надежности при возникновении сбоев перед каждым из восстанавливающих органов после резервируемых блоков необходи мо размещать элементы несовпадений (элементы И, накопители, формирователи и вторые элементы н). При боль шом числе восстанавливакмцих органов (при реализации сложных алгоритмов преобразования дискретной информации) это приводит к большому количес ву вспомогательной аппарутры, непосредственно не участвующей в обработке информации по алгоритму. Кроме того, такое построение затрудняет диагностику этих узлов, что сн жает надежность устройств. Цель изобретения - упрощение и повышение надежности устройства. Поставленная цель достигается тем, что в гщаптивное рез-ервированное устройство, содержащее генерато тактовых импульсов, делитель частоты и в каждом канале первые элементы Н, выходы которых подключены к входам соответствующих ;восстанавливакицих (блоков, соединен1шх выходами в каждом канале с первыми входами элементов несовпадения, вторые входа которых соединены с выходами резервируемых блоков и первыми входами первых элементов И, введены в каждый к нал блок вторых элементов И, элементы ИЛИ, оперативный запоминающий блок и п числу резервируемых блоков триггеры сдвига и триггеры сядибок, выходы которых подключены к вторым входам пер вых элементов И, информационный вход каждого триггера ошибок соединен с выходом одноименного триггера сдвига и с первым информационным входом последующего триггера сдвига, вторые информационные входы триггеров сдвига соединены с выходами соответствующих элементов несовпадения, выход последнего триггера сдвига подклю.чен к входам записи оперативного запоминающего блока, выходы разрядов которого соединены с входами вторых элементов И блока, выходы которых через элемент ИЛИ подключены к первому информационному входу первого триггера сдвига, входы синхронизации триггеров сдвига и ошибок, адресные входы,, синхровходы и входы записи-считывания оперативного запоминающего блока подключены к одноименным выходам делителя частоты. На фиг. 1 представлена блок-схема предлагаемого устройства, на фиг. 2временная диаграмма его работы. Устройство содержит канал 1 резервирования, генератор 2 тактовых импульсов, делитель 3 частоты, восстанавливающие блоки 4, входы 5 резервируемых блоков 6, элементы 7 несовпадения, оперативный запоминающий блок 8 с разрядами , триггеры 9 сдвига, триггеры 10 ошибок, блок вторых элементов И 11, элемент ИЛИ 12, первые элементы И 13, выходы 14 в.осстанавливающих блоков 4, входы 15 Управление для связи с цифровьм вычислительным комплексом ЦВК 15, адресные входы 16 блока 8, информационный вход 17 блока 8, вход 18 управления блокировкой делителя 3. Кроме того, на фиг. 2 обозначена выход С 1 синхроимпульсов делителя 3 для параллельной записи информации в триггеры сдвига ot элементов 7 несовпадения, выход С 2 синхроимпульсов делителя 3 для параллельной записи информации об сшибках в триггеЕ л 10 ошибок, синхроимпульсы СК сдви,га триггеров 9 сдвига. Запись-Считывание вход для управления записью или считыванием блока 8 и выходы IT, 2Т, ...МТ делителя 3, определяющие последовательность работы разурядов оперативного запоминающего в режиме запись. Устройство работает следующим образом. На входы 5 резервируемых блоков 6, реализирующих каждый свой алгоритм функционирования, поступает цифровая информация. После преобразования информация с каждого из блоков 6 поступает на входа элелюнтов И 13, а с их выходов - на входы восстанавливающих блоков 4, реализуняцих пороговую функцию 2 из п , позволякадую обеспечить правильное значение выходного сигнала до тех пор/ пока исправ ны два любых из -п блоков. Информация с вихода резервируемого 6 и вйсстанавливающего 4 блоков сравнивается элементом 7 несовпадения, вырабатывающим сигнал несовпадения.

8процессе работы генератор 2 и делитель 3 вырабатьшают синхросигналы И управляющие импульсы в соответствии с временной диаграммой. Импульс запись предшествует каждому из импульсов СК сдвига, разрешение с блока 4 на считывание подается во все остальное время в соответствии с присутствующим адресом. Смена адреса происходит с каждым импульсом сдвига перед выдачей команды запись.-В исходном состоянии содержимое оперативного запоминающего блока равно О, а триггеры 10 выдают разрешение на элементы И 13 для прохождения информации резервируемых блоков 6 на восстанавливающий блок 4.

При поступлении на входы триггеров 9 синхроимпульсов С 1 информаци о несовпадении выходов блоков 6 и 4 записывается в каждый из соответствуюгцих триггеров 9. Затем с импулсом запись эта информация записывается в первый разряд блока 8 по адресу последнего из триггеров 9 сдвига. Затем последующие импульсы сдвига изменяют как адрес оперативного запоминающего устройства, так и передвигают информацию верхних фиг. ) триггеров 9 к нижнему, а с него информация записывается в блок 8. При этом триггеры сдвига замкнут путем соединения выхода элемента И 11 через элемент ИЛИ 12 с информационным входом верхнего по чертежу триггера 9, т.е. одновременно со сдвигом информации и считыванием с последнего триггера в первый тригге

9записывается информация сравнения по каждому адресу выходной информации параллельно со всех М разрядов блока 8. Таким образом, чтобы записать сигнал ошибки .в триггер 9 по какому-либо адресу, сигнал с элемента 7 несовпадения должен записываться подряд в течение М циклов, так как цикла сдвига повторяются те же адреса, но запись ведется в очередной разряд блока 8 согласно

:тактам 1т, 2 Т ...МТ.

I

В конце каждого из циклов импульсом С 2 информация об ошибках переписывается в триггеры 10, которые разрешают или запрещают прохождение информсщии с блоков 6 на восстанавливающий блок 4. Как уже было сказано ныне, блок 4 реализует порогоBylo функцию 2 из п г а далее кажды из резервируемых блоков с блоком 4 работает аналогично иэзестному устройству, обеспечивая те же, что и в известном устройстве, значения вероятности неотключения отказавшего канала за определенное время и вероятностей ошибочного отключения из-за сбоев при выборе определенной тактовой частоты для случая М-3 (для из5 вестного ус ройства это аналогично двухразрядному реверсивному счетчику) .

Технико-экономический эффект от

0 применения предлагаемого устройства возрастает с увеличением в системах количества резервируег их блоков 6 и определяется теми потерями, которые предотвраиаются в системе за счет

5 своевременного обнаружения и отключения отказавших блоков, и экономией оборудования за счет исключения в каждой цепи от блока 6 до блока 4 реверсивных счетчиков и формирователей . Введенные триггеры гораздо проще и занимают меньше оборудования, . а блок 8 представляет собой группу интегральных микросхем на все блоки 6, а в принципе их задачу может решать центральная (или специальная в масштабах комплекса) прецессорная система с ее памятью. Кроме того, связь предлагаемого устройства с ЦБК по входам 15, как уже было пoдчepкнyтJ г, открывает огромные возможности как

для диагностики, так и для сове маенствования алгоритмов сщаптации путем .записи в триггеры 9 информации от ЦВК, где сосредотачивается вся инфор мация об отказах и сбоях.

5

Формула изобретения

Адаптивное резервированное.уст0 ройство, содержащее генератор тактовых импульсов, делитель частоты и в каждом канале первые элементы И, выходы которых подключены к входам соответствующих восстанавливающих

блоков, соединенных выходами в каждом канале с первыми входами элементов несовпадения, вторые входы кото ых соединены с выходами резервируемых блоков и первыми входами первым элементов И, отличающееся тем, что, с целью упрощения и повышения надежности устройства, оно содержит в каждом канале блок вторых элементов И, элементы ИЛИ, оперативный запоминающий блок и по числу резервируемых блоков Триггеры сдвига и триггеры ошибок, выходы которых подключены к вторым входам первых элe ментов И, информационный вход каждого триггера ошибок соединен с выхо0 дом одноименного триггера сдвига

и с первым информационным входом по.следующего триггера сдвига, вторые информационные входы триггеров сдвига соединены с выходами соответствую5 щих элементов несовпадения, выход

последнего, триггера сдвига подключен ключен к входам записи оперативного запоминающего блока, выходы раз-рядов которого соединены с входами вторых элементов И блока, выходы которых через элемент ИЛИ подключены к первому информационному входу первого триггера сдвига, входы синхронизации триггеров сдвига и сяиибок, адресные входы, синхровходы и входы

записи-считывания оперативного запоминающего блока подключены к одноименным выходам делителя частоты.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 495767, кл. Н 05 К 10/00, 1974.

2.Авторское свидетельство СССР 619902, кл. Н 05 К 10/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для выделения кадрового синхронизирующего слова | 1989 |

|

SU1704146A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1709544A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| Устройство для кодирования информационного сигнала и передачи его в первичную цифровую систему связи | 1987 |

|

SU1483648A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

Авторы

Даты

1983-03-07—Публикация

1980-11-28—Подача