1

Изобретение используется в аналого-цифровых вычислительных машинах.

Известно устройство, содержащее интеграторы, нуль-орган, блок сравнения, ключи, аналоговый запоминающий блок, логические элементы «И, тактовый генератор. Вход первого интегратора через первый и второй ключи соединен с источниками первого и третьего входных напряжений соответственно, а вход второго интегратора через третий и четвертый ключи соединен с источниками опорного и второго входного напряжений.

Недостатком известного устройства является погрешность, обусловленная нестабильностью масштабных коэффициентов интегратора.

Предложенное устройство от известного отличается тем, что с целью увеличения точности в нем вход нуль-органа соединен с выходом первого интегратора, а выход соединен через первый логический элемент «И с нулевым входом первого триггера, единичный выход которого соединен через второй логический элемент «И с управляющими входами второго и четвертого ключей. Входы блока сравнения соединены с выходом второго интегратора и источником опорного напряжения, а БЫХОД соединен через третий логический элемент «И с нулевым входом второго триггера, единичный выход которого соединен через четвертый логический элемент «И с управляющими входами первого и третьего ключей.

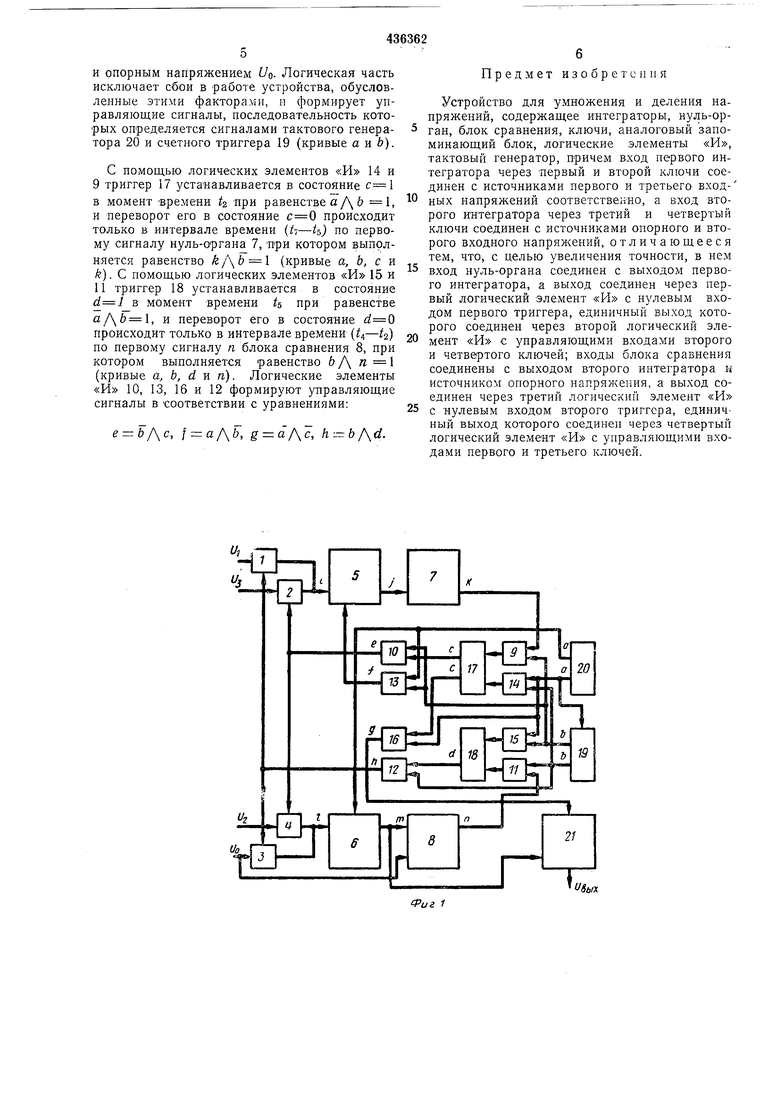

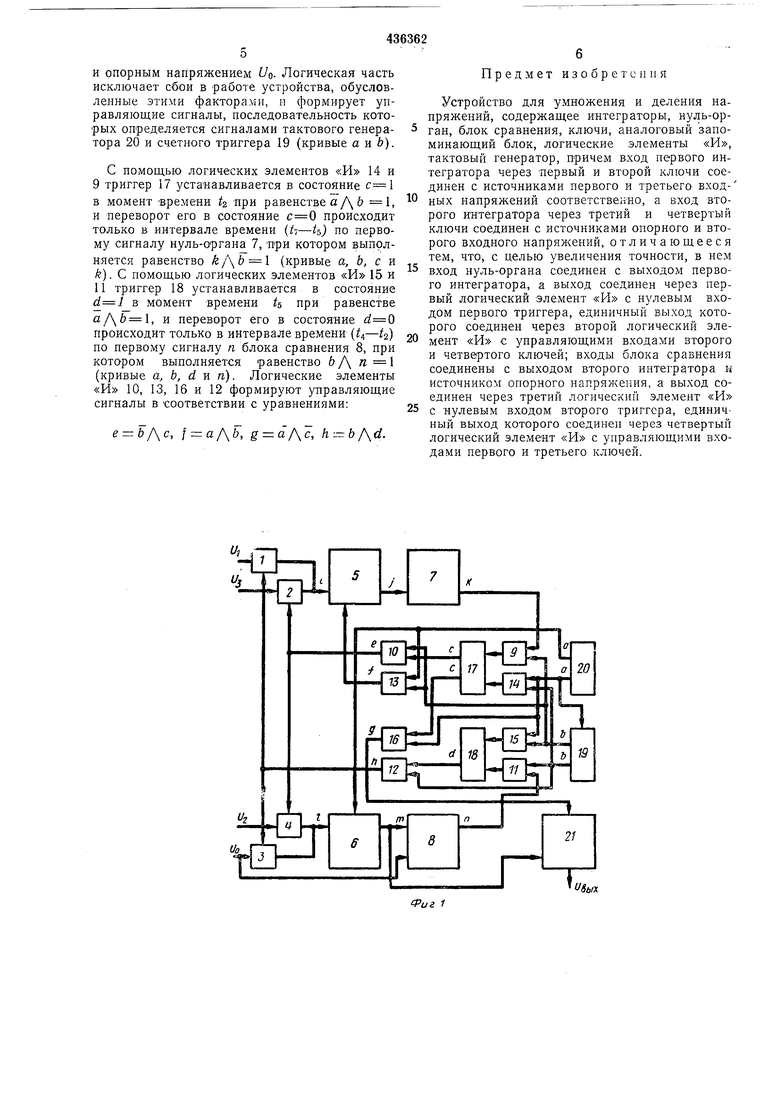

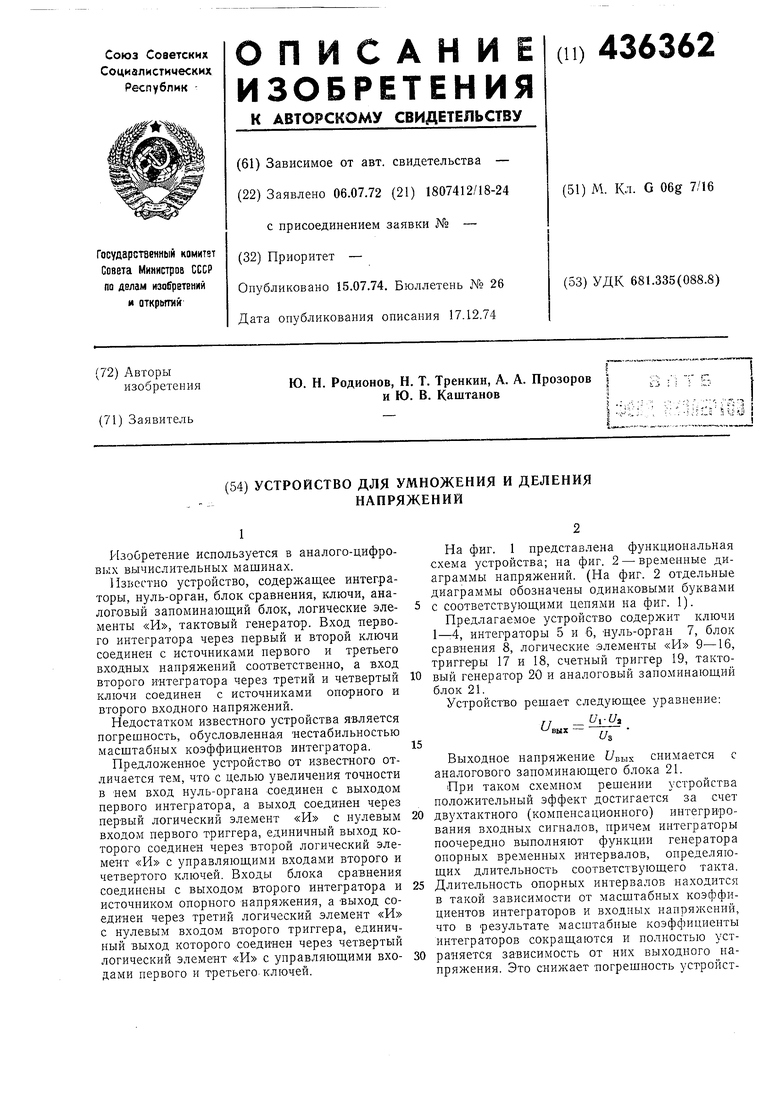

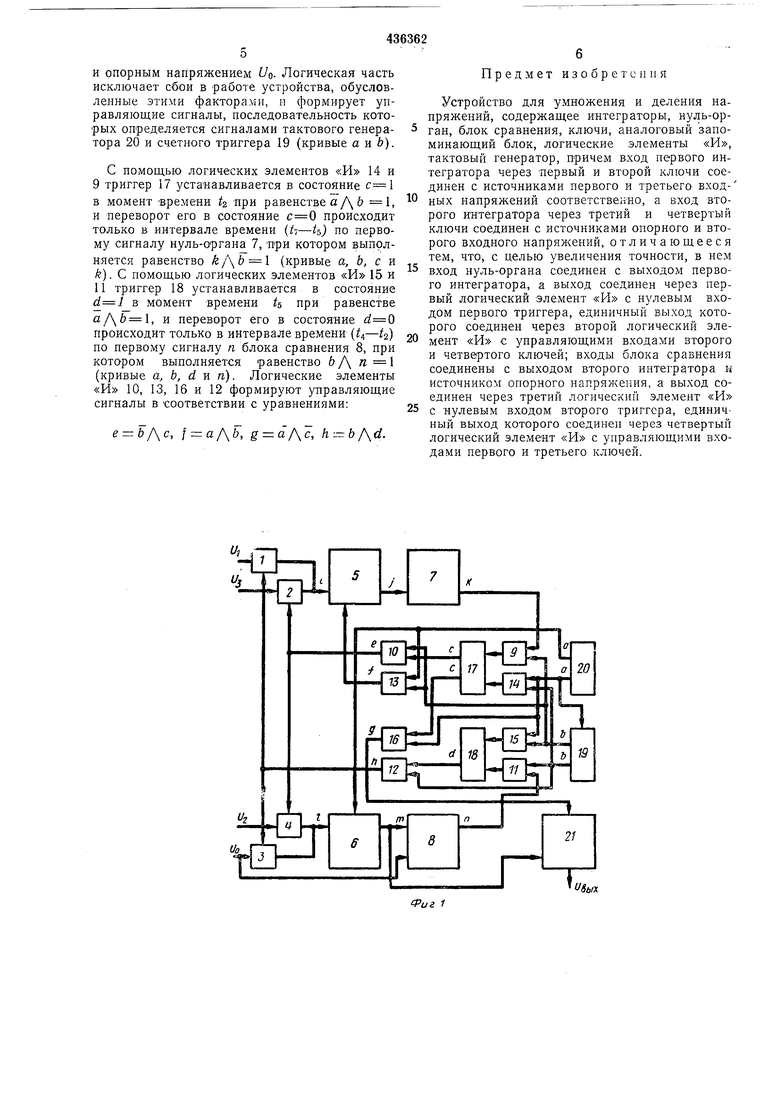

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграммы напряжений. (На фиг. 2 отдельные диаграммы обозначены одинаковыми буквами с соответствующими цепями на фиг. 1).

Предлагаемое устройство содержит ключи , интеграторы 5 и 6, нуль-орган 7, блок сравнения 8, логические элементы «И 9-16, триггеры 17 и 18, счетный триггер 19, тактовый генератор 20 и аналоговый запоминающий блок 21.

Устройство решает следующее уравнение:

и f/,j/

и.

15

Выходное напряжение Ьвых снимается с аналогового запоминающего блока 21.

При таком схемном решении устройства положительный эффект достигается за счет

двухтактного (компенсационного) интегрирования входных сигналов, причем интеграторы поочередно выполняют функции генератора опорных временных интервалов, определяющих длительность соответствующего такта.

Длительность опорных интервалов находится в такой зависимости от масштабных коэффициентов интеграторов и входных напряжений, что в результате масштабпые коэффициенты интеграторов сокращаются и полностью устраняется зависимость от них выходного напряжения. Это снижает погрешность устройства умножения и деления и упрощает его схему и консгрукцию, так как аозволяет использовать интеграторы с нестабильными масштаоными коэффициентами.

Jj.oiM4ecKaH часть устройства, состоящая из элеменшв ;И 9-16 и триггеров 17-19 функциональной схемы, в соответствии с сигналами, получаемыми от тактового генератора /.О, нуль-органа 7 и блока сравнения Ь, вырабатывает последовательность импульсов, управляющих режимом раооты аналоговой части устройства, включающей в себя ключи 1-4, интеграторы о и 6 и блок 21 функциональной схемы.

Полный рабочий цикл устройства занимает интервал времени () и включает в себя два такта интегрирования Ti и TZ. Циклы следуют один за другим так, что коиец предыдущего г является началом последующего ti.

В начале каждого цикла в течение интервала времени () сигналами тактового генератора 20 и логического элемента «И 13 (Кривые а и /) интеграторы б и 6 устанавливаются в исходное нулевое состояние (кривые У и т). Ключи 1-4 находятся в разомкнутом состоянии.

В момент времени 4 управляющий сигнал с логического элемента «И 12 (кривая h) переводит ключи 1 и 3 в замкнутое состояние. Начинается первый такт интегрирования 7ь в течение которого ключи 1 и 3 подключают входы интеграторов 5 и 6 (кривые г и /) к источникам входного Ui и опорного UQ напрял ений соответственно. Длительность первого такта определяет интегратор 6. Его выходное напряжение (кривая т) в интервале времени Оз-4) линейно изменяется.

В момент времени 4 линейно-изменяющееся напряжение но модулю становится равным напряжению Uo, и срабатывает блок сравнения 8, на второй вход которого также подано напряжение L/Q. По сигналу из блока сравнения 8 (кривая п) логическая часть устройства переводит ключи 1 и 3 в разомкнутое состояние (кривая /г). Па выходе интегратора 6 момент времени /з фиксируется напряжение UQ (кривая т).

Таким образом, длительность первого такта интегрирования Ti(t3-tz) зависит только от масштабного коэффициента Ке интегратора 6:

Г - J

Так как в течение интервала TI интегратор 5 интегрировал напряжение f/i, то в момент времени ts при размыкании ключа 3 на выходе интегратора 5 фиксируется напряжение (кривая /).

В течение интервала времени (5-4) сигналом тактового генератора 20 (кривая а) интегратор 6 устанавливается в исходное нулевое состояние (кривая т).

В момент времени is управляющий сигнал с логического элемента «И 10 (кривая е)

переводит ранее разомкнутые ключи 2 и 4 в замкнутое состояние. Начинается второй такм интегрирования TZ, в течение которого ключи 2 и 4 подключают входы интеграторов 5 и б (кривые г и /) к источникам входных на-прял ений 1/3 и {/2 соответственно. Длительность второго такта определяет интегратор 5. Так как напряжение бз на входе интегратора 5 имеет полярность, противоположную полярности напряжения L/i, то выходное напряжение интегратора 5 (крива1Я /) в интервале времени (/6-4) уменьшается по линейному закону. В момент времени te линейно-изменяющееся напряжение переходит через нуль, и срабатывает нуль-орган 7. По сигналу нуль-органа 7 (кривая k) логическая часть устройства переводит ключи 2 и 4 в разомкнутое состояние (кривая е). Па выходе интегратора 5 фиксируется напряжение, близкое к нулю (кривая /;.

Таким образом, длительность, второго такта интегрирования 72 (4-4) равна:

т 2 -

US-K,

Так как в течение интервала TZ интегратор 6 интегрировал напряжение Uz, то в момент времени 4 при размыкании ключа 4 на выходе интегратора 6 фиксируется напряжение (кривая т), равное:

вь.,..

Подставив в это уравнение значение TZ, получим:

г, rf/

ВЫХ -,;

Из этого уравнения видно, что выходное напряжение устройства зависит только от входных напряжений и не зависит от масштабных коэффициентов интеграторов 5 и 6.

В течение интервала времени (т-U) управляющий сигнал с логического элемента «И 16 (кривая g) устанавливает аналоговый запоминающий блок 21 в режим запоминания напряжения f/вых с выхода интегратора 6 (кривая т).

Папряжение, запомненное в аналоговом запоминающем блоке 21, корректируется в следующем рабочем цикле.

Таким образом, выходная величина устройства так же, как и входные величины, представляется в виде непрерывного медленно изменяющегося напряжения.

В течение некоторой части рабочего цикла сигналы на выходах нуль-органа 7 и блока сравнения 8 могут быть неопределенными (заштрихованные части кривых fe и /г). Это объясняется тем, что при ВЫХОДНОМ напряжении

интегратора 5, близком к нулю, состояние нуль-органа 7 Определяется случайными факторами - флуктуациями и дрейфом н)левого уровня. Также неопределенно состояние блока сравнения 8 при близкой к нулю разности

между выходным напряжением и-нтегратора 6 и опорным напряжением UQ. Логическая часть исключает сбои в работе устройства, обусловленные этими факторами, и формирует управляющие сигналы, последовательность которых определяется сигналами тактового генератора 20 и счетного триггера 19 (кривые а и Ь). С помощью логических элементов «И 14 и 9 триггер 17 устанавливается в состояние в момент Бремени tz при равенствеаДб 1, и переворот его в состояние происходит только в интервале времени ( по первому сигналу нуль-органа 7, При котором выполняется равенство 1 (кривые а, Ь, с k). С помощью логических элементов «И 15 и 11 триггер 18 устанавливается в состояние момент времени U при равенстве , и переворот его в состояние происходит только в интервале времени () по первому сигналу п блока сравнения 8, при котором выполняется равенство b/ п (кривые а, Ь, d v( п). Логические элементы «И 10, 13, 16 и 12 формируют управляющие сигналы в -соответствии с уравнениями: e--bf c, f , g , h--b/ d. Предмет изобретения Устройство для умножения и деления напряжений, содержащее интеграторы, нуль-орган, блок сравнения, ключи, аналоговый запоминающий блок, логические элементы «И, тактовый генератор, причем вход первого интегратора через первый и второй ключи соединен с источниками первого и третьего входных напряжений соответствекно, а вход второго интегратора через третий и четвертый ключи соединен с источниками опорного и второго входного напряжений, отличающееся тем, что, с целью увеличения точности, в нем вход нуль-органа соединен с выходом первого интегратора, а выход соединен через первый логический элемент «И с нулевым входом первого триггера, единичный выход которого соединен через второй логический элемент «И с управляющими входами второго и четвертого ключей; входы блока сравнения соединены с выходом второго интегратора и источником опорного напряжения, а выход соединен через третий логический элемент «И с нулевым входом второго триггера, единичный выход которого соединен через четвертый логический элемент «И с управляющими входами первого и третьего ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ | 1972 |

|

SU432531A1 |

| Устройство ввода и вывода информации для время-импульсных вычислительных устройств | 1972 |

|

SU437084A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| ПРЕОБРАЗОВАТЕЛЬ АКТИВНОЙ МОЩНОСТИ В КОД | 1971 |

|

SU313209A1 |

| Аналоговый интегратор | 1987 |

|

SU1425724A1 |

| Аналого-цифровое интегрирующее устройство | 1980 |

|

SU868784A1 |

| Устройство для измерения сдвига фаз | 1977 |

|

SU661398A1 |

| Электромагнитный расходомер | 1986 |

|

SU1509600A1 |

i/г

Даты

1974-07-15—Публикация

1972-07-06—Подача