(54) АНАЛОГО-ЦИФРОВОЕ ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое интергрирующее устройство | 1985 |

|

SU1339591A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Устройство для определения одномерных начальных моментов К-го порядка случайного сигнала | 1983 |

|

SU1108464A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

Изобретение относится к вычислительной технике и может найти применение в устройствах предварительной обработки аналоговой информации в качестве интегратора. Известен аналого-цифровой интерга тор содержаиций преобразователь полярности входного сигнала, аналоговый интегратор, входные и выходные аналоговые вентили, инвертор аналогового сигнала, пороговый элемент, согласующие элементы, счетный триггер, многоразрядный счетчик и цифро аналоговый преобразователь 1. Однако существенный недостаток этого устройства состоит в том, что оно пригодно для интегрирования только однополярных сигналов. Наиболее близким по технической сущности к предлагаемому является аналого-цифровое интегрирующее устройство, содержащее реверсивный пер ключатель входного сигнала, аналого вый интегратор, вход которого соединен с выходом реверсивного перекл чателя, а выход - с первыми входами двух схем сравнения. Схемы сравнения своими выходами соединены со входами логического блока,в состав iKOTOporo входят два триггера и схе ма выделения неравнозначности состояний этих триггеров. Вторые входы этих схем сравнения ссЗединены с соответствуиадими клеммами положительного и отрицательного пороговых уровней потенциала. Первый выход логического блока соединен с тактирующими входами реверсивного переключателя входного сигнала и реверсивного счетчика, второй выход логического блока соединен с логическим входом счетчика, предназначенным для управления направлением счета 2. Однако данное устройство, как и указанное выше, обладает недостатком, заключающимся в том,что сигнал, подлежащий интегрированию, прежде, чем поступить на вход аналогового интегратора, претерпевает инверсию и коммутации, что влечет за собой снижение точности устройства. Цель изобретения - повышение точности устройства. Поставленная цель достигается ем, что в аналого-цифровое интегрирующее устройство, содержащее аналоговый интегратор, первый вход которого является сигнальным входом устройства, а выход соединен с первым входом схемы сравнения, дешифратор, первый

вход которого подключен к выходу схемы сравнения, а первый и второй выходы соединены с входами реверсивного счетчика, выходы которого являются выходами устройства, и реверсивный переключатель, управляющий вход которого подключен к первому выходу дешифратора, введен аналоговый ключ, включенный между выходом реверсивного переключателя и вторым входом аналогового интегратора, при этом выход реверсивного переключателя подключен ко второму входу схемы сравнения,а аналоговый вход соединен с входом опорного уровня устройства, а вторые выход и вход дешифратора связаны соответственно с управляющим входом аналогового ключа и входом тактирующих импульсов устройства.

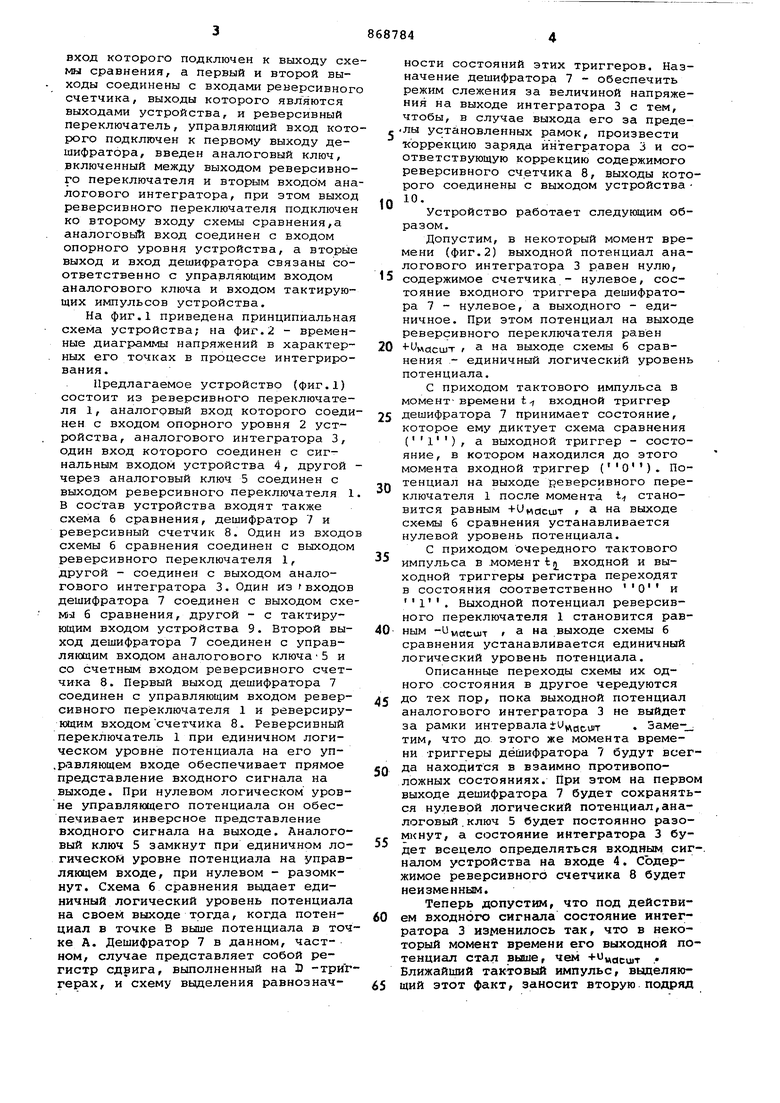

На фиг.1 приведена принципиальная схема устройства; на фиг.2 - временные диаграммы напряжений в характерных его точках в процессе интегрирования.

Предлагаемое устройство {фиг.1) состоит из реверсивного переключателя 1, аналоговый вход которого соединен с входом опорного уровня 2 устройства, аналогового интегратора 3, один вход которого соединен с сигнальным входом устройства 4, другой через аналоговый ключ 5 соединен с выходом реверсивного переключателя 1. В состав устройства входят также схема 6 сравнения, дешифратор 7 и реверсивный счетчик 8. Один из входов схемы б сравнения соединен с выходом реверсивного переключателя 1, другой - соединен с выходом аналогового интегратора 3. Один из входов дешифратора 7 соединен с выходом схеMiJ 6 сравнения, другой - с тактирующим входом устройства 9. Второй выход дешифратора 7 соединен с управляющим входом аналогового ключа5 и со счетным входом реверсивного счетчика 8. Первый выход дешифратора 7 соединен с управляющим входом реверсивного переключателя 1 и реверсирующим входомсчетчика 8. Реверсивный переключатель 1 при единичном логическом уровне потенциала на его уп.равляющем входе обеспечивает прямое представление входного сигнала на выходе. При нулевом логическом уровне управляющего потенциала он обеспечивает инверсное представление входного сигнала на выходе. Аналоговый ключ 5 замкнут при единичном логическом уровне потенциала на управляющем входе, при нулевом - разомкнут. Схема 6 сравнения выдает единичный логический уровень потенциала на своем выходе тогда, когда потенциал в точке В выше потенциала в точке А. Дешифратор 7 в данном, частном, случае представляет собой регистр сдвига, выполненный на D -триггерах, и схему выделения равнозначности состояний этих триггеров. Назначение дешифратора 7 - обеспечить режим слежения за величиной напряжения на выходе интегратора 3 с тем, чтобы, в случае выхода его за пределы установленных рамок, произвести коррекцию заряда интегратора 3 и соответствующую коррекцию содержимого реверсивного счетчика 8, выходы которого соединены с выходом устройства 10.

Устройство работает следующим образом.

Допустим, в некоторый момент времени (фиг.2) выходной потенциал аналогового интегратора 3 равен нулю, содержимое счетчика - нулевое, состояние входного триггера дешифратора 7 - нулевое, а выходного - единичное. При этом потенциал на выходе реверсивного переключателя равен масшт I а на выходе схемы 6 сравнения - единичный логический уровень потенциала.

С приходом тактового импульса в момент-времени t-7 входной триггер дешифратора 7 принимает состояние, которое ему диктует схема сравнения (), а выходной триггер - состояние, в котором находился до этого момента входной триггер (О). Потенциал на выходе реверсивного переключателя 1 после момента t становится равным +UMCICU)T , а на выходе схемы 6 сравнения устанавливается нулевой уровень потенциала.

С приходом очередного тактового импульса в .момент tj входной и выходной триггеры регистра переходят в состояния соответственно О и . Выходной потенциал реверсивного переключателя 1 становится равным -UMCJCUIT г 3 на выходе схемы б сравнения устанавливается единичный логический уровень потенциала.

Описанные переходы схемы их одного состояния в другое чередуются до тех пор, пока выходной потенциал аналогового интегратора 3 не выйдет за рамки интервала . Заме- ТИМ, что до этого же момента времени триггеры дешифратора 7 будут всегда находится в взаимно противоположных состояниях. При этом на первом выходе дешифратора 7 будет сохраняться нулевой логический потенциал,аналоговый .ключ 5 будет постоянно разомкнут, а состояние интегратора 3 бу5дет всецело определяться входным сиг-, налом устройства на входе 4. Содержимое реверсивного счетчика 8 будет неизменньзм.

Теперь допустим, что под действием входного сигнала состояние интегратора 3 изменилось так, что в некоторый момент времени его выходной потенциал стал выше, чем +имаси1т . Ближайший тактовый импульс, выделяющий этот факт, заносит вторую подряд

единицу в дешифратор 7. На выходе, схемы выделения равнозначности состояний этих триггеров возникает единичный логический уровень потенциала. Аналоговый ключ 5 зат ыкается и на вход интегратора 3 поступает положительное значение опорного уровня, вызывающее изменение выходного потенциала интегратора 3 в сторону убывания.

За однин период следования тактовых импульсов интегратору 3 сообщается корректирующая вольт-секундная порция воздействия на входе, соответствующая изменению его выходного потенциала нади- UM . Этого воздействия достаточно, чтобы после одного такта коррекции выходной потенциал интегратора снова оказался внутри интервала ±UM . Очередной тактовый импульс, согласно логике работы устройства, описанной выше, приводит триггеры дешифратора 7 в неравнозначные состояния, аналоговый ключ 5 размыкается и интервал корректирующего воздействия +-масигг на входе интегратора 3 заканчивается. Одновременно реверсивный счетчик 8 получает отрицательное единичное приращение содержимого, поскольку на втором выходе логического блока 7 в данном случае имеет место единичный логический уровень потенциала.

Если выходной пртенциал интегратора 3 под действием входного сигнала изменяется так, что в некоторый момент времени он оказывается ниже, чем , то происходит процесс коррекции, аналогичный описанному. Отличие состоит только в том, что триггеры дешифратора 7 в этом с-лучае находятся в нулевых состояниях, коррекция содержимого интегратора 3 при этом под действием инверсного значения масштабирующего потенциала а реверсивный счетчик 8 получает положительное приращение содержимого на единицу.

Потенциал входа опорного уровня 2 определяет величины пороговых потенциалов +tJwc cu)T и 4iAacuiT /3 через них - цену единицы младшего разряда, реверсивного счетчика 8 в вольт-секундном выражении. Чем выше этотпотенциал, тем большим приращениям интеграла от входного напряжения соответствуют приращения выходного кода. Наличие входа опорного уровня в этом устройстве позволяет осуществить электрическое управление постоянной интегрирования.

5 Таким образом, благодаря аналоговому ключу, введенному в схейу аналого-цифрового интегратора, и предложенным связям предлагаемое устройство является более точным в работе,

0 чем известное, поскольку сигнал/ подлежащий интегрированию, не претерпевает коммутаций и инверсий на входе устройства, а непосредственно поступает на вход аналогового интег5 ратОра 3.

Формула изобретения

Аналого-цифровое интегрирующее

0 устройство, содержащее аналоговый интегратор,первый вход которого является информационным входом устройства, а выход соединен с первым входом схемы сравнения, дешифратор,

5 первый вход которого подключен к выходу схемы сравнения, а первый и второй выходы соединены с входами реверсивного счетчика, выходы которого являются выходами устройства, и ре0версивный переключатель, управляющий вход которого подключен к первому выходу дешифратора, отличающееся тем, что, с целью повышения точности, интегрирования, в него

5 введен аналоговый ключ, включенный между вторым входом аналогового интегратора и выходом реверсивного переключателя, соединенным со вторым входом схемы сравнения, аналоговый,

0 вход реверсивного переключателя соединен с входом опорного уровня устройства, а вторые выход и вход дешифратора связаны соответственно с управляющим входом аналогового ключа и входом тактирующих импульсов уст5ройства.

Источники информации, принятые во внимание при экспертизе

0

(прототип). .

Авторы

Даты

1981-09-30—Публикация

1980-01-14—Подача