1

Известны умножители частоты, состоящие из последовательно соединенных удвоителей частоты, т. е. осун ествляющие умножение путем последовательного удвоения частоты входного сигнала.

Для расширения диапазона умножаемых частот и улучшения динамических свойств в предлагаемый умножитель частоты в каждый из его каскадов, кроме последнего, введены два ключевых элемента, две схемы «И, схема «ИЛИ, согласующее и сравнивающее устройства. Входы ключевых элементов соединены с выходами схем «И, а выходы - с выходами интеграторов, подключенных через согласующее устройство к измерительному входу сравнивающего устройства. Компенсирующий вход сравнивающего устройства соединен с выходом одного из интеграторов последующего каскада, а выход - с одним из входов триггера последующего каскада, другой вход которого через схему «ИЛИ соединен с одним из выходов триггера и со второй схемой «И, а второй вход схемы «ИЛИ - со вторым выходом триггера, первой схемой «И и двумя схемами «И предыдущего каскада.

Выход формирователя прямоугольного напряжения и один из выходов второго триггера подключены ко входам третьей схемы «И, выход которой через разделительные

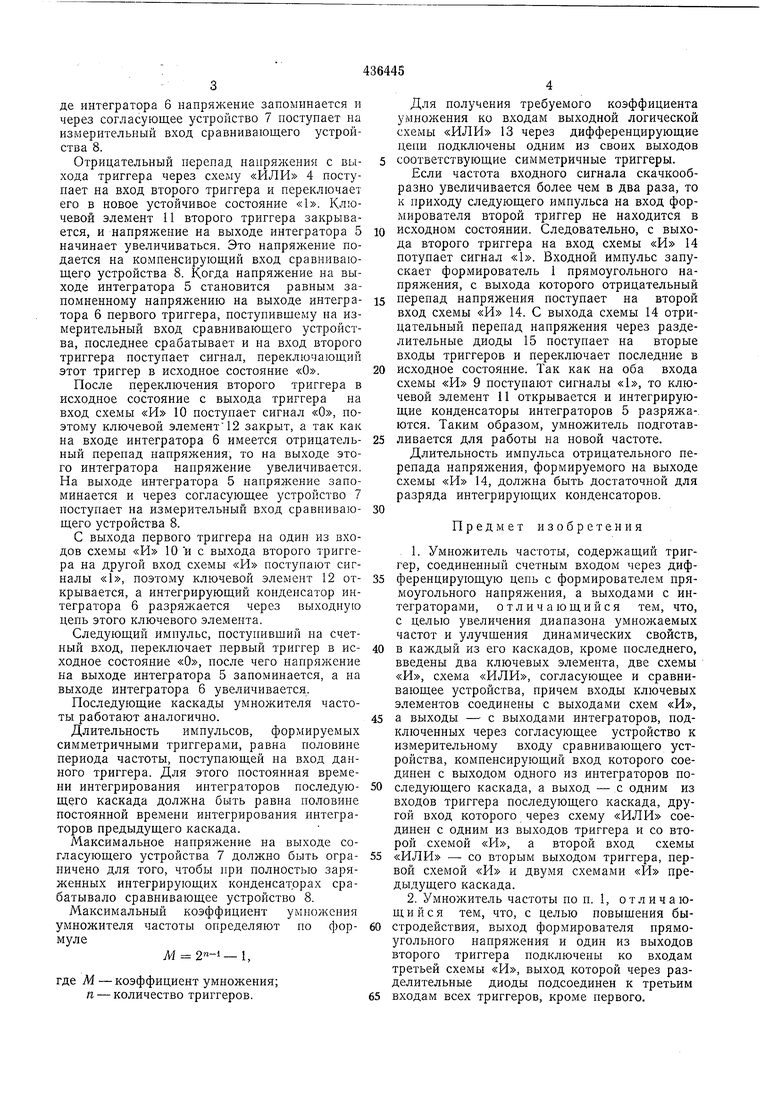

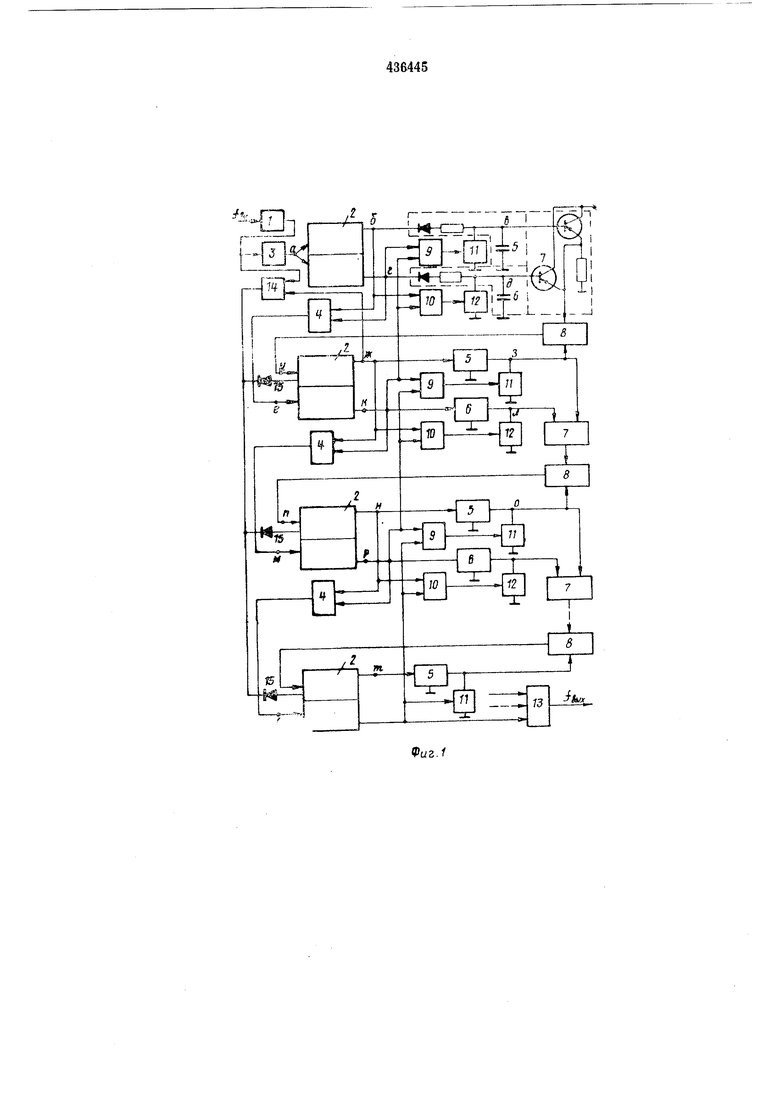

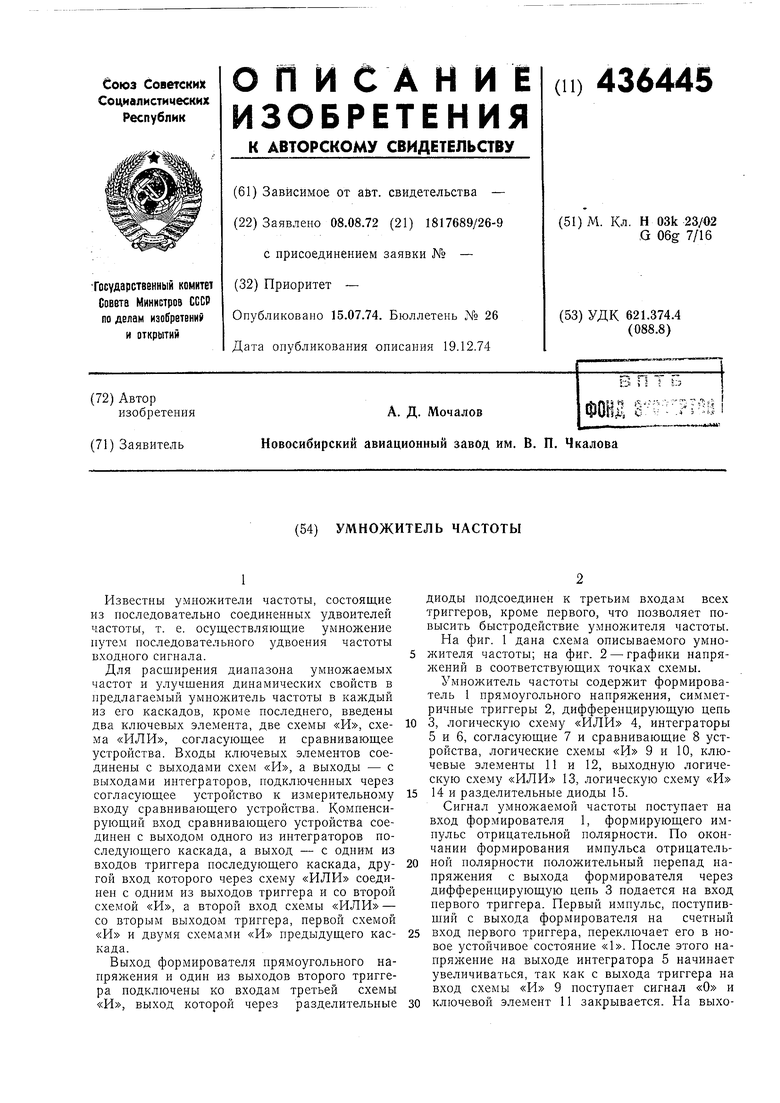

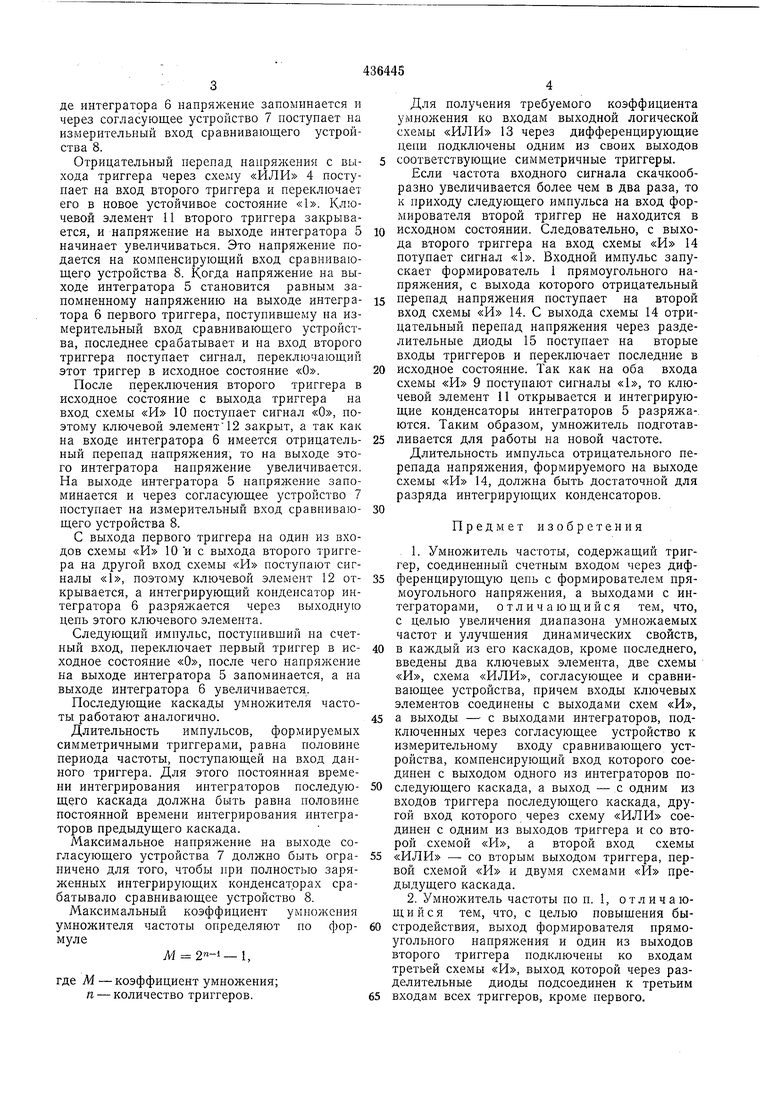

диоды подсоединен к третьим входам всех триггеров, кроме первого, что позволяет повысить быстродействие умножителя частоты. На фиг. 1 дана схема описываемого умножителя частоты; на фиг. 2 - графики напряжений в соответствующих точках схемы.

Умножитель частоты содержит формирователь 1 прямоугольного напряжения, симметричные триггеры 2, дифференцирующую цепь

3, логическую схему «ИЛИ 4, интеграторы 5 и 6, согласующие 7 и сравнивающие 8 устройства, логические схемы «И 9 и 10, ключевые элементы 11 и 12, выходную логическую схему «ИЛИ 13, логическую схему «И

14 и разделительные диоды 15.

Сигнал умножаемой частоты поступает на вход формирователя 1, формирующего импульс отрицательной полярности. Ио окончании формирования импульса отрицательной полярности положительный перепад напряжения с выхода формирователя через дифференцирующую цепь 3 подается на вход первого триггера. Первый импульс, поступивший с выхода формирователя на счетный

вход первого триггера, переключает его в новое устойчивое состояние «1. После этого напряжение на выходе интегратора 5 начинает увеличиваться, так как с выхода триггера на вход схемы «И 9 поступает сигнал «О и

ключевой элемент 11 закрывается. На выходе интегратора 6 напряжение запоминается и через согласующее устройство 7 поступает на измерительный вход сравнивающего устройства 8.

Отрицательный перепад напряжения с выхода триггера через cxeiviy «ИЛИ 4 поступает на вход второго триггера и переключает его в новое устойчивое состояние «1. Ключевой элемент 11 второго триггера закрывается, и напряжение на выходе интегратора 5 начинает увеличиваться. Это напрял ение подается на компенсирующий вход сравнивающего устройства 8. Когда напряжение на выходе интегратора 5 становится равным запомненному напряжению на выходе интегратора 6 первого триггера, поступившему на измерительный вход сравнивающего устройства, последнее срабатывает и на вход второго триггера поступает сигнал, переключающий этот триггер в исходное состояние «О.

После переключения второго триггера в исходное состояние с выхода триггера на вход схемы «И 10 поступает сигнал «О, поэтому ключевой элемент 12 закрыт, а так как на входе интегратора 6 имеется отрицательный перепад напряжения, то на выходе этого интегратора напряжение увеличивается. На выходе интегратора 5 напряжение запоминается и через согласующее устройство 7 поступает на измерительный вход сравнивающего устройства 8.

С выхода первого триггера на один из входов схемы «И 10 и с выхода второго триггера на другой вход схемы «И поступают сигналы «1, поэтому ключевой элемент 12 открывается, а интегрирующий конденсатор интегратора 6 разряжается через выходную цепь этого ключевого элемента.

Следующий импульс, поступивший па счетный вход, переключает первый триггер в исходное состояние «О, после чего напряжение на выходе интегратора 5 запоминается, а на выходе интегратора 6 увеличивается.

Последующие каскады умножителя частоты работают аналогично.

Длительность импульсов, формируемых симметричными триггерами, равна половине периода частоты, поступающей на вход данного триггера. Для этого постоянная времени интегрирования интеграторов последующего каскада должна быть равна половине постоянной времени интегрирования интеграторов предыдущего каскада.

Максимальное напряжение на выходе согласующего устройства 7 должно быть ограничено для того, чтобы при полностью заряженных интегрирующих конденсаторах срабатывало сравнивающее устройство 8.

Максимальный коэффициент умножения умножителя частоты определяют по формуле

Л 2«-1-1,

где М-коэффициент умножения; п - количество триггеров.

Для получения требуемого коэффициента

умножения ко входам выходной логической

схемы «ИЛИ 13 через дифференцирующие

цепи подключены одним из своих выходов

соответствующие симметричные триггеры.

Если частота входного сигнала скачкообразно увеличивается более чем в два раза, то к приходу следующего импульса на вход формирователя второй триггер не находится в

исходном состоянии. Следовательно, с выхода второго триггера на вход схемы «И 14 потупает сигнал «1. Входной импульс запускает формирователь 1 прямоугольного напряжения, с выхода которого отрицательный

перепад напряжения поступает на второй вход схемы «И 14. С выхода схемы 14 отрицательный перепад напряжения через разделительные диоды 15 поступает на вторые входы триггеров и переключает последние в

исходное состояние. Так как на оба входа схемы «И 9 поступают сигналы «1, то ключевой элемент 11 открывается и интегрирующие конденсаторы интеграторов 5 разряжаются. Таким образом, умножитель подготавливается для работы на новой частоте.

Длительность импульса отрицательного перепада напряжения, формируемого на выходе схемы «И 14, должна быть достаточной для разряда интегрирующих конденсаторов.

Предмет изобретения

. 1. Умножитель частоты, содержащий триггер, соединенный счетным входом через дифференцирующую цепь с формирователем прямоугольного напряжепия, а выходами с интеграторами, отличающийся тем, что, с целью увеличения диапазона умножаемых частот и улучшения динамических свойств,

в каждый из его каскадов, кроме последнего, введены два ключевых элемента, две схемы «И, схема «ИЛИ, согласующее и сравнивающее устройства, причем входы ключевых элементов соединены с выходами схем «И,

а выходы - с выходами интеграторов, подключенных через согласующее устройство к измерительному входу сравнивающего устройства, компепсирующий вход которого соединен с выходом одного из интеграторов последующего каскада, а выход - с одним из входов триггера последующего каскада, другой вход которого через схему «ИЛИ соединен с одним из выходов триггера и со второй схемой «И, а второй вход схемы

«ИЛИ - со вторым выходом триггера, первой схемой «И и двумя схемами «И предыдущего каскада.

2. Умножитель частоты по п. 1, отличающийся тем, что, с целью повышения быстродействия, выход формирователя прямоугольного напряжения и один из выходов второго триггера подключены ко входам третьей схемы «И, выход которой через разделительные диоды подсоединен к третьим

входам всех триггеров, кроме первого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1977 |

|

SU738125A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2002 |

|

RU2226695C1 |

| Аналого-дискретный интегратор | 1979 |

|

SU809250A2 |

| Н. Г. Горбушин и М. Л. Мирианашвили Институт медицинской радиологии АМН СССР | 1970 |

|

SU277419A1 |

| Устройство для измерения ускорений | 2022 |

|

RU2793846C1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| РАДИОПЕРЕДАЮЩАЯ СИСТЕМА ВРЕМЕННОЙ ОБЛАСТИ И РАДИОПЕРЕДАТЧИК | 1989 |

|

RU2105415C1 |

| Устройство для управления вентильным преобразователем | 1991 |

|

SU1774446A1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| Умножитель частоты | 1982 |

|

SU1058040A1 |

LJ

NjXJNJxrvJVJ

Г ГГГГГГ ГГГ г

hiDTimjinnrmjumr

т

L

Даты

1974-07-15—Публикация

1972-08-08—Подача