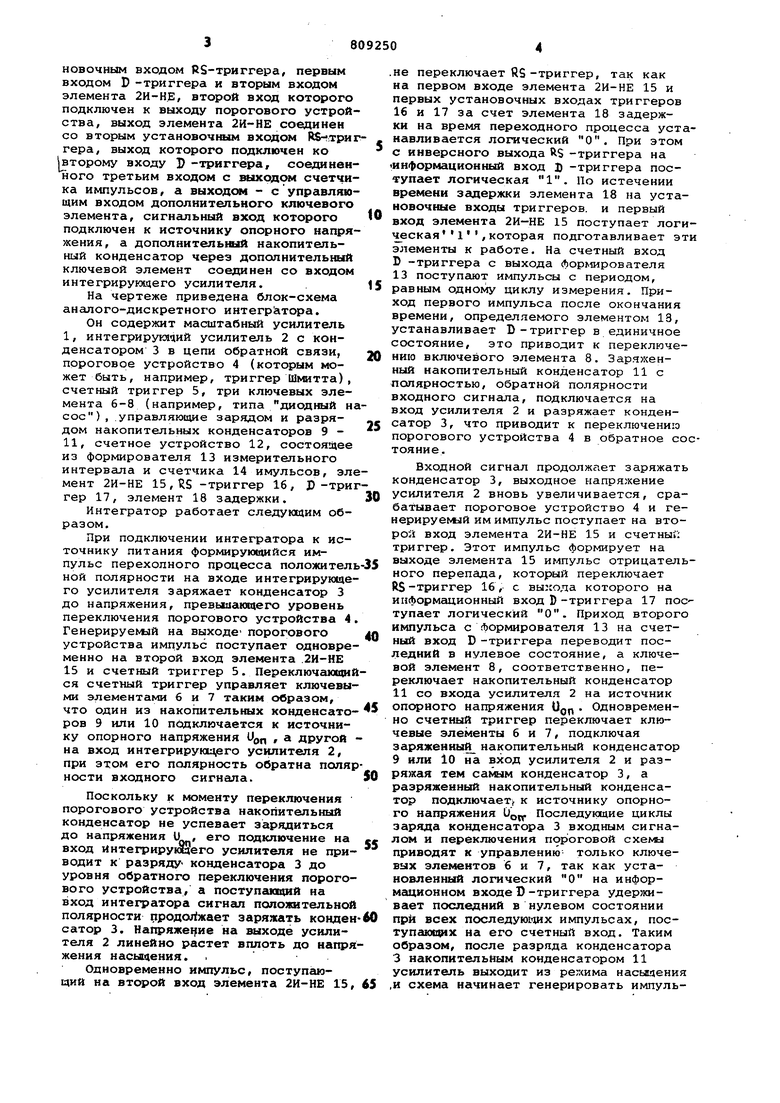

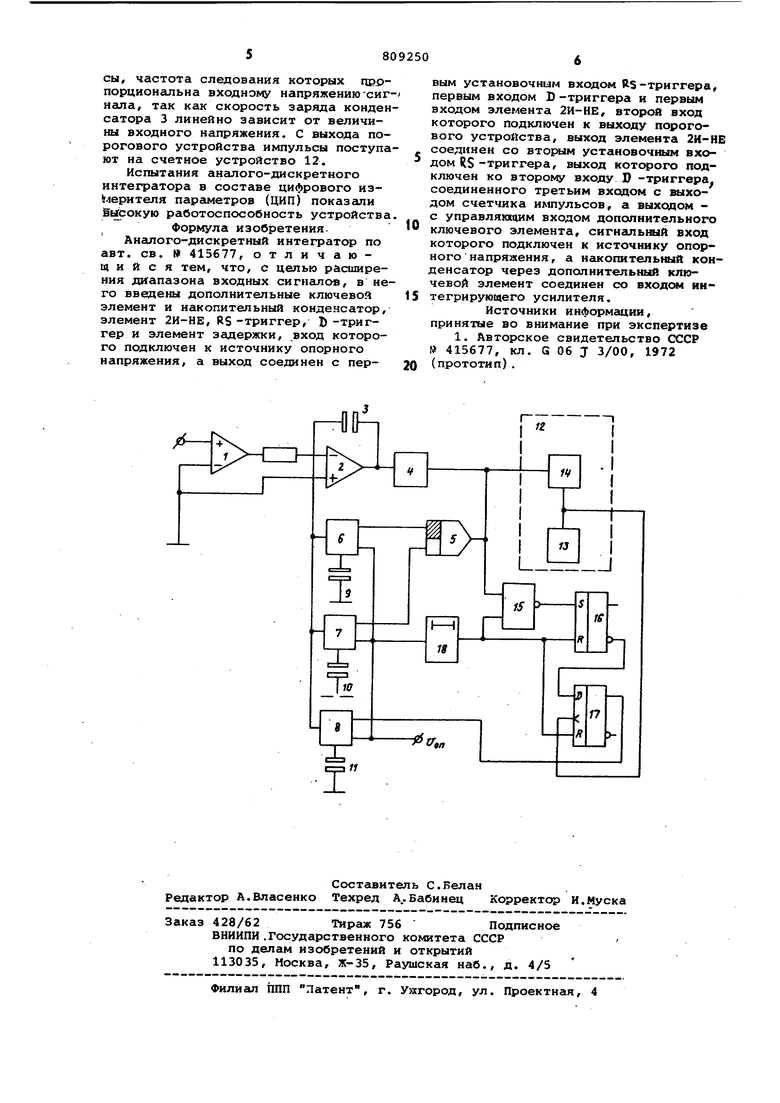

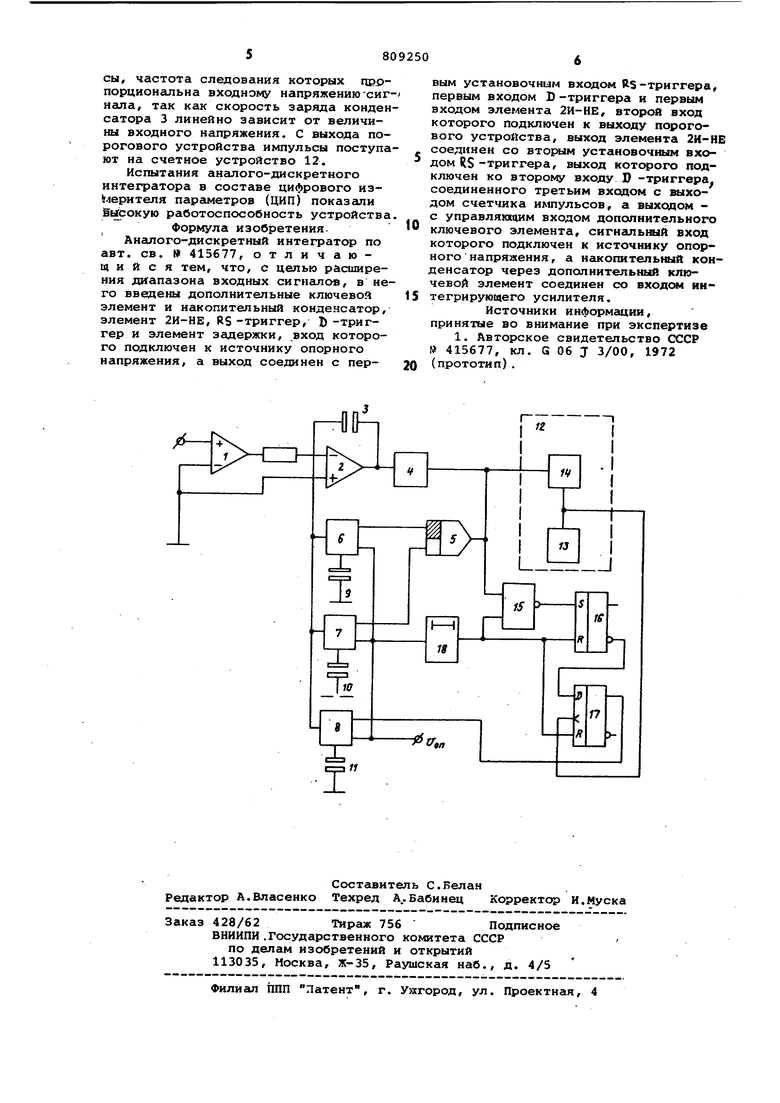

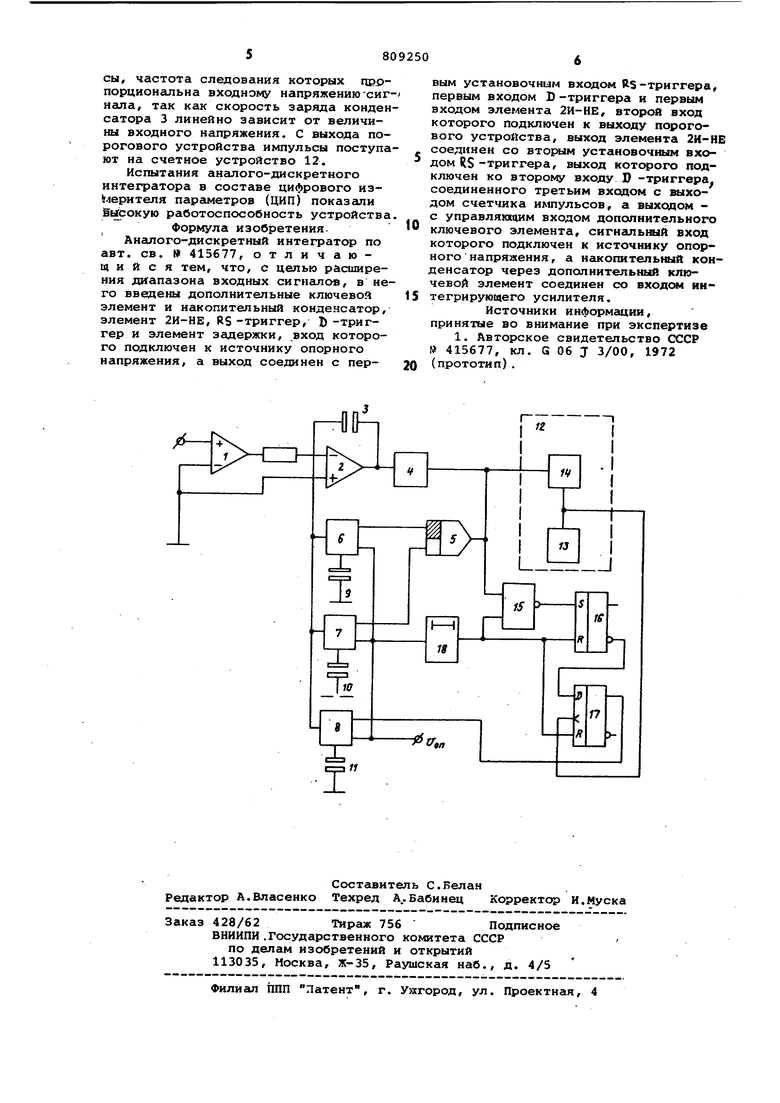

Изобретение относится к измерител ной технике и может быть использован например в цифровых измерителях пара метров хроматографа. По основному авт. св. № 415677 известен аналого-дискретный интегратор, который содержит последовательно соединенные интегрирующий усилитель, пороговое устройстве и счетчик импульсов, а также накопительйые конденсаторы, каждый из которых через соответствующую ключевую схему подключен ко входу интегрирующего усилителя, триггер, счетный вхо которого подключен к выходу порогевого устройства, а к двум выходам триггера подключены первые входы ключевых схем, вто( входы которых соединены с источником опорного напряжения fl . Недостатком известного интегратора является невозможность его работы при сигналах положительной полярности. Это объясняется тем, что в момен включения источника питания из-за присутствия емкостных цепей, на инвертирующем входе интегрирующего уси лителя формируется импульс переходно го процесса положительной полярности с максимсшьной энергией,который заря жает конденсатор обратной связи до напряжения, превшиающего порог срабатывания порогового ycTpcrflcTBa. К моменту переключения порогового устройства накопительные конденсаторы еще не успевают зарядиться и первое срабатывание одной и-з ключевых схем происходит вхолостую, т.е. мгшый заряд накопительного конденсатора не разряжает конденсатор обратной связи до уровня обратного перекл1эчения порогового устройства. Присутствующий на входе интегратора сигнгш положительной полярности продолжает заряжать конденсатор обратной связи до величины напряжения насЕяцения интегрирующего усилителя, а так как пороговое устройство не переключается, то интегратсч оказывается в иерабочем режиме. Цель предлагаемого изобретения расширение диапазона входных сигналов . Для этого в известный интегратор введены дополнительные ключевой элемент и накопительный конденсатор элемент 2И-НЕ, RS-триггер, D -триггер и эленюнт задержки, вход которого подключен к источнику опорного напряжения, а выход соединен с первым установочным входом RS-триггера, первым входом D -триггера и вторым входом элемента 2И-НЕ, второй вход которого подключен к выходу порогового устройства, выход элемента 2И-НЕ соединен со вторым установочным входом К8-,триг гера, выход которого подключен ко (второму входу D -триггера, соединенного третьим входом с выход.ом счетчика импульсов, а выходе - с управляющим входом дополнительного ключевого элемента, сигнальный вход которого подключен к источнику опорного напряжения, а дополннтельшлй накопительный конденсатор через дополнительный ключевой элемент соединен со входом интегрирующего усилителя. На чертеже приведена блок-схема аналого-дискретного интегратора. Он содержит масштабный усилитель I,интегрирукя-ций усилитель 2 с конденсатором 3 в цепи обратной связи, пороговое устройство 4 (которым может быть, например, триггер Шмитта), счетный триггер 5, три ключевых элемента 6-8 (например, типа диодный н сос), .управляющие зарядом и разрядом накопительных конденсаторов 9 II,счетное устройство 12, состоя Дее из формирователя 13 измерительного интервала и счетчика 14 имульсов, эл мент 2И-НЕ 15, Я5 -триггер 16, J)-три гер 17, элемент 18 задержки. Интегратор работает следующим образом. При подключении интегратора к источнику питания формирующийся импульс переходного процесса положител ной полярности на входе интегрирующе го усилителя заряжает конденсатор 3 до напряжения, превышающего уровень переключения порогового устройства 4 Генерируемый на выходе- порогового устройства импульс поступает одновре менно на второй вход элемента .2И-НЕ 15 и счетный триггер 5. Переключающи ся счетный триггер управляет ключевы ми элементами 6 и 7 таким образом, что один из накопительных конденсато ров 9 или 10 подключается к источнику опорного напряжения OQ , а другой на вход интегрирукхцего усилителя 2, при этом его полярность обратна поля ности входного сигнала. Поскольку к моменту переключения порогового устройства накопительный конденсатор не успевает зарядиться до напряжения U , его подключение на вход Интегрирующего усилителя не приводит к разряду- конденсатора 3 до уровня обратного переключения порого вого устройства, а поступгиощий на вход интегратора сигнал положительной полярности продо} жает заряжать коидеи сатор 3. Напряже{;ие на выходе усилителя 2 линейно растет вплоть до напря жения насыщения. Одновременно импульс, поступающий на второй вход элемента 2И-НЕ 15 не переключает RS-триггер, так как на первом входе элемента 2И-НЕ 15 и первых установочных входах триггеров 16 и 17 за счет элемента 18 задержки на время переходного процесса устанавливается логический О. При этом с инверсного выхода RS -триггера на информационный вход D -триггера поступает логическая 1. По истечении времени згщержки элемента 18 на установочные входы триггеров, и первый вход элемента 2И-НЕ 15 поступает логическая 1 , которая подготавливает эти элементы к работе. На счетный вход D -триггера с выхода формирователя 13 поступают импульсы с периодом, равным одному циклу измерения. Приход первого импульса после окончания времени, определяемого элементом 13, устанавливает В-триггер в единичное состояние, это приводит к переключению включевого элемента 8. Заряженный накопительный конденсатор 11 с полярностью, обратной полярности входного сигнала, подключается на вход усилителя 2 и разряжает конденсатор 3, что приводит к переключению порогового устройства 4 в обратное состояние. Входной сигнал продолжает заряжать конденсатор 3, выходное напряжение усилителя 2 вновь увеличивается, срабатывает пороговое устройство 4 и генерируемый им импульс поступает на второй вход элемента 2И-НЕ 15 и счетныП триггер. Этот импульс формирует на выходе элемента 15 импульс отрицательного перепада, который переключает RS-триггер 16, с выхода которого на информационный вход D-триггера 17 поступает логический О. Приход второго импульса с формирователя 13 на счетный вход D-триггера переводит последний в нулевое состояние, а ключевой элемент 8, соответственно, переключает накопительный конденсатор 11 со входа усилителя 2 на источник опорного напряжения UQ,, . Одновременно счетный триггер переключает ключевые элементы 6 и 7, подключая заряженный накопительный конденсатор 9 или 10 на вход усилителя 2 и разряжая тем самым конденсатор 3, а разряженный накопительный конденсатор подключает к источнику опорного напряжения . Последующие циклы заряда конденсатора 3 входным сигналом и переключения пор оговой cxewtj приводят к управлению только ключевых элементов 6 и 7, так как установленный логический О на информационном входеD-триггера удерживает последний в нулевом состоянии при всех последующих импульсах, поступаюсцих на его счетный вход. Таким образом, после разряда конденсатора 3 накопительным конденсатором 11 усилитель выходит из режима насыщения ,и схема начинает генерировать импульсы, частота следования которых nPi)порциональна входному напряжениюсигнала, так как скорость заряда конденсатора 3 линейно зависит от величины входного напряжения. С выхода порогового устройства импульсы поступают на счетное устройство 12.

Испытания аналого-дискретного интегратора в составе цифрового из г4ерителя параметров (ЦИП) показали высокую работоспособность устройства Формула изобретения.

Аналого-дискретный интегратор по авт. св. 415677, отличающийся тем, что, с целью расширения диапазона входных сигнсшов, в него введены дополнительные ключевой элемент и накопительный конденсатор, элемент 2И-НЕ, RS -триггер, Ь -триггер и элемент задержки, вход которого подключен к источнику опорного напряжения, а выход соединен с первым установочным входом RS-триггера, первым входом D-триггера и первым входом элемента 2И-НЕ, второй вход которого подключен к выходу порогового устройства, выход элемента 2И-НВ соединен со вторым установочным входом RS -триггера, выход которого подключен ко второму входу D -триггера. соединенного третьим вхадом с выходом счетчика импульсов, а выходом с управляххцим входом дополнительного

0 ключевого элемента, сигнальшлй вход которого подключен к источнику опорного напряжения , а накопительный конденсатор через дополнительный ключевой элемент соединен со входе ин5тегрирующего усилителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 415677, кл. G 06 J 3/00, 1972 (прототип).

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| АНАЛОГО-ДИСКРЕТНЫЙ ИНТЕГРАТОР | 1972 |

|

SU415677A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Аналого-дискретное интегрирующее устройство | 1985 |

|

SU1327128A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1628204A1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Измерительный преобразователь напряжения в частоту | 1984 |

|

SU1218467A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-11—Подача