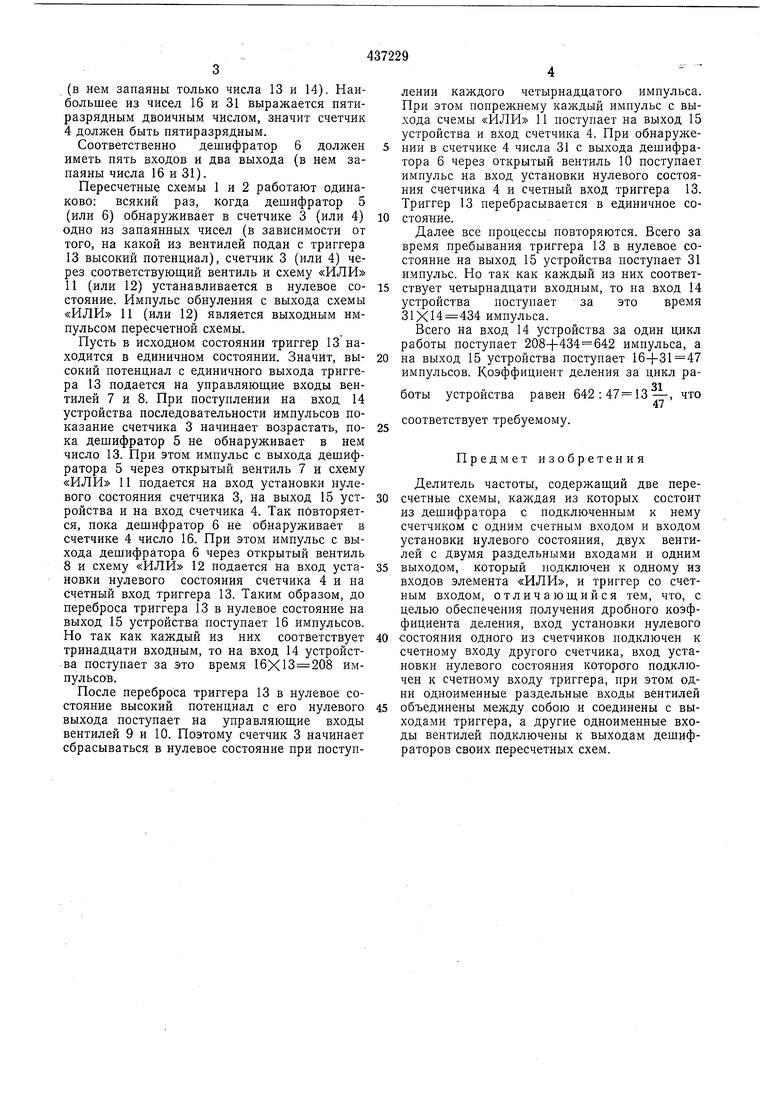

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частоты, измерителях частоты и других устройствах для деления частоты периодических импульсов в дробное число раз. Известен делитель частоты, содержащий две пересчетные схемы, каждая из которых состоит из дешифратора с подключенным к нему счетчиком с одним счетным входом и входом установки нулевого состояния, двух вентилей с двумя раздельными входами и одним выходом, который подключен к одному из входов элемента «ИЛИ, и триггер со счетным входом. Цель изобретения - обеспечение получекия дробного коэффициента деления частоты. Для этого вход установки нулевого состояния одного из счетчиков подключен к счетному входу другого счетчика, вход установки нулевого состояния которого подключен к счетному входу триггера, при этом одни одноименные раздельные входы вентилей объединены между собою и соединены с выходами триггера, а другие одноименные входы вентилей подключены к выходам дешифраторов своих пересчетных схем. На чертеже приведена функциональная схема предлагаемого делителя частоты. Он содержит пересчетные схемы 1 и 2, счетчики 3 и 4, дешифраторы 5 и 6, вентили 7-10, логические схемы «ИЛИ 11 и 12, триггер 13, вход 14 и выход 15. Работает делитель частоты следующим образом. В каждом из дешифраторов 5 и 6 запаяны по два числа: в дешифраторе 5 - числа А и (Л-)-1), в дешифраторе 6-числа (р-а) и а, где: Л - целая часть требуемого коэффициента деления; а - числитель его дробной части; Р - знаменатель его дробной части. Работа делителя частоты на примере реализации дробного коэффициента деления. Пусть требуемый коэффициент деления равен:/C 13f-. В этом случае: Л 13, Л + 1 14, Р-а 47-31 :16 Эти числа определяют основные параметры устройства. Наибольшее из чисел 13 и 14 выражается четырехразрядным двоичным числом, значит счетчик 3 должен быть четырехразрядным. Соответственно дешифратор 5 иметь четыре входа и два выхода

(в нем запаяны только числа 13 и 14). Наибольшее из чисел 16 и 31 выражается пятиразрядным двоичным числом, значит счетчик 4 должен быть пятиразрядным.

Соответственно дешифратор 6 должен иметь пять входов и два выхода (в нем запаяны числа 16 и 31).

Пересчетные схемы 1 и 2 работают одинаково: всякий раз, когда дешифратор 5 (или 6) обнаруживает в счетчике 3 (или 4) одно из запаянных чисел (в зависимости от того, на какой из вентилей подан с триггера 13 высокий потенциал), счетчик 3 (или 4) через соответствующий вентиль и схему «ИЛИ 11 (или 12) устанавливается в нулевое состояние. Импульс обнуления с выхода схемы «ИЛИ И (или 12) является выходным импульсом пересчетной схемы.

Пусть в исходном состоянии триггер 13 находится в единичном состоянии. Значит, высокий потенциал с единичного выхода триггера 13 подается на управляющие входы вентилей 7 и 8. При поступлении на вход 14 устройства последовательности импульсов показание счетчика 3 начинает возрастать, пока дешифратор 5 не обнаруживает в нем число 13. При этом импульс с выхода дешифратора 5 через открытый вентиль 7 и схему «ИЛИ 11 подается на вход установки нулевого состояния счетчика 3, на выход 15 устройства и на вход счетчика 4. Так повторяется, пока дешифратор 6 не обнаруживает в счетчике 4 число 16. При этом импульс с выхода дешифратора 6 через открытый вентиль 8 и схему «ИЛИ 12 подается на вход установки нулевого состояния счетчика 4 и на счетный вход триггера 13. Таким образом, до переброса триггера 13 в нулевое состояние на выход 15 устройства поступает 16 импульсов. Но так как каждый из них соответствует тринадцати входным, то на вход 14 устройства поступает за это время 16X13 208 импульсов.

После переброса триггера 13 в нулевое состояние высокий потенциал с его нулевого выхода поступает на управляющие входы вентилей 9 и 10. Поэтому счетчик 3 начинает сбрасываться в нулевое состояние при поступлении каждого четырнадцатого импульса. При этом попрежнему каждый импульс с выхода счемы «ИЛИ 11 поступает на выход 15 устройства и вход счетчика 4. При обнаружеНИИ в счетчике 4 числа 31 с выхода дешифратора 6 через открытый вентиль 10 поступает импульс на вход установки нулевого состояния счетчика 4 и счетный вход триггера 13. Триггер 13 перебрасывается в единичное состояние.

Далее все процессы повторяются. Всего за время пребывания триггера 13 в нулевое состояние на выход 15 устройства поступает 31 импульс. Но так как каждый из них соответствует четырнадцати входным, то на вход 14 устройства поступает за это время 31X14 434 импульса.

Всего на вход 14 устройства за один цикл работы поступает 208-|-434 642 импульса, а

на выход 15 устройства поступает 16-1-31 47 импульсов. Коэффициент деления за цикл ра31

боты устройства равен 642:47 13-, что

47

соответствует требуемому.

Предмет изобретения

Делитель частоты, содержащий две пересчетные схемы, каждая из которых состоит из дешифратора с подключенным к нему счетчиком с одним счетным входом и входом установки нулевого состояния, двух вентилей с двумя раздельными входами и одним

выходом, который подключен к одному из входов элемента «ИЛИ, и триггер со счетным входом, отличающийся тем, что, с целью обеспечения получения дробного коэффициента деления, вход установки нулевого

состояния одного из счетчиков подключен к счетному входу другого счетчика, вход установки нулевого состояния которого подключен к счетному входу триггера, при этом одни одноименные раздельные входы вентилей

объединены между собою и соединены с выходами триггера, а другие одноименные входы вентилей подключены к выходам дешифраторов своих пересчетных схем.

-К: -т-™1

1ЙЕЕЕШ:

LZIZJ

(Ai-1)

I

/5 У

I I ISEEHE:; J. i - I Г1 g j I f

KihW

LI

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1982 |

|

SU1082285A1 |

| Пересчетное устройство | 1982 |

|

SU1051698A1 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Делитель частоты | 1979 |

|

SU824447A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Устройство для деления число-импульсного кода на константу | 1981 |

|

SU1012443A1 |

| Устройство для преобразования средней частоты пачки импульсов | 1980 |

|

SU906000A1 |

Авторы

Даты

1974-07-25—Публикация

1972-03-27—Подача