Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен делитель частоты, содержащий два пересчетных блока, каждый из которых состоит из дешифратора с подключенным к нему счетчиком импульсов с одним счетным входом и входом установки нулевого состояния, двух вентилей с двумя входами и одним выходом, который подключен к одному из входов элемента ИЛИ, и триггер со счетным входом, вход установки нулевого состояния первого из счетчиков импульсов подключен к счетному входу второго счетчика импульсов, вход установки нулевого состояния которого подключен к счетному входу триггера, при этом первые входы вентилей соединены с выходами триггера, а вторые входы вентилей подключены к выходам дешифраторов своих пересчетных блоков.

Основным недостатком указанного делителя частоты является его сложность.

Наиболее близким по технической сущности является делитель частоты, содержащий счетчик импульсов на Т-триггерах с дополнительными R-входами, RS-триггер, инвертор и дешифратор, входы которого соединены с соответствующими выходами счетчика импульсов, а выход - с S-входом RS-триггера, инверсный выход которого соединен с R-входом счетчика импульсов, шина входной частоты соединена со счетным входом счетчика импульсов и через инвертор с R-входом - RS-триггера.

Указанный делитель частоты отличается простотой, но имеет следующие недостатки. Во-первых, наличие помех на выходах во время сброса в исходное состояние счетчика импульсов после переключения RS-триггера, которые могут формироваться на любом из выходов счетчика импульсов в зависимости от величины коэффициента деления и вызвать нарушение функционирования устройства, подключенного к выходу делителя частоты; во-вторых, малое количество реализуемых коэффициентов деления при заданном числе разрядов счетчика и неравномерность их распределения по диапазону; в-третьих, невозможность получения коэффициента деления меньше 2; в-четвертых, необходимость использования в делителе частоты R-входа счетчика импульсов.

Целью изобретения является расширение функциональных возможностей.

Поставленная цель достигается тем, что в делитель частоты, содержащий шину входной частоты, счетчик импульсов и дешифратор, входы которого соединены с соответствующими выходами счетчика импульсов, введен сумматор по модулю два, первый вход которого соединен с шиной входной частоты, второй - с выходом дешифратора, а выход подключен к счетному входу счетчика импульсов.

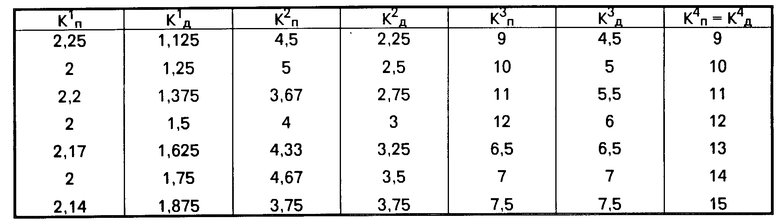

На фиг.1 представлена функциональная схема делителя частоты на примере делителя частоты на 10 с дешифратором на основе элементов И-НЕ; на фиг.2 - функциональная схема делителя частоты на примере делителя частоты на 10 с дешифратором на основе сумматора по модулю два.

Делитель частоты содержит счетчик 1 импульсов (4-х разрядный для делителя частоты на 10), дешифратор 2, входы которого соединены с соответствующими выходами счетчика 1 и сумматор 3 по модулю два, первый вход которого соединен с шиной 4 входной частоты, второй - с выходом дешифратора 2, а выход - со счетным входом счетчика 1.

Для исключения влияния задержек переключения триггеров счетчика 1 на функционирование делителя частоты в дешифраторе 2 при необходимости может быть включен фильтр 5, выполненный, например, в виде резистивно-емкостной цепи.

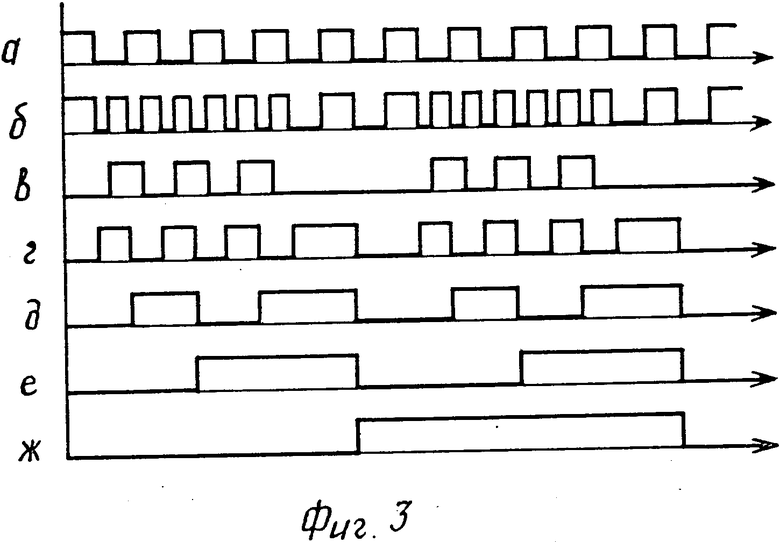

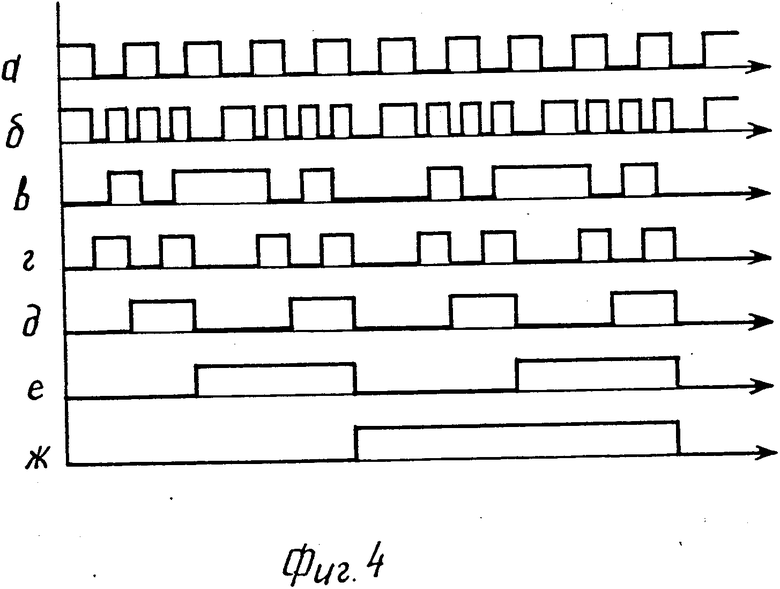

На фиг. 3 и 4 приведены диаграммы напряжений в различных точках делителей фиг.1 и 2 соответственно:

на шине входной частоты 4 - точка а;

на выходе сумматора 3 - точка б;

на выходе дешифратора 2 - точка в;

на выходах первого, второго, третьего и четвертого разрядов счетчика - точки г,д,е,ж соответственно.

Делитель частоты (фиг.1) работает следующим образом.

В исходном состоянии на выходах счетчика 1 и дешифратора 2 присутствует уровень "0", на шине 4 и на выходе сумматора 3 - уровень "1". При поступлении переднего фронта входного импульса в виде отрицательного перепада напряжения на шину 4 на выходе сумматора 3 появляется отрицательный перепад напряжения, поступающий на счетный вход счетчика 1 и вызывающий переключение триггера первого разряда. При этом на соответствующем входе дешифратора 2 и с некоторой задержкой на его выходе и на выходе сумматора 3 появляется положительный перепад напряжения.

При поступлении заднего фронта входного импульса в виде положительного перепада напряжения на шину 4 на выходе сумматора 3 появляется отрицательный перепад напряжения, вызывающий переключение триггеров первого и второго разрядов счетчика 1.

При этом происходит изменение потенциалов на соответствующих входах дешифратора 2 и с некоторой задержкой на его выходе и на входе сумматора 3.

Далее работа делителя частоты происходит аналогичным образом. При этом триггер первого разряда переключается от обоих фронтов первого, второго и третьего импульсов и от передних фронтов четвертого и пятого импульсов, всего 8 раз, что обеспечивает коэффициент деления делителя, равный 10 - по выходу четвертого разряда, равный 5 - по выходу третьего разряда, равный 2,5 - по выходу второго разряда и равный 1,25 - по выходу первого разряда счетчика 1.

Делитель частоты (фиг.2) работает аналогичным образом. При этом триггер первого разряда счетчика 1 переключается 8 раз при поступлении пяти входных импульсов: от обоих фронтов первого, второго и четвертого импульсов, от заднего фронта третьего импульса и от переднего фронта пятого импульса.

Таким образом, устройство, реализованное по обеим схемам дешифратора, нормально функционирует, обеспечивая указанные выше коэффициенты деления.

По сравнению с базовым образцом, в качестве которого взят прототип, заявленный делитель частоты имеет следующие преимущества:

а) отсутствие необходимости использования R-входа счетчика импульсов;

б) отсутствие помех на выходах устройства;

в) увеличение количества реализуемых коэффициентов деления;

г) повышение равномерности распределения коэффициентов деления по диапазону;

д) возможность получения коэффициентов деления менее 2.

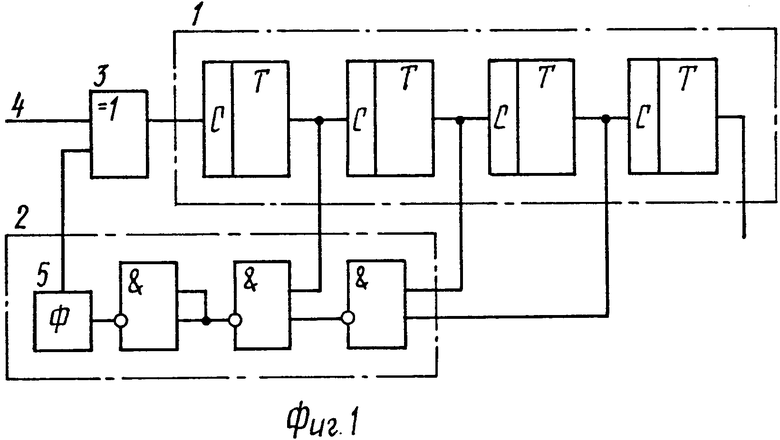

Три последних преимущества поясняются таблицей, в которой приведены коэффициенты К1, К2, К3, К4 деления частоты входных импульсов соответственно по выходу первого, второго, третьего и четвертого разрядов четырехразрядного двоичного счетчика импульсов для прототипа Кп и данного устройства Кд; при этом в каждой строке приведены коэффициенты деления для одного из семи возможных вариантов схемы с недвоичным коэффициентом деления.

Из таблицы видно, что количество реализуемых недвоичных коэффициентов деления составляет для прототипа 20, а для данного устройства - 28, а также видно более равномерное распределение коэффициентов деления по диапазону и наличие четырех значений коэффициентов деления меньше 2.

Перечисленные преимущества существенно расширяют функциональные возможности делителей частоты в составе разрабатываемой аппаратуры.

Таким образом, новая совокупность признаков позволяет производить коммутацию фазы импульсов на счетном входе счетчика импульсов во время его работы, за счет чего увеличить количество переключений триггеров счетчика импульсов при одинаковом с прототипом числе входных импульсов, и таким образом, уменьшить коэффициент деления, при этом сохраняется последовательность переключения триггеров счетчиков импульсов во время его работы, устраняется необходимость принудительного его сброса в исходное состояние, а следовательно, устраняется причина возникновения помех на выходах устройства и устраняется необходимость использования R-входа счетчика импульсов. Одновременно достигается увеличение числа реализуемых коэффициентов деления, повышается равномерность распределения их по диапазону и появляется возможность получения коэффициентов деления менее 2.

Кроме того, необходимо отметить существенное упрощение синтеза схемы делителя частоты по заданному коэффициенту деления, поскольку коэффициенты деления по выходам всех разрядов счетчика импульсов связаны двоичной зависимостью.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1983 |

|

SU1162368A1 |

| Умножитель частоты следования импульсов | 1987 |

|

SU1539980A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU980291A1 |

| Филлипов А.Г., Белкин О.С | |||

| Проектирование логических узлов ЭВМ | |||

| М., Сов.радио, 1974, рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1994-11-30—Публикация

1982-03-05—Подача