1

Изобретение отпосится к дискретной технике и может быть использовано в схемах аппаратуры передачи данных, а также для создания многоканальной анпаратуры телефонной связи при уплотнении посредством импульсно-кодовой модуляции (ИКМ).

Известна схема преобразователя, в которой двоичная последовательность импульсов подается на логический элемент, управляюнл,ий двумя логическими и двумя формирующими элементами.

Недостаток известной схемы заключается в том, что опа сложна и имеет относительно низкую надежность. Кроме того, известная схема может работать только при единственном представлении (отображении) единиц и нулей в двоичной кодовой последовательности импульсов, поступающей на вход преобразователя. Изменение нолярности импульсов, отображающих (представляющих) единицу, а также общее изменение снособа нредставления единицы и цуля в двоичной кодовой последовательности нриводит к необходимое изменения схемы нреобразователя.

Целью изобретения является упрощение схемы, новышение надежности ее работы и обеснечение возможности подачи па вход преобразователя двоичной кодовой носледовательности с любылг из вариантов представления единицы и НУЛЯ соответственно либо положительным импульсом и отсутствием импульса, либо отрицательным импульсом и отсутствиел импульса, либо отсутствием импульса и положительным импульсом, либо отсутствием импульса и отрицательным импульсом.

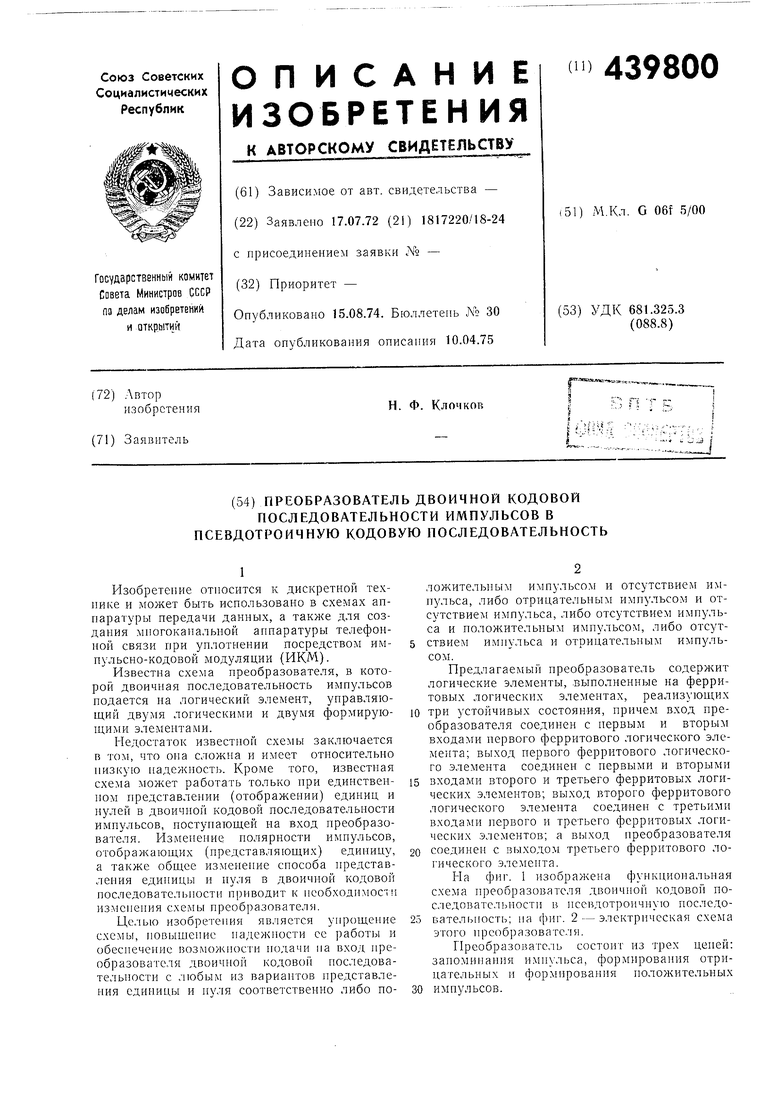

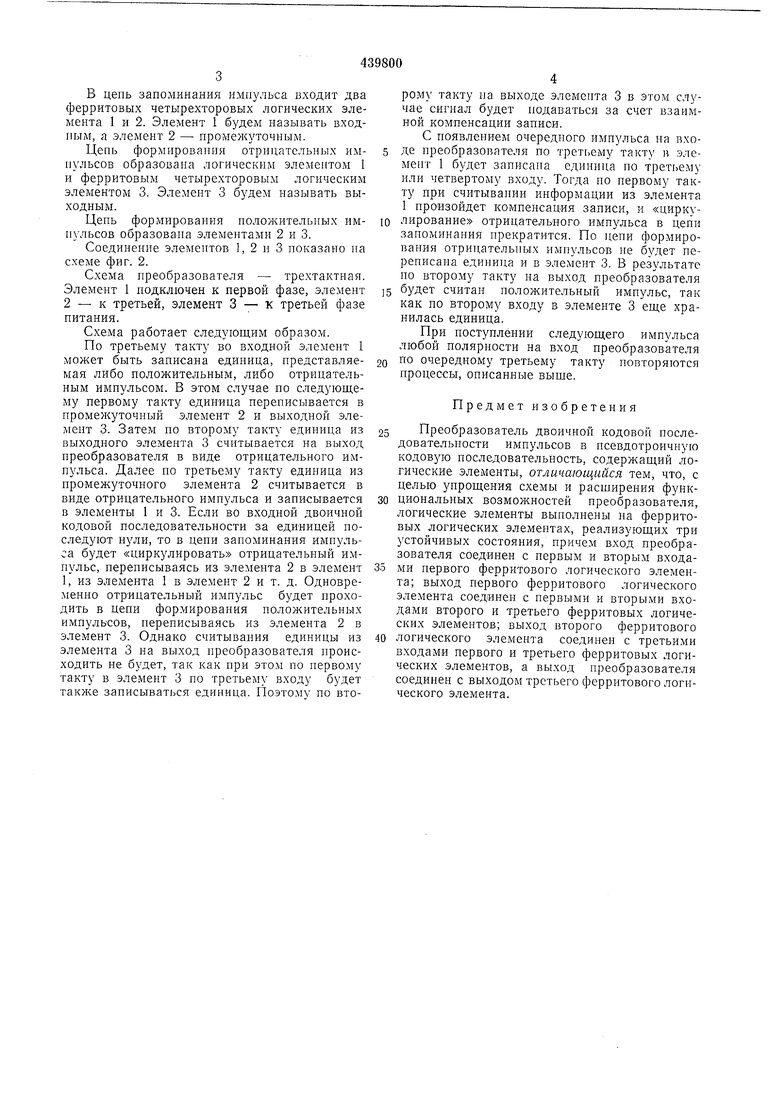

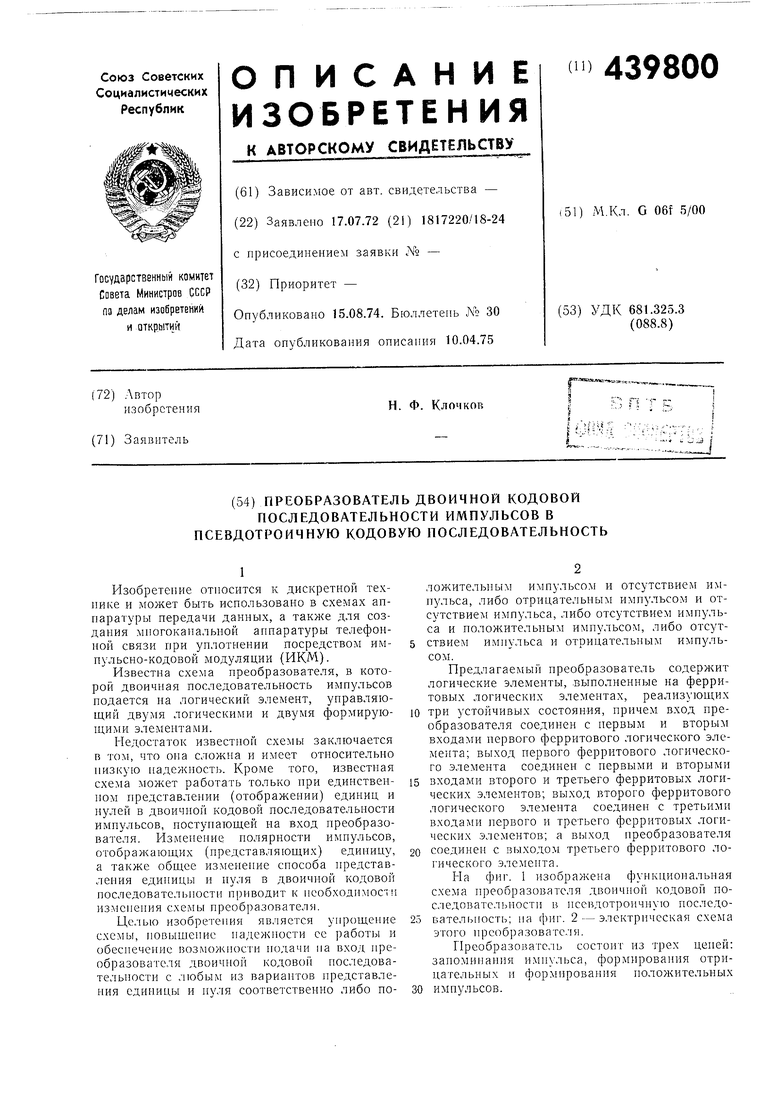

Предлагаемый преобразователь содержит логические элементы, выполненные на ферритовых логических элементах, реализующих три устойчивых состояния, причем вход преобразователя соединен с первым и вторьт входами первого ферритового логического элемента; выход первого ферритового логического элемента соединен с первыми и вторыми входами второго и третьего ферритовых логических элементов; выход второго ферритового логического элемента соединен с третьими входами нервого и третьего ферритовых логических элементов; а выход преобразователя соединен с выходом третьего ферритового логического элемента.

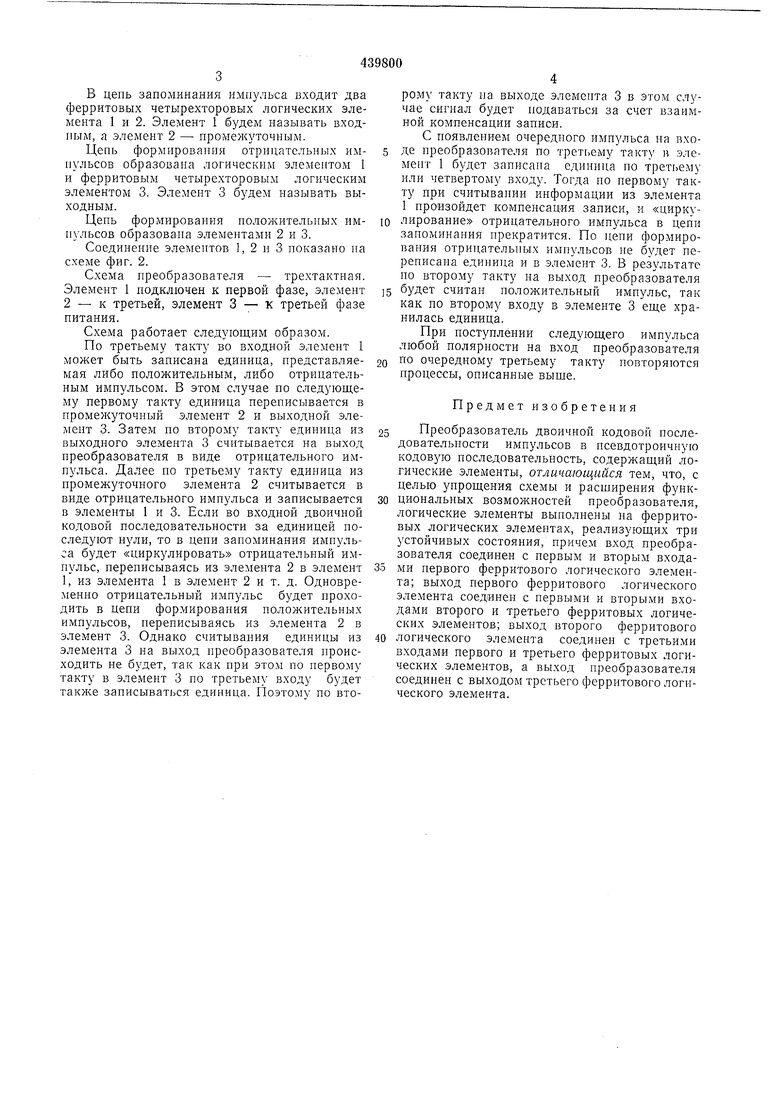

На фиг. 1 изображена функциональная схема преобразователя двоичной кодовой последовательности в нсевдотроичную после.довательпость; па фиг. 2 - электрическая схема этого нреобразовате.тя.

Г1реобразо1 атель состоит из трех цецей: заноминания имнульса, формирования отрицательных и формирования ноложительных импульсов.

В цепь запоминания импульса входит два ферритовых четырехторовых логических элемента 1 и 2. Элемент 1 будем называть входпым, а элемент 2 - промежуточным.

Цепь формпроваппя отрицательных импульсов образована логическим элементом 1 и ферритовым четырехторовым логическим элементом 3. Элемент 3 будем называть выходным.

Цепь формирования положительных импульсов образоваиа элементами 2 и 3.

Соединение элементов 1, 2 и 3 показано па схеме фпг. 2.

Схема преобразователя - трехтактиая. Элемент 1 подключен к первой фазе, элемент 2 - к третьей, элемент 3 - к третьей фазе питания.

Схема работает следующим образом.

По третьему такту во входной элемент 1 может быть записана единица, представляемая либо положительным, либо отрицательным импульсом. В этом случае по следующему первому такту единица переписывается в промежуточный элемент 2 и выходной элемент 3. Затем по второму такту единица из выходного элемента 3 считывается па выход преобразователя в виде отрицательного импульса. Далее по третьему такту единица из промежуточного элемента 2 считывается в виде отрицательного импульса и записывается в элементы 1 и 3. Если во входной двоичной кодовой последовательности за единицей последуют пули, то в цепи запоминания импульса будет «циркулировать отрицательный импульс, переписываясь из элемепта 2 в элемент 1, из элемента 1 в элемент 2 и т. д. Одновременно отрицательный импульс будет проходить в цепи формирования положительных импульсов, переписываясь из элемента 2 в элемент 3. Однако считывания единицы из элемента 3 на выход преобразователя происходить не будет, так как при этом по первому такту в элемент 3 по третьему входу будет также записываться единица. Поэтому по второму такту па выходе элемента 3 в этом случае сигнал будет подаваться за счет взаимной компенсации записи.

С иоявлепием очередного импульса па входе преобразователя по третьему такту в элеMeirr 1 будет записана единица по третьему или четвертому входу. Тогда ио первому такту при считывании информации из элемента 1 произойдет компенсация записи, и «циркулирование отрицательного импульса в цепи запоминания прекратится. По цепи формирования отрицательиых импульсов не будет переписаиа единица и в элемент 3. В результате ио второму такту на выход преобразователя

будет считан положительный импульс, так как по второму входу в элементе 3 еще хранилась единица.

При поступлеиии следующего импульса любой полярности на вход преобразователя

по очередному третьему такту повторяются процессы, описанные выще.

Предмет изобретения

Преобразователь двоичной кодовой последовательности импульсов в псевдотроичпую кодовую последовательность, содержащий логические элементы, отличающийся тем, что, с целью уирощения схемы и расширения функциональных возможностей преобразовате.пя, логические элементы выполнены на ферритовых логических элементах, реализующих три устойчивых состояиия, причем вход преобразователя соединен с первым и вторым входами первого ферритового логического элемента; выход первого ферритового логического элемента соединен с первыми и вторыми входами второго и третьего ферритовых логических элементов; выход второго ферритового

логического элемента соединен с третьими входами первого и третьего ферритовых логических элементов, а выход преобразователя соединен с выходом третьего ферритового логического элемента.

Вюд

ч:

+

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения операции "конъюнкции на три входа" на ферритферритовых логических элементах | 1981 |

|

SU966910A1 |

| Устройство для выполнения операции "конъюнкция на три входа" на феррит-ферритовых логических элементах | 1980 |

|

SU898619A1 |

| Логический перемножитель по модулю три на феррит-ферритовых элементах | 1977 |

|

SU692090A1 |

| Преобразователь двоичного кода в троичный код 1,0,1 | 1978 |

|

SU750477A1 |

| Преобразователь двоичного кодаВ ТРОичНый КОд 1,0,1 | 1979 |

|

SU796838A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1978 |

|

SU741261A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1979 |

|

SU773615A1 |

| Устройство для формирования последовательностей импульсов | 1984 |

|

SU1182638A1 |

| Преобразователь перемещений в код | 1978 |

|

SU763939A1 |

-о Вопод

+

Т

о Вымд

)

вход

Фиг Z

Авторы

Даты

1974-08-15—Публикация

1972-07-17—Подача