1

Изобретение относится к технике передачи дискретных сообщений в,условиях воздействия сильных импульсных помех. Применение устройства особенно целесообразно при -использовании методов, основанных на передаче дешифрируемой на приема синхрогруппы (маркерной группы) в случае довольно большой вероятности сбоя при ее дешифрации..

Известны устройства цикловой синхронизации, осуш;ествляющие параллельный поиск синхрогруппы на всех позициях .цикла. Однако существенным недостатком этих устройств является их большая аппаратурная сложность. Известные устройства цикловой синхронизации, реализующие последовательный поиск синхрогруппы и работающие в условиях интенсивных импульсных помех, как правило, не обеспечивают высокой помехоустойчивости, особенно в переходном режиме.

Целью изобретения является повышение помехоустойчивости в переходном и в установившемся режимах устройством .цикловой -синхронизации, работающим по принципу последовательного поиска синхрогрупп.

Сущность изобретения заключается в том, что в устройстве первый выход блока анализа, -соединенный с первыми входами двух схем -«И, и второй выход блока анализа подключены соответственно к нервому и второму входам блока определения сбоев, управляющ-ий

вход которого соединен с выходом дешифратора нулевого состойния. Третий вход блока оц.ределений сбоев соединен с выходом управляемого делителя и входом блока анализа. Первый и в горой выходы блока определения сбоев подключены соответственно ко второму входу управляемого делителя и ко входу обратного счета реверсивного счетчика. Вторые входы схем «И подключе-ны соответственно к первому и второму выходам триггера индикации. Выходы схем «И соединены соответственно со входом установки и входом прямого счета реверсивного счетчика.

В устройстве блок определения сбоев выполнен с применением схем «И, «ИЛИ, «НЕ и триггера. Первый вход триггера подключен через схему «ИЛИ к первому входу блока. Второй вход схемы «ИЛИ соединен со вторым выходом блока и выходом первой схемы «И. Второй вход блока подключен ко второму входу триггера, выход которого подключен к первым входам первой и второй схем «И, вторые входы которых подсоединены к третьему входу блока, управляющий вход которого подключен к третьему входу первой схемы «И и через схему «НЕ - к третьему входу второй схемы «И, выход которой соединен с первым выходом блока.

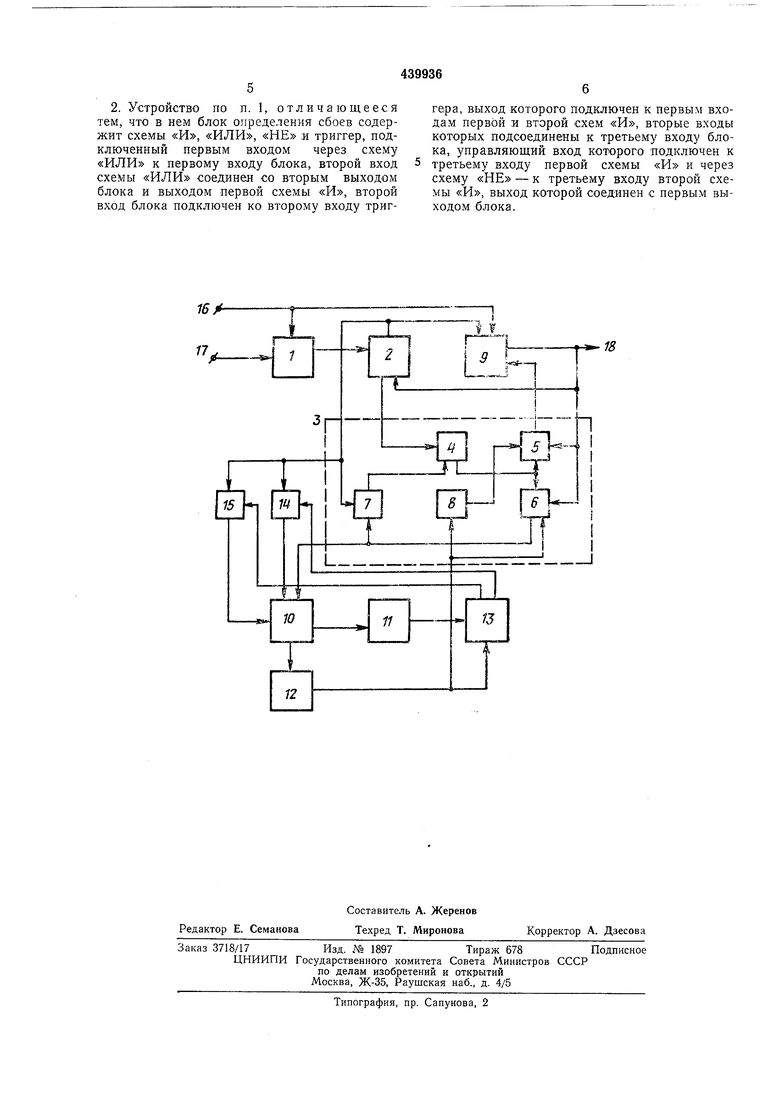

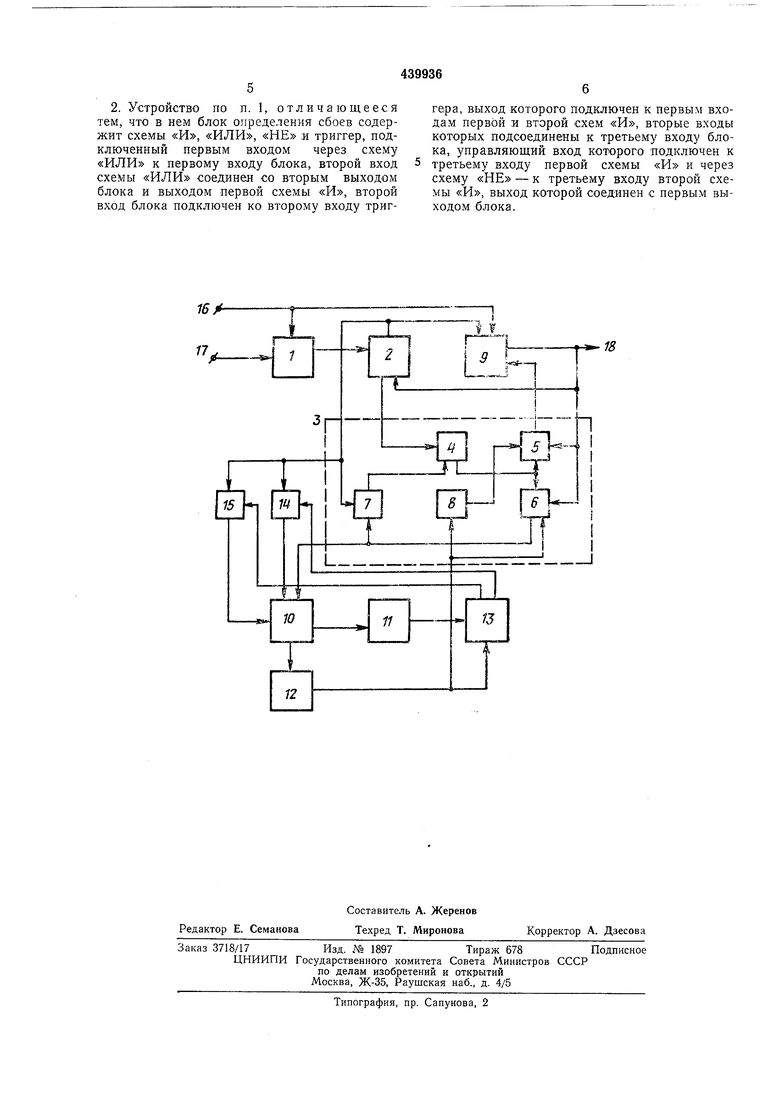

На чертеже представлена схема устройства.

Предлагаемое устройство содержит дешифратор 1 синхрогруппы, блок 2 анализа, блок определения сбоев 3, содержащий триггер 4, схемы «И 5 и 6, схему «ИЛИ 7, схему «НЕ 8, управляемый делитель 9, реверсивный счетчик 1G, дешифраторы 11 и 12 заданного и нулевого состояний, триггер индикации 13, схемы «И 14 и 15, входы 16 и 17 и выход 18 устройства.

На входы дешифратора синхрогрупны 1 подаются тактовые .импульсы (вход 16) и принимаемый сигнал (вход 17).

Импульсы с выхода дешифратора 1, опознающего синхрогруппу Б информационном сигнале и дешифрирующего ее, поступают на блок 2, осуществляюш;ий анализ временного положенин откликов дешифратора 1. Блок 2 определяет местоположение импульсов с дешифратора, при этом критерием отличия периодически следующих откликов и откликов внутри интервала периодичности служит первый отклик с выхода денгифратора, который принимается за предполагаемую позицию начала цикла.

Имцульс, соответствующий первому отклику, запускает управляемый делитель 9 тактовой частоты до частоты циклов, а также через схему «И 14 поступает на вход прямого счета реверсивного счетчика 10. Появивщийся вслед за этим внутри цикла хотя бы один отклик с дешифратора синхрогруппы поступает на выход откликов внугри интервала периодичности блока 2 и далее на переброс триггера 4 блока определения сбоев 3.

Второй периодически следующий отклик с дешифратора синхрогруппы (при его наличии) возвращает через схему «ИЛИ 7 триггер в исходное состояние и поступает на вход прямого счета реверсивного счетчика 10. Если второй отклик с дешифратора отсутствует, то цикловой импульс с выхода управляемого делителя 9 через схему «И 6 поступает на входы обратного счета реверсивного счетчика 10 и переброса триггера 4 через схему «ИЛИ 7. В случае, когда после появления импульса, соответствующего первому отклику, внутри цикла нет ни одного импульса с дешифратора синхрогруппы и появился второй периодически следующий отклик, то он проходит на вход прямого счета реверсивного счетчика.

(При отсутствии второго периодически следующего отклика на реверсивном счетчике сохраняется предыдущее записанное число, и вновь ведется просмотр следующего интервала внутри цикла. Если в результате счета реверсивный счетчик досчитал до нулевого состояния, то цикловый импульс с выхода управляемого делителя 9 проходит через схему «И 5, открываемую по команде с дешифратора 12 через схему «НЕ 8 и останавливает управляемый делитель, который вновь запустится первым (очередным) откликом с дешифратора 1.

Таким образом, триггер 4 в случае наличия импульса внутри интервала нериодичности и отсутствия очередного периодически следующего отклика с дешифратора синхрогруппы дает разрешение на прохождение цикловых импульсов на вход обратного счета реверсивного счетчика 10 при любом состоянии последнего, кроме нулевого, а при списывании реверсивного счетчика в ноль - также и на остановку управляемого делителя 9. Если в результате счета реверсивный счегчик досчитал до заданной цифры, триггер индикации 13 состояния синхронизма по команде с дешифратора 11 переключается в положение, соответствующее установившемуся режиму устройстства, а сам реверсивный счетчик переходит в состояние, соответствующее максимально возможной цифре прямого счета. Теперь все периодически следующие отклики поступают через схему «И 15 на вход установки реверсивного счетчика, переключая последний с любой цифры, кроме нулевой, в состояние, соответствующее максимально возможной цифре прямого счета. Поступление импульсов на вход обратного счета реверсивного счетчика происходит аналогично вышеописанному в переходном режиме.

При списании реверсивного счетчика до нуля триггер индикации 13 по команде с дешифратора 12 переходит в положение, соответствующее переходному режиму устройства, при этом также происходит остановка управляемого делителя 9, и вновь начинается поиск истинной позиции начала цикла.

Предмет изобретения

1. Устройство для синхронизации по циклам, содержащее последовательно соединенные дешифратор синхрогруппы, блок анализа и управляемый делитель, выход которого подключен к выходу устройства, первый вход устройства соединен с первыми входами управляемого делителя и дешифраюра синхрогруппы, второй вход которого подключен ко второму входу устройства, схемы «И, блок определения сбоев и реверсивный счетчик с подключенным к нему через дещифраторы нулевого и заданного состояний триггером индикации, отличающееся тем, что, с целью повышения помехоустойчивости, в устройстве первый выход блока анализа, соединенный с первыми входами двух схем «И, и второй выход блока анализа подключены соответственно к первому и второму входам блока определения сбоев, управляющий вход которого соединен с выходом дешифратора нулевого состояния, третий вход блока определения сбоев соединен с выходом управляемого делителя и входом блока анализа, первый и второй выходы блока определения сбоев подключены соответственно ко второму входу управляемого делителя и ко входу обратного счета реверсивного счетчика, вторые входу схем «И подключены соответственно к первому и второму выходам триггера индикации, выходы схем «И соединены соответственно со входом установки и входом прямого счета реверсивного счетчика.

2. Устройство по п. 1, отличающееся тем, что в нем блок определения сбоев содержит схемы «И, «ИЛИ, «НЕ :и триггер, подключенный первым входом через схему «ИЛИ к первому входу блока, второй вход схемы «ИЛИ соединен со вторым выходом блока и выходом первой схемы «И, второй вход блока подключен ко второму входу триггера, выход которого подключен к первым входам первой и второй схем «И, вторые входы которых подсоединены к третьему входу блока, управляющий вход которого подключен к третьему входу первой схемы «И и через схему «НЕ - к третьему входу второй схемы «И, выход которой соединен с первым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| Приемное устройство циклового фазирования | 1983 |

|

SU1085006A1 |

| Устройство формирования сигнала кадровойСиНХРОНизАции | 1979 |

|

SU843301A1 |

| Устройство для синхронизации по циклам | 1991 |

|

SU1811019A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

16

-;

Авторы

Даты

1974-08-15—Публикация

1972-10-24—Подача