1

Изобретение относится к асинхронным оДноканальным системам управления вентильными преобразователями и содержит общий управляемый генератор, частота которого является функцией сигнала ошибки, и распределитель импульсов по фазам вентильного преобразователя.

Системы такого типа охватываются обратной связью по регулируемому выходному параметру преобразователя (напряжению, току, скорости двигателя и т. д.), позволяющей осуществлять астатическое регулирование параметра без применения дополнительных регуляторов.

Предложенное устройство отличается тем, что оно снабжено вторым интегратором со своей цепью сброса, подключенным параллельно -первому интегратору, причем цепь сброса через логический элемент ИЛИ связана с выходами распределителя импульсов.

Это позволяет исключить ошибки управления, возникающие из-за размыкания системы на время сброса интегратора.

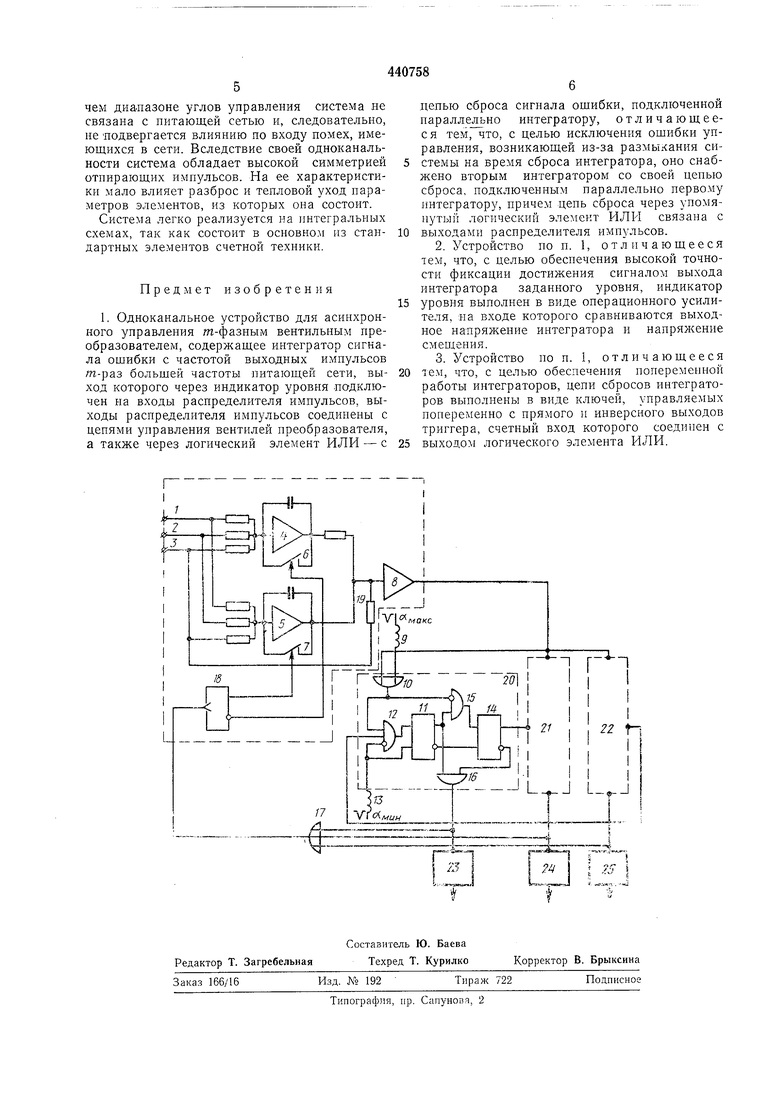

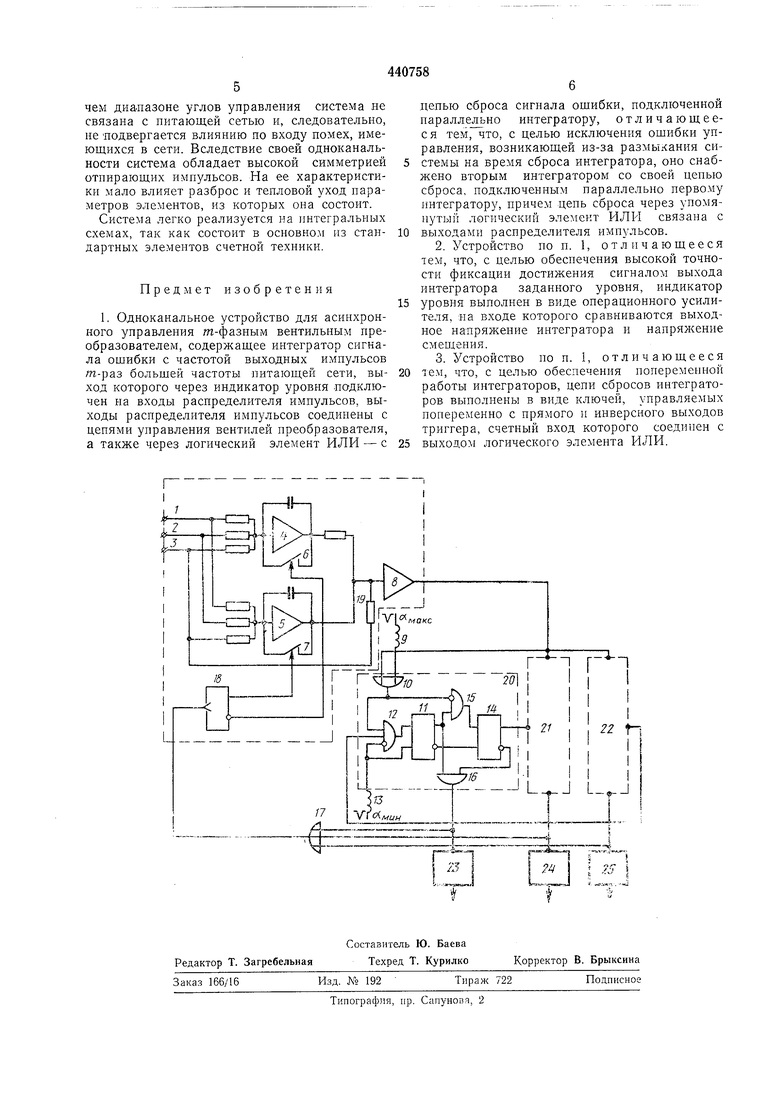

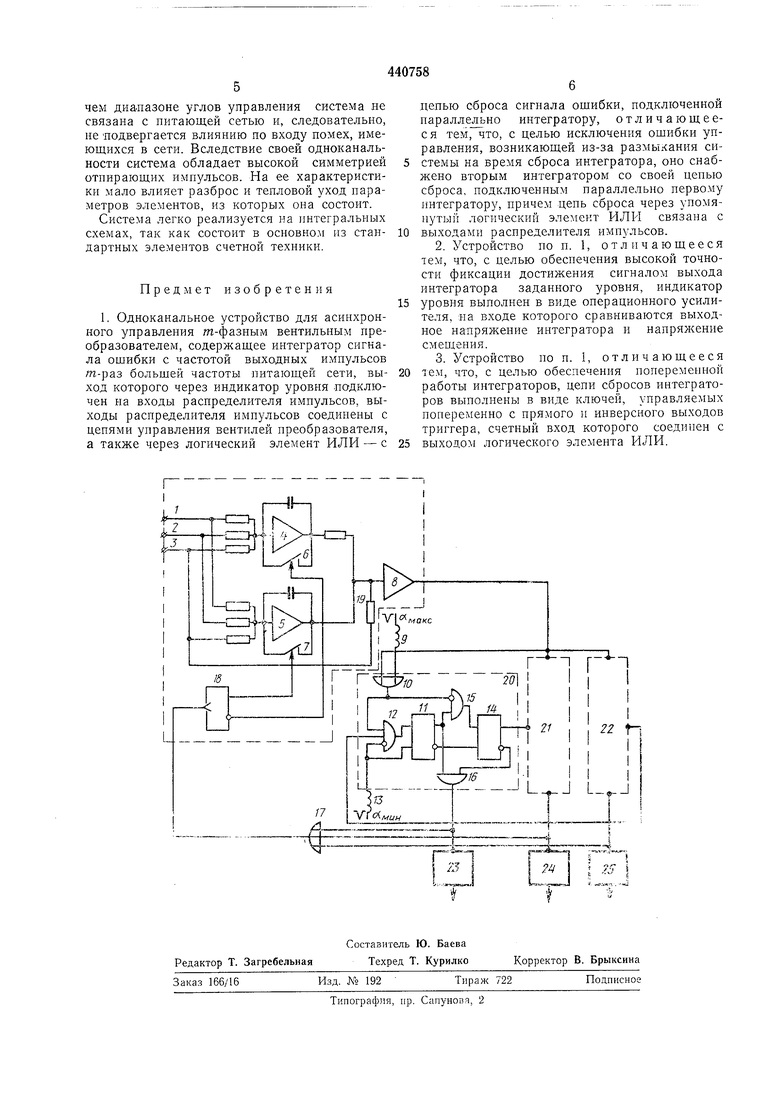

На чертеже изображена схема одноканального устройства для управления трехфазным вентильным преобразователем.

На схеме: I - вход сигнала управления; 2 - вход сигнала отрицательной обратной связи по регулируемому параметру; 3 - вход сигнала смещения; 4, 5-интеграторы (oneрационные усилители), охваченные емкостнэй обратной связью; 6, 7 - электронные ключи, например полевые транзисторы; 8 - пороговый элемент (операционный усилитель); 9 - обмотка импульсного трансформатора ограничения минимального значения угла управления; 10 - элемент ИЛИ, осуществляющий логическое суммирование сигналов: управляющего (выход порогового элемента 8) и ограничения амакс (обмотка 9); 11 - первый потенциальный триггер; 12 - элемент И с запретом, осуществляющий логическое перемножение сигналов выхода предыдущей ячейки распределителя импульсов, элемента 10 и инвертированного сигнала; 13 - обмотка пмпульсного трансформатора ограничения минимального значения угла управления амин; 14-- второй потенциальный триггер; 15-элемент «Запрет, осуществляющий запрет передачи сигналов с прямого выхода триггера II на первый вход триггера 14 сигналом выхода элемента 10; 16 - элемент И, осуществляющий логическое перемножение сигналов пря.мого выхода первого триггера II и инверсного выхода второго триггера 14; 17 - элемент ИЛИ, осуществляющий логическое суммирование выходных сигналов всех ячеек распределптеля; 1в - потенциальный триггер со счетны.м входом, осуществляющий попеременное замыкание ключей 6 и 7; 19 - сопротивление, определяющее величину порога срабатывания порогового элемента 8; 20, 21, 22 - ячейки распределителя импульсов фаз А, В к С соответственно; 23, 24, 26 - ячейки формирователей-усилителей управляющих импульсов.

При сигнале ошибки, равном нулю, устанавливается такой сигнал смещения (вход 3), чтобы время нарастания напряжения на выходе . интегратора, производящего интегрирование в данном интервале (например интегратора 4) до значения, определяемого порогом срабатывания элемента 8, соответствовало интервалу между импульсами управления преобразователя, т. е. 2я/т (т - число фаз преобразователя).

Порог срабатывания элемента 8 определяется напряжением смещения на входе 3 и величиной сопротивления 19.

В установившемся режиме выдача сигнала, например, на выходе ячейки 20 распределителя фазы А происходит при следующих условиях: триггер И взведен (на прямом выходе сигнал «О) импульсом начала диапазона с обмотки 13, предыдущая ячейка 22 сработала, т. е. на средний вход элемента 12 подан сигнал «1.

При достижении выходным сигналом интегратора величины срабатывания порогового элемента 8 на верхний по схеме вход элемента 12 поступает сигнал «1. Так как к этому времени импульс с обмотки 13 закончился, элемент 12 подает сигнал «1 на верхний вход триггера 11. На прямом выходе триггера И появляется сигнал «1. Так как до этого момента на инверсном выходе триггера ,14 имеется также сигнал «1, элемент 16 пропускает сигнал на ячейку 23.

Одновременно сигнал «1 через элемент 17 и триггер 18 попадает на входы электронных ключей 6 и 7. Ключ 6 замыкается и сбрасывает верхний интегратор, ключ 7 размыкается, и нижний интегратор вступает в работу, подготавливая выдачу следующего импульса управления.

При сбросе интегратора на выходе элемента 8 появляется сигнал «О. Этот сигнал отпирает элемент 15, и триггер 14 перебрасывается в положение, при котором на его прямом выходе сигнал «1, а на инверсном - «О. Элемент 16 запирается.

Таким образом, длительность сигнала на выходе элемента 16 обусловлена временем нахождения в закрытом состоянии элемента 15, т. е. временем наличия сигнала на выходе элемента 8.

Сигнал «1 с прямого выхода триггера 14 подается на вход следующей ячейки 21 распределителя. Далее процесс повторяется.

По достижении выходным сигналом интегратора порога срабатывания элемента 8 сигнал «1 подается на все фазные блоки. При этом реагирует только та ячейка распределителя импульсов, в которой триггер 11 предварительно взведен сигналом обмотки 13. В остальных ячейках этот триггер сброшен, поэтому сигналы, приходящие с выхода элемента 8, не изменяют их состояния.

Если интегратор сигнала ошибки на интервале между импульсами управления соседних фаз не равен нулю, т. е. среднее значение регулируемого параметра на равно заданному, сигнал на выходе интегратора соответственно раньше или позже достигнет значения порога срабатывания элемента 8, что будет соответствовать сокращению или увеличению интервалов между импульсами управления вентилями, т. е. их сдвигу по фазе соответственно вперед или назад до тех пор, пока регулируемый параметр не станет равным по среднему значению заданной величине.

Движение импульсов управления по фазе вперед ограничено моментом подачи им-пульсов с обмотки 13. Например, если после срабатывания фазы

С (ячейка 22) большая величина отрицательного сигнала ошибки вызывает появление сигнала «1 на выходе элемента 8 до подачи импульса с обмотки 13, то на выходе элемента 16 ячейки 20 фазы А и.мпульс не появляется, так как элемент 16 закрыт сигналом «О с инверсного выхода триггера 14. В момент, соответствующий минимальному значению угла управления для фазы Л, с обмотки 9 поступит импульсный сигнал «1, который кратковременно выключит элемент 12, чтобы сигнал с его выхода не мешал перебросу триггера 11, и взведет триггер 11 (на прямом выходе сигнал «О). Одновременно сигналом «1 с инверсного выхода триггера 11 взведется триггер 14. Сигналом «1 с инверсного выхода триггера 14 откроется элемент 16.

После окончания импульса на обмотке 13 на выходе элемента 12 опять появится сигнал «1, который перебросит триггер 11 в положение, при котором на прямом его выходе будет сигнал «1.

Так как на обоих входах элемента 16 имеется по сигналу «1, на выходе ячейки 20 фазы А появляется сигнал, который сбрасывает интегратор, и т. д.

Большая величина положительной ошибки на входе системы может привести к тому, что элемент 8 не сработает до конца диапазона управления очередной фазы. Тогда, если эта

фаза Л, в момент максимального для нее угла управления, установленного узлом ограничения, будет подан импульс с обмотки 9, заменяющий для фазы Л сигнал с элемента 8. Далее фазная ячейка 20 будет работать как при

нормальной работе, и сигнал на выходе интегратора будет сброшен несмотря на то, что он так и не достиг уровня срабатывания порогового элемента 8. Это делается для того, чтобы интегрирование сигнала ошибки на следующем интервале начиналось с нуля независимо от ощибки на предыдущем интервале.

Предлагаемая система фазового управления вентильными преобразователями обладает высокой помехоустойчивостью, так как в рабо

| название | год | авторы | номер документа |

|---|---|---|---|

| Вентильный электродвигатель с токовым регулированием | 1989 |

|

SU1677807A2 |

| Устройство для управления и защиты тиристоров многофазного выпрямителя | 1977 |

|

SU687557A1 |

| Устройство одноканального асинхронного фазового управления вентильным преобразователем | 1973 |

|

SU529538A1 |

| Устройство для одноканального фазового управления вентильным преобразователем | 1982 |

|

SU1083325A1 |

| Устройство для программного управления шаговым двигателем | 1981 |

|

SU1015339A1 |

| Реверсивный вентильный электродвигатель | 1983 |

|

SU1132329A1 |

| Устройство для автоматической сменыМАСшТАбОВ B АНАлОгОВОй ВычиСлиТЕль-НОй МАшиНЕ | 1978 |

|

SU815729A1 |

| Стабилизированный многофазный импульсный преобразователь постоянного напряжения | 1986 |

|

SU1355965A1 |

| Способ упреждающего управления вентильным преобразователем | 1984 |

|

SU1288858A1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

Авторы

Даты

1974-08-25—Публикация

1971-09-21—Подача