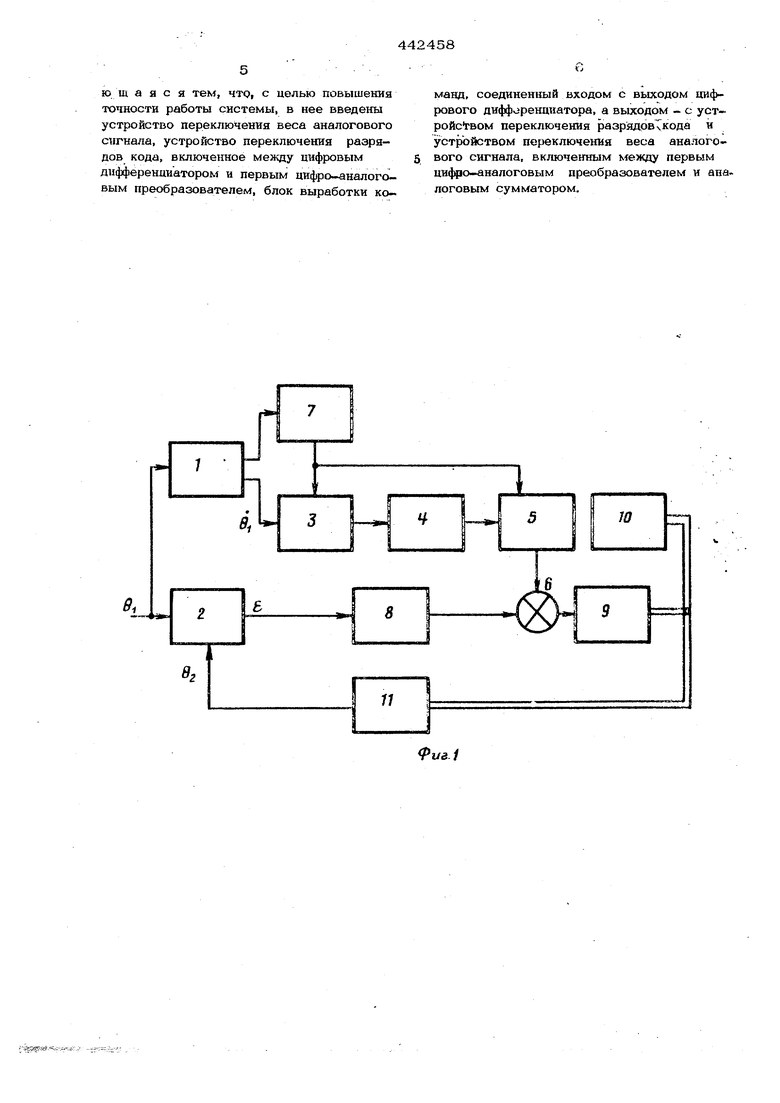

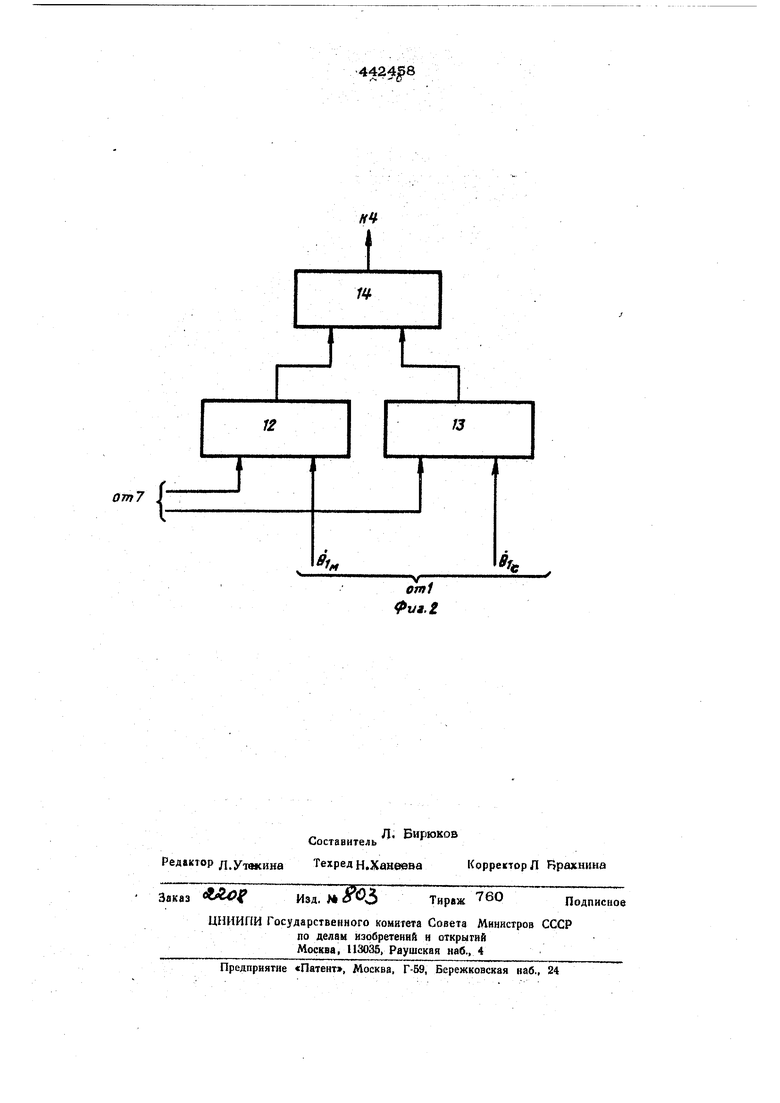

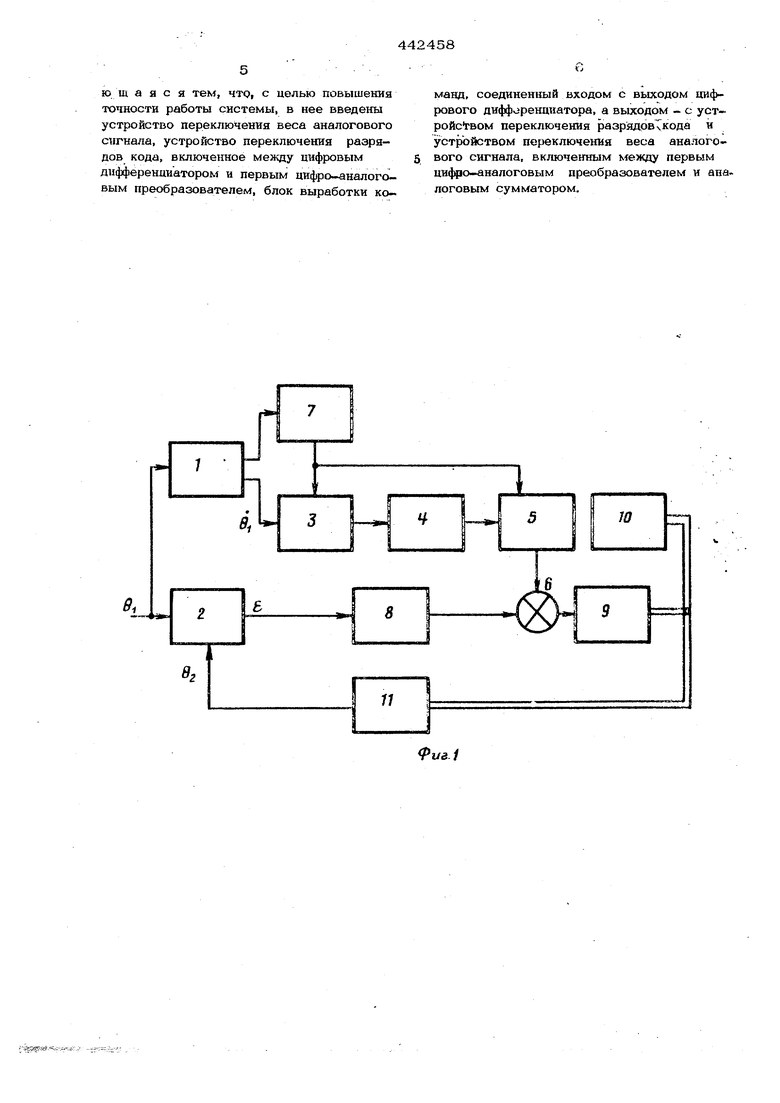

(54) ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА КОМБИНИРОВАННОГО . g младшие и старшие разряды кода j n компенсирующего сигнала. ; Цифровая следящая система комбвнироj ванного регулирования состоит из цифро1БОГО дифферешшатора 1, вход которого соединен с одним из входов цифрового сумг матора 2, а один из выходов - с устройст- вом переключения разрядов кода 3, выход IcoToporo соединен последовательно с дифро аналоговым преобразователем 4, устройство переключения веса аналогового сигнала 5 и аналоговым сумматором 6, Второй выход дифференциатора 1 соединен с выходом блок выработки команд 7, выход которого соединен с вторым входом устройства переключения разрядов кода 3. Выход сумматора 2 соединен последовательно с цифро-аналого вым преобразователем 8 и сумматором 6, выход которого соединен с входом привода 9, связанного с нагрузкой 1О и преобразователем вал-цифра 11, выход которого со единен с вторым входом сумматора 2, Устройство переключения разрядов кода 3 состоит из двух сборок вентилей 12, 13 и сборки схем ИЛИ 14. Сборка вентилей 12, включающая в себя десять схем И, входами соединена с блоком выработки команд 7 с младшими .разрядами (с 1 по Ю) дифференциатора 1. Сборка вентилей 13, включающая в себя десять схем И, входами соединена также с блоком выработки команд 7 и со Старшими разрядами (с 5 по 14) дифференциатора 1, Выходы вен- ; тильных сборок 12 и 13 соединены со входами сборки схем ИЛИ 14, выход которой соединен с цифро-аналоговым преобразователем 4 Цифровой дифференциатор 1 служит для выработки первой производной в цифровой форме от задающего воздействия б чяф ровой сумматор 2 предназначен для выработки сигнала ошибки системы. Устройство переключения разрядов кода 3 осуществляет подключение по сигналу с блока выра-i ботки команд 7 десяти младших или десяти старших разрядов дифференциатора 1 к к десятиразрадной сетке цифро-аналогового преобразователя 4, а устройство переключения веса аналогового сигнала 5 выдает уровни компенсирующего сигнала в аналоговой форме в соответствии с четырнад цатиразрядным кодом дифференциатора 1. При работе цифровой следящей системы комбинироваявого регулирования на входы дифференциатора 1 и сумматора 2 поступа ет задающее воадействяе сумматоре 2 происходит операция вьь., читания кода сигнала обратной связи © , поступающехх) с преобразователя вал-диф- ра 11, из кода сигнала Q , и на выходе его формируется код сигнала рассогласовав НИН , который поступает на ци чро- налрговый преобразователь в. . Дифференциатор 1 выдает четырнадцати-: разрядный код компенсирующего сигнала, который поступает на блрк выработки ко манд 7 и устройство переключения разрядов кода 3. Блок 7 анализирует код с дифференаиа,тора 1 и подключает сборку вен 2 через сборку ИЛИ 14 (младагае 1О разрядов) к разрядной сетке цифро-аналогового преобразователя 4, если в четырех старших разрядах - нули, и подключает сборку вентилей 13 через сборку схем ИЛИ 14 (старшие Ю разрядов), если хотя бы в одном из четырех старших разрядов кода присутствует единица. Одногвременно он выдает команду на устройство переключения веса аналогового устройства 5, которое приводит диапазон изменения сигнала с цифро-аналогового преобразователя 4 в соответствие с четырнадцатиразрядным кодом, т. е. делит уровень сиг-нала на К-16, если к разрядной сетке циф.ро- налогового преобразователя 4 присо- , единены младшие Ю разрядов кода с цифро вого дифференциатора 1 и делит на К-1, если присоединены старшие Ю разрядов кода. Сигнал ошибки с цифро-аналогового преобразователя 8 и компенсирующий сигнал, приходящий в устройства переключения веса аналогового сигнала 5 с соответствующим коэффициентом, суммируются в сумматоре 6, и сумма подается на привод 9, который управляет нагрузкой 10. Предмет изобретения Цифровая следящая система комбинированного регулирования, содержащая цифровой дифференциатор, первый цифро-аналоговый преобразователь и последовательно соединенные хшфровой сумматор, второй цифро-аналоговый преобразователь, анало говый сумматор, привод с нагрузкой и преобразователь вал цифра, причем вход цифрового дифференциатора и выход преоб 1 рааователя вал-цифра подключешы ко входам цифрового сумматора, о v л ича.

ю щ а я с я тем, чтО| с целью повышения точности работы системы, в нее введены устройство переключения веса аналогового сигнала, устроГютво переключения разрядов кода, включенное между цифровым дифференциатором и первым цифро-аналоговым преобразователем, блок выработки команд, соединенный входом с выходом цифрового дифференциатора, а выходом - с устроистом переключения разрядовТкода и уст юйством переключения веса аналогового сигнала, включенным между первым ци о-аналоговым преобразователем и аналоговым сумматором.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1987 |

|

SU1548845A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU873405A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

| Устройство аналого-цифрового преобразования | 1984 |

|

SU1295514A1 |

| Многоканальный цифро-аналоговый преобразователь | 1974 |

|

SU636794A1 |

| Двухотсчетный следящий привод | 1989 |

|

SU1700535A1 |

| Электроразведочная станция | 1989 |

|

SU1730603A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Приемное устройство для высокочастотной геоэлектроразведки | 1988 |

|

SU1613987A1 |

Ю

б.

12

{:

от

ffU

13

omi

Авторы

Даты

1974-09-05—Публикация

1972-08-15—Подача