Изобретение относится к вычислительной и измерительной технике и может быть использовано для преобразования 1дифровьгх величин в аналоговые .

Цель изобретения - повышение достоверности преобразования.

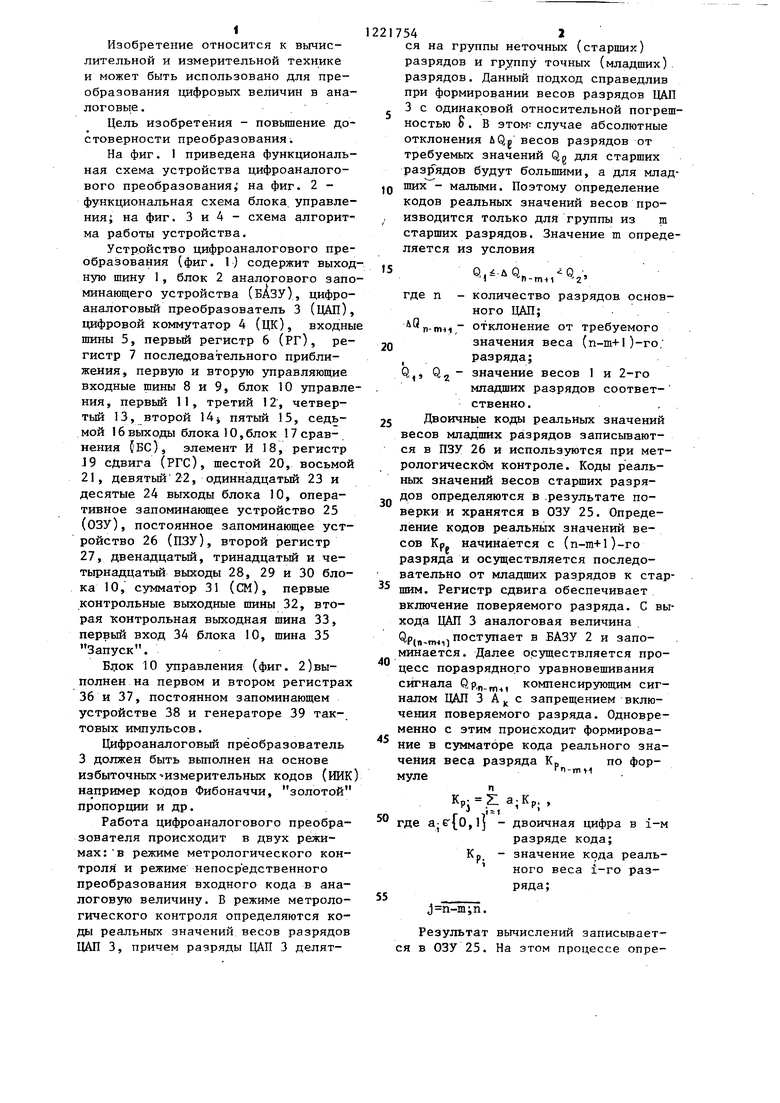

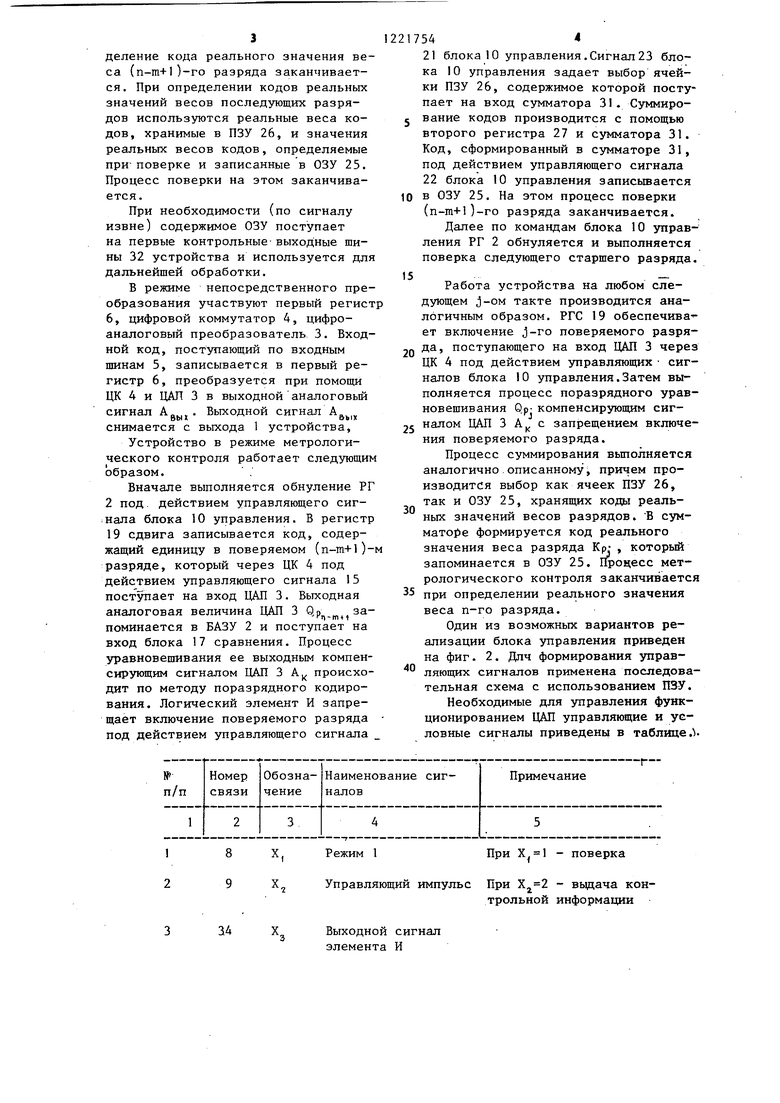

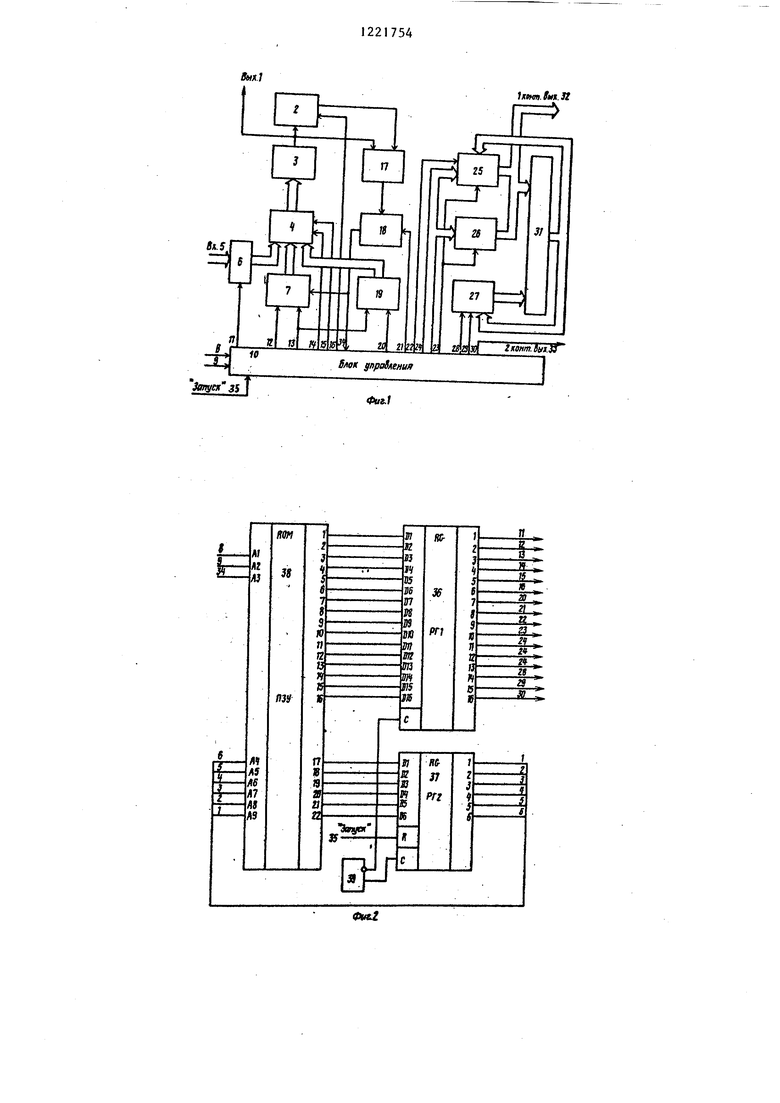

На фиг. 1 приведена функциональная схема устройства цифроаналого- вого преобразованияj на фиг. 2 - функциональная схема блока управления; на фиг. 3 и 4 - схема алгоритма работы устройства.

Устройство цифроаналогового преобразования (фиг. 1) содержит выходную шину 1, блок 2 аналогового запоминающего устройства (БАЗУ), цифро- аналоговый преобразователь 3 (ЦАП), цифровой коммутатор 4 (ЦК), входны шины 5, первый регистр 6 (РГ), регистр 7 последовательного приближения, первую и вторую управляющие входные шины 8 и 9, блок 10 управления, первый 11, третий 12, четвертый 13, второй 14i пятый 15, седьмой 16 выходы блока 10, блок 17 сравнения ЦБС), элемент И 18, регистр J9 сдвига (РГС), шестой 20, восьмой 21, девятый 22, одиннадцатый 23 и десятые 24 выходы блока 10, оперативное запоминающее устройство 25 (ОЗУ), постоянное запоминающее устройство 26 (ПЗУ), второй регистр 27, двенадцатьш, тринадцатью и че- тьфнадцатый выходы 28, 29 и 30 блока 10, сумматор 31 (см), первые контрольные выходные шины 32, вторая контрольная выходная шина 33, первый вход 34 блока 10, шина 35 Запуск.

BJJOK 10 управления (фиг. 2)выполнен на первом и втором регистрах 36 и 37, постоянном запоминающем устройстве 38 и генераторе 39 тактовых импульсов.

Цифроаналоговьй преобразователь 3 должен быть вьтолнен на основе избыточных измерительных кодов (ИИК например кодов Фибоначчи, золотой пропорции и др.

Работа цифроаналогового преобразователя происходит в двух режимах: в режиме метрологического контроля и режиме непосредственного преобразования входного кода в аналоговую величину. В режиме метрологического контроля определяются коды реальных значений весов разрядов ЦАП 3, причем разряды ЦАП 3 делят

10

15

7542

ся на группы неточных (старших) разрядов и группу точных (младших). разрядов. Данный подход справедлив при формировании весов разрядов ЦАП 3 с одинаковой относительной погрешностью 8. В этом- случае абсолютные отклонения AQp весов разрядов от требуемых значений Qg для старших разрядов будут большими, а для младших - малыми. Поэтому определение кодов реальных значений весов производится только для группы из m старших разрядов. Значение m определяется из условия

Q.i-u Q Q , 1 n-m + i г

где n - количество разрядов основного ЦАП;

4Q

n-m-ii.

20

отклонение от требуемого значения веса (n-m+l)-ro. разряда;

Q, значение весов 1 и 2-го

младших разрядов соответ- ственно.

Двоичные коды реальных значений весов младших разрядов записьгаают- ся в ПЗУ 26 и используются при метрологической контроле. Коды реальных значений весов старших разрядов определяются в .результате поверки и хранятся в ОЗУ 25. Определение кодов реальных значений весов Кр начинается с (n-m+l)-ro разряда и осуществляется последовательно от младших разрядов к старшим. Регистр сдвига обеспечивает включение поверяемого разряда. С выхода ЦАП 3 аналоговая величина Qp, поступает в БАЗУ 2 и запоминается. Далее осуществляется процесс поразрядного уравновешивания сигнала Qp,n., компенсирующим сигналом ЦАП 3 А с запрещением включения поверяемого разряда. Одновременно с этим происходит формирование в сумматоре кода реального значения веса разряда К- по форrn-f- нуле

-тм

50

Kp.Za.Kp.,

где aje {o,lj - двоичная цифра в i-м разряде кода;

К,

J n-m;n.

- значение кода реального веса i-ro разряда;

Результат вычислений записывается в ОЗУ 25. На этом процессе опре3

деление кода реального значения веса {n-m+l)-ro разряда заканчивается. При определении кодов реальных значений весов последующих разрядов используются реальные веса кодов, хранимые в ПЗУ 26, и значения реальных весов кодов, определяемые при-поверке и записанные в ОЗУ 25. Процесс поверки на этом заканчивается.

При необходимости (по сигналу извне) содержимое ОЗУ поступает на первые контрольные выходные шины 32 устройства и используется для дальнейшей обработки.

В режиме непосредственного преобразования участвуют первый регист 6, цифровой коммутатор 4, цифро- аналоговый преобразователь 3. Входной код, поступающий по входным шинам 5, записывается в первый регистр 6, преобразуется при помощи ЦК 4 и ЦДЛ 3 в выходной аналоговый сигнал А„ .. Выходной сигнал А „

ВЫАоЫХ

снимается с выхода 1 устройства.

Устройство в режиме метрологического контроля работает следующим образом. ,

Вначале выполняется обнуление РГ 2 под. действием управляющего сигнала блока 10 управления. В регистр 19 сдвига записывается код, содержащий единицу в поверяемом (n-m+1)разряде, который через ЦК 4 под действием управляющего сигнала 15 поступает на вход ЦАП 3. Выходная аналоговая величина ЦАП 3 Qp запоминается в БАЗУ 2 и поступает на вход блока 17 сравнения. Процесс уравновешивания ее выходным компенсирующим сигналом ЦАП 3 Aj происходит по методу поразрядного кодирования. Логический элемент И запрещает включение поверяемого разряда под действием управляющего сигнала

34

Выходной сигнал элемента И

20

217544

21блока 10 управления.Сигнал23 блока 10 управления задает выбор ячейки ПЗУ 26, содержимое которой поступает на вход сумматора 31. Суммиро5 вание кодов производится с помощью второго регистра 27 и сумматора 31. Код, сформированный в сумматоре 31, под действием управляющего сигнала

22блока 10 управления записьшается 10 в ОЗУ 25. На этом процесс поверки

(п-т+1)-го разряда заканчивается.

Далее по командам блока 10 управления РГ 2 обнуляется и выполняется поверка следующего старшего разряда.

15-

Работа устройства на любом следующем J-OM такте производится аналогичным образом. РГС 19 обеспечива- ет включение j-ro поверяемого разряда, поступающего на вход ЦАП 3 через ЦК 4 под действием управляющих сигналов блока 10 управления.Затем выполняется процесс поразрядного уравновешивания Qp- компенсирующим сиг25 налом ЦАП 3 А с запрещением включения поверяемого разряда.

Процесс суммирования выполняется аналогично.описанному, причем производится выбор как ячеек ПЗУ 26, так и ОЗУ 25, хранящих коды реальных значений весов разрядов. В сумматоре формируется код реального значения веса разряда Кр; , который запоминается в ОЗУ 25. Йроцесс метрологического контроля заканчивается

35 при определении реального значения веса п-го разряда.

Один из возможных вариантов реализации блока управления приведен на фиг. 2. Длч формирования управляющих сигналов применена последовательная схема с использованием ПЗУ. Необходимые для управления функционированием ЦАП управляющие и условные сигналы приведены в таблице .V

30

40

трольной информации

11 12 13 14

15

X,,,

Синхроимпульс РГ 1 Синхроимпульс РПП Начальная установка

1Адрес ЦК

2Адрес ЦК

Алгоритм функционирования устройства в соответствии с приведенным описанием работы показан на фиг. 3 и 4.

Формула изобретения

1. Устройство цифроаналогового преобразования, содержащее блок управления, цифровой коммутатор , первый регистр, информационные входы которого являются входными шинами, управляющМ вход подключен к первому выходу блока управления, выход5 1 подключены к соответствующим первым информационным входам цифррПродолжение таблицы

Цри коммутируется РГС

При У 1 коммутируется РПП

При , коммутируется РГ 1

вого коммутатора, первый управляющий вход которого подключен к второму выходу блока управления, выходы подключены к соответствующим входам цифроаналогового преобразователя, выход которого является выходной шиной устройства отличающееся тем,что, с целью повышения достоверности преобразования, введены блок аналогового запоминающего устройства,.блок сравнения, второй регистр, регистр сдвига, элемент И, оперативное запоминающее устройство, постоянное запоминающее устройство, сумматор, регистр последовательного приближения, первый управляющий вход которого подключен к третьему выходу блока управления, второй управляющий вход объединен с первым управляющим входом регистра сдвига и подключен к четвертому выходу блока управления, информационный вход .объединен с первым входом блока управления и подключен к выходу элемента И, выходы подключены к соответствующим вторым информационным входам цифрового коммутатора, второй управляющий вход которого подключен к пятому выходу блока управления, третьи информационные входы подключены к соответствующим выходам регистра сдвига, второй управляющий вход которого подключен к шестому выходу блока управления, седьмой выход которого подключен к управляющему входу блока аналогового запоминающего устройства, информационный вход которого объединен с первым входом блока сравнения и подключен к выходу цифро- аналогового преобразователя, выход подключен к второму входу блока сравнения, выход которого подключен к первому входу элемента И, второй вход которого подключен к восьмому выходу блока управления, девятый выход которого подключен к первому управляющему входу оперативного запоминающего устройства десятые выходы блока управления подключены к соответствующим адресным входам оперативного и постоянного запоминающих устройств, одиннадцатый выход подключен к второму управляющему входу оперативного за- поминакицего устройства и к первому управляющему входу постоянного запоминающего устройства,- выходы которого объединены с соответствующими выходами оперативного запоминающего устройства, являются первыми

контрольными выходными шинами и ПОД

ключены к соответствующим первым входам сумматора, выходы которого подключены к соответствующим информационным входам оперативного запо2217548

минающего устройства и второго регистра, выходы которого подключены к соответствующим вторым входам сумматора, первый и второй управляющие

5 входы подключены соответственно к двенадцатому и тринадцатому выходам блока управления, четырнадцатый выход которого является второй контрольной выходной шиной, второй и

10 третий входы являются первой и второй управляющими шинами соответственно, четвертый вход является шиной Запуск. . 2. Устройство по п. 1, о т л и15 чающееся тем, что блок управления вьтолнен на первом и втором регистрах, генераторе тактовых импульсов и постоянном запоминающем устройстве, первый, второй и третий.

20 входы которого являются соответствен- но вторым, третьим и первым входами блока управления, входы с четвертого по девятый подключены к соответствующим выходам второго регистра,

25 выходы с первого по Е+13, где Z , an- количество разрядов преобразуемого кода, подключены к соответствующим информационным входам первого регистра, выходы с

3Q +14 по подключены к соответствующим информационным входам второго регистра, первьй управляющий вход которого является четвертым входом блока управления, второй управляющий вход подключен к прямому входу генератора тактовых импульсов, инверсный выход которого подключен к управляющему входу первого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый выходы которого являются соответственно первым, третьим, четвертым, вторым, пятым, седьмым, щестым, восьмым, девятым и одиннадцатым выходами блока управления, выходы с одиннадцатого по +10 являются десятыми выходами блока управления, выходы с .Т+11 по +13 являются соответственно двенадцатым, тринадцатым и четырнадца-.

тым выходами блока управления;

35

40

45

ffuxJ

Л. 5

jJdByor jsl

IfiHm. tun. Л

«tee./

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU949800A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

Изобретение относится к области вычислительной и измерительной техники и может быть использовано для преобразования цифровых величин в аналоговые. Изобретение позволяет повысить достоверность преобразования за счет использования избыточных измерительных кодов (ИИК) и введения блока аналогового запоминающего устройства, постоянного запоминающего устройства, сумматора, регистра последовательного приближения, блока сравнения, второго регистра, регистра сдвига, элемента И, оперативного запоминающего устройства, которые обеспечивают работу устройства в режиме метрологического контроля и режиме непосредствен- ного преобразования входного кода в аналоговую величину. В режиме метрологического контроля, который основан на свойствах ИИК, определяются коды реальных значений весов разрядов цифроаналогового преобразователя, которые записываются в оперативное запоминающее устройство и затем используются для коррекции в режиме непосредственного преобразования входного кода в аналоговую величину. 1 з.п. ф-лы,. 4 ил, табл. (О to to ел й

| Цифро-аналоговый преобразователь | 1978 |

|

SU947955A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР ,№ 864548, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-03-30—Публикация

1984-08-15—Подача