Изобретение относится к специализированным средствам вычислительной техники, предназначенным для статистического анализа случайных процессов.

Известны устройства для определения экстремумОБ, содержащие слов вы,целения экстремума, два идентичных канала, в каждый из которых входит триггер определения типа экстремума, блоки оперативной и договременной памяти.

Недостатками таких устройств является сложность логической схемы определения наличия и типа экстремума, а также существенные затраты оборудования на регистрирующие счетчики, в качестве которых обычно используются двоичные счетчики импульсов.

Предлагаемое устройство отличается от известных тем, что в нем второй выход преобразователя аналог-код подключен в первым входам блока сравнения и блоаа переноса

кода, второй вход которого соединен с вторым выходом блока задания программы, а выход - с вторым входом блока оперативной памяти, второй выход которого соединен с вторым входом блока сравнения. Выходы последнего подключены к первым

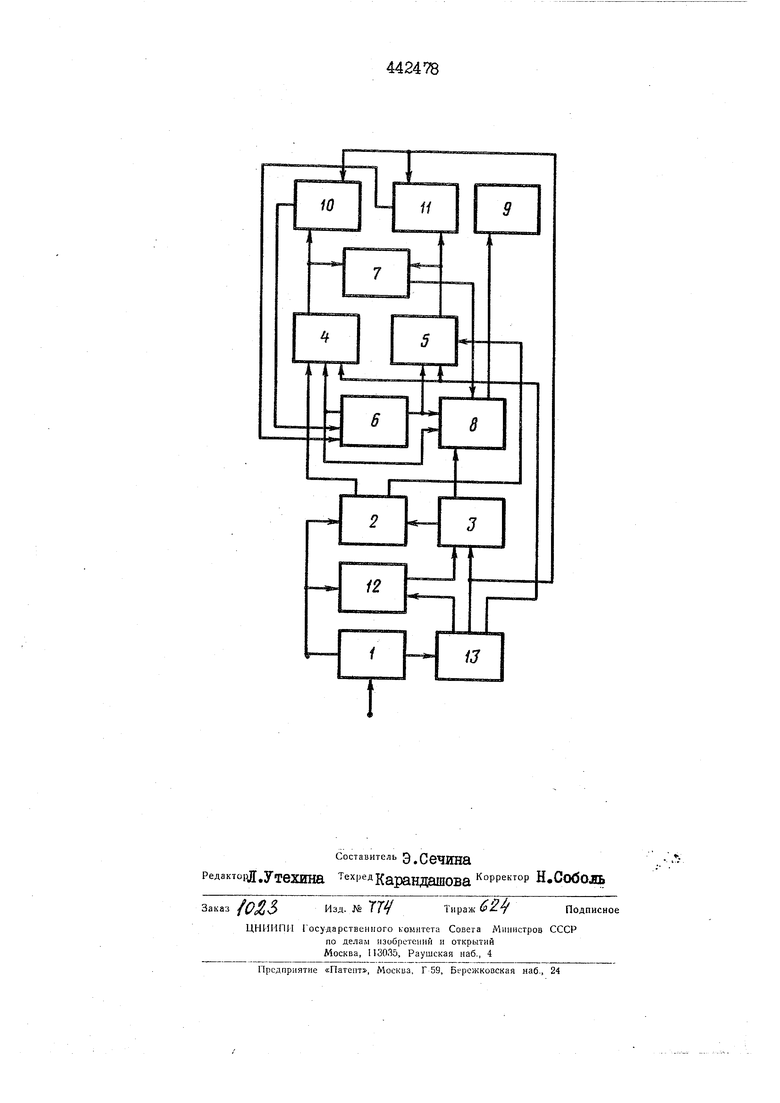

входам схем И соответственно,выходы которых подключены к первыщ входам элементов задержки и входам схемы ИЛИ, выход которой соединен с вторым входом схемы выбора адреса. При этом вторые входы элементов.задержки объединены и подключены к первому выходу блока задания программы, третий выход которого соединен со вторыми входами схем И,третьи входы которых соединены соответственно с третьим и четвертым входами схемы выбора адреса и выходами блока выделения экстремумов, первый и второй входы которого соединены с выходами элеiMeHTQB задержки. Это позволяет упростить устрой. Функциональная схема предлагаемого устройства показана, на чертеже, Устройство содержит преобразователь 7 аналог-код ; блок сравне ния 2; блок оперативной памяти 3; схемы И 4 и 5; блок выделения экстремума 6; схему ШШ 7; схему выбора адреса 8; блок долговременной памяти 9; элементы задержки 10, II; блок переноса кода 12 и блок задания программы 13 Устройство работает следукшщм образом. Анализируемая кция подается на преобразователь аналог-код I, имеющй заданное число уровней квантования. Измеренное значение в цифровом коде поступает с преобразователя на блок сравнения 2, гд сравнивается с предыдущим измеренным значением, которое записано в блоке оперативной памяти 3, В случае неравенства двух измеренных значений на одном из выходов блока сравнения 2 в зависимости от знака производной появляется сигнал, управляющий одной из схем И 4 или В, Выходы блока выделения экстрецу ма 6 соединены с входами схем -И таким образом, что при их стробировании сигнал на однсш из выходов схем И появляется только в случае изменения знака производной, т,е, при наличии экстремума. Тип экстремума определяется состоянием триггера блока выделения экстремума 6 на данный момент времени. Сиг нал с выхода схемы И через элементы задержки 10,11 поступает на соответствуЕощий вход триггера блока выделения экстремума 6 и изменяет его состояние на противоположное, а через схему ИЛИ 7 поступает на схему выбора адреса 8, При поступлении сигнала с одной из схем и 4, 5 схема выбора адреса 8 вызывает из блока долговремен ной памяти 9 числовую линейку, соответствующую цифровому коду, запи санному в оперативной памяти 3, и состоянию триггера блока выделения экстремумов 6, К значению, записанному в вызванной числовой ли-,..тс . нейве, добавляется единица; соответствуЪщая наличию определенного типа Э15стремума на данном уровне. Новое значение записьшается в ту же числовую линейку. Работа всех блоков устройства синхронизируется блоком задания программы 13, ПРЩЛЁТ ИЗОБРЕТЕНИЯ Устройство Д7Ш определения плотности вероятностей экстремальных значений случайных процессов, содержащее блок переноса кода, блоки сравнения, блок выделения экстремума, элементы задер;жки, схемы И, мсему ИЛИ, преобразователь аналог-код, первый выход которого соединен с входом блока задания программы, первый выход которого подклкгаен к первому входу блока оперативной памяти, первый выход которого соединен с первым входом схемы выбора адреса, выход которой соединен с блоком долговременной памяти, отличающееся тем, что, с целью упрощения устройства, второй выход преобразователя аналог-код подключен к первым входам блока сравнения и блока переноса кода, второй вход которого соединен с вторым выходом блока задания программы, а выход - с вторым входом блока оперативной памя-, ти, второй выход которого соединен с вторым входом блока сравнения, выходы которого подключены к первым входам схем И соответственно, выходы которых подключены к первым входам элементов задержки и входам схемы ШШ, выход которсй соединен с вторым входом схемы выбора адреса; при этом вторые входы элементов задержки объединены и подключены к первому выходу блока задания программы, третий выход которого соединен с вторыми входами схем И, третьи входы которых соединены соответственно с третьим и четвертым входами схемы выбора адреса и выходами блока выделения экстремумов, первый и второй входы которого соединены с выходами элементов задержки.

10

Is

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1979 |

|

SU875388A1 |

| Устройство для программного управления процессом обработки изделий микроэлектроники | 1986 |

|

SU1386962A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для программного регулирования | 1977 |

|

SU732814A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для программного регулирования | 1979 |

|

SU930263A2 |

| Устройство для числового программного управления станком | 1978 |

|

SU744465A1 |

| Устройство для автоматического контроля процесса сварки | 1984 |

|

SU1238921A1 |

| Устройство для распознавания изображений | 1983 |

|

SU1215123A1 |

| Адаптивный статистический анализатор | 1980 |

|

SU955090A1 |

Авторы

Даты

1974-09-05—Публикация

1972-12-07—Подача