ционный выход которого соединен с первым входом коммутатора и первым входом блока сравнения, выход блока сравнения соединен с вторым входом первого элемента И-НЕ блока задания режима, выход первого элемента И-НЕ блока задания режима соединен с вторым входом второго элемента И-НЕ блока задания режима, информационный выход первого регистра блока формирования и коммутации адресов соедине с входом первого операнда сумматора и с первым информационным входом первого коммутатора, выход которого соединен с входом блока индикации, информационньй выход второго регистра блока формирования и коммутации адресов соединен с вторым информационным входом первого коммутатора и первым входом схемы сравнения, выход которой соединен с третьим-входом второго элемента И-НЕ блока задания режима, вход записи счетчика блока формирования и коммутации адресов соединен с первым выходом блока клавиатуры, информационный выход счетчика соединен с вторым входом схемы сравнения, третьим информационным входом первого коммутатора, входом второго сумматора и адресным входом блока оперативной памяти, адресный вход устройства соединен с первым информационным входом второго коммутатора блока формирования и коммутации адресов, выход которого соединен с четвертым информационным входом первого коммутатора блока формирования и коммутации адресов, адресными входами блока внешней памяти, адресными входами блока постоянной памяти, блока записи в постоянную память, первый выход блока клавиату|ры соединен с управляющими входами

первого и второго коммутаторов блока формирования и коммутации адресов второй выход блока клавиатуры соедиг иен. с вторым информационным входом коммутатора, вьгход которого соединен с вторым входом блока индикации, входом блока сравнения, с информационными входами блока оперативной памяти, блока внешней памяти, с информационным входом первого мультиплексора, блока записи в постоянную память, восьмой, девятый и десятый выходы блока клавиатуры соединены соответственно с управлякяцим входом коммутатора, с входом записи блока

внешней памяти, с первь|м входом первого элемента И блока записи в постоянную память, выход первого элемента И блока записи в постоянную память соединен с вторым входом триггера, единичный выход которого соединен с входом разрешения счета первого счетчика и счетным входом второго счетчика блока записи в постоянную память,выход генератора импульсов соединен со счетным входом первого счетчика, информационный выход которого соединен с первыми входами второго и третьего элеметов И блока записи в постоянную память, выход переполнения первого счетчика блока записи в постоянную память через элемент НЕ соединен с вторым входом третьего элемента И, выход которого соединен с первым входом четвертого элемента И блока записи в постоянную память, выход схемы сравнения блока записи в постоянную память соединен с вторым входом четвертого элемента И, выход которого соединен с информационным входом второго счетчика, информационый выход которого соединен с информационными входами первого и второго мультиплексоров и первым входо дешифратора блока записи в постоянную г лмять, выходы первого и второго мультиплексоров блока записи в постоянную память соединены соответственно с первым и вторым входам ) сравнения, выход первого мультиплексора блока записи в постоянную память соединен с вторым входом второго элемента И, выход которого соединен с вторым входом дешифратора и первым входом первого преобразователя уровней сигналов, выход которого соединен с информационным входом блока постоянной памяти и через второй преобразователь уровней с вторым входом мультиплексора и с третьим информационным входом коммутатора, вькод второго счетчика блока записи в постоянную память через одновибратор соединен с вторым входом первого элемента И блока записи в постоянную память и с вторым информационньм входом коммутатора блока задания режима, выход дешифратора блока записи в постоянную память соединен с вторым входом первого преобразователя уровней сигналов, информационньй выход блока внешней памяти соединен с четвертым информационным входом коммутатора и является информационным выходом уст1149268ройства, одиннадцатьй выход блокаклавиатуры соединен с входом чтения блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для контроля и регистрации асинхронных сигналов интерфейса | 1982 |

|

SU1084803A1 |

| Устройство для анализа производительности вычислительных систем | 1990 |

|

SU1711166A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для контроля электрического монтажа | 1989 |

|

SU1698843A1 |

УСТРОЙСТВО ДЛЯ ЗАПИСИ И КОРРЕКЦИИ ПРОГРАММ, содержащее блок клавиатуры, блок формирования и коммутации адресов, блок оперативной памяти, блок индикации и блок внешней памяти, причем блок формирования и коммутации адресов содержит первый и второй регистры, первый выход блока клавиатуры соединен с входами записи первого и второго регистров блока формирования и коммутации адресов, второй выход блока клавиатуры соединен с информахщонными входами первого и второго регистров блока формирования и коммутации адресов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок задания режима, блок сравнения, блок записи в постоянную память и коммутатор, а в блок формирования и коммутации адресов введены сумматор, схема сравнения, первый и второй коммутаторы -и счетчик, причем блок записи в постоянную память содержит генератор импульсов, первый и второй счетчики, первый и второй мультиплексоры, одновибратор, дешиф-i ратор, первый и второй преобраэователи уровней сигналов, блок постоянной памяти, схему сравнения, триггер четьфе элемента И и элемент НЕ, блок задания режима содержит коммутатор, триггер, переключатель, два элемента задержки, элемент И, элемент ИЛИ и два элемента И-НЁ, причем третий, четвертый, пятый, шестой и седьмой выходы блока клавиатуры соединены соответственно с управляющим входом коммутатора, первым входом первого элемента И-НЕ, первым входом элемента ИЛИ, первым входом элемента И и управляющим входом переключателя блока задания режима, § выход готовности блока внешней памяти соединен с первым информационным (Л входом коммутатора блока задания режима, выход коммутатора блока задания режима соединен с первым дом триггера и через первый элемент задержки с вторым входом триггера и первым входом второго элемента И-НЕ, выход которого через второй элемент задержки соединен с вторым входом элемента И и счетным входом счетчика блока формирования и коммутации адресов, выход элемента И блока задания режима соединен с вторым входом элемента ШШ, выход которого соединен с первым информационным входом переключателя блока задания режима, вход обращения устройства соединен с вторым информационным входом переключателя блока задания режима, выход которого соединен с входом чтения блока внешней памяти и первым входом триггера блока записи в постоянную память, выход триггера блока задания режима соединен с входом обращения блока оперативной памяти, информа

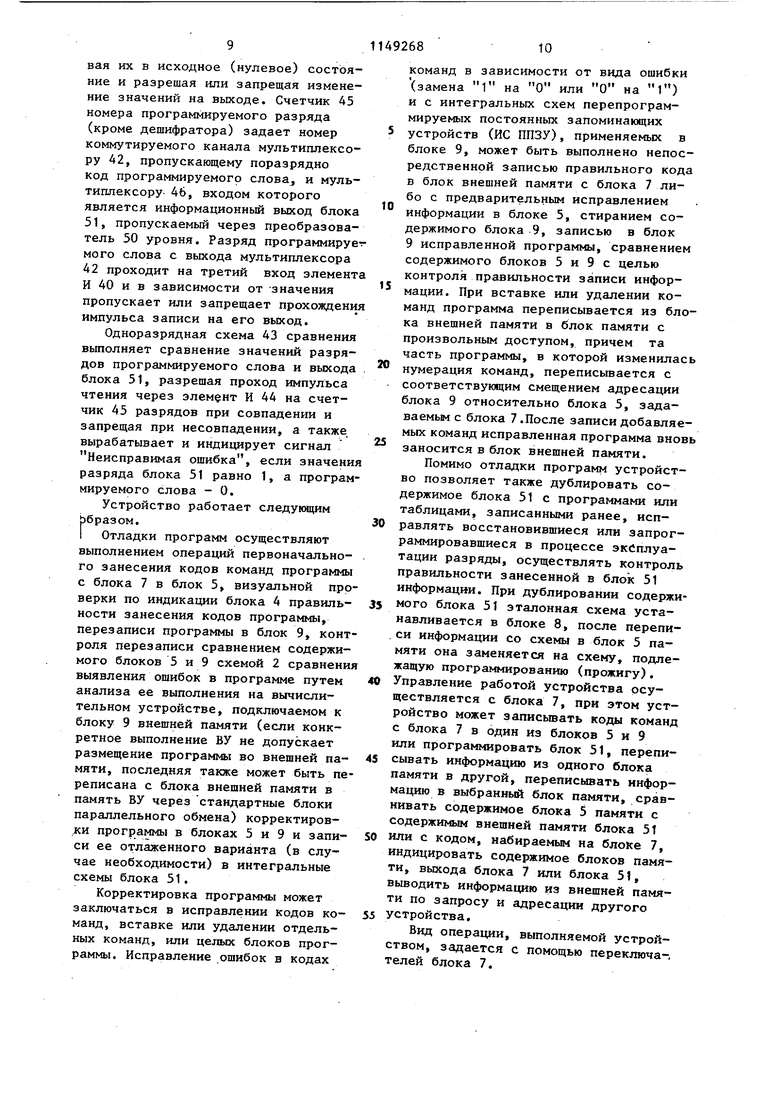

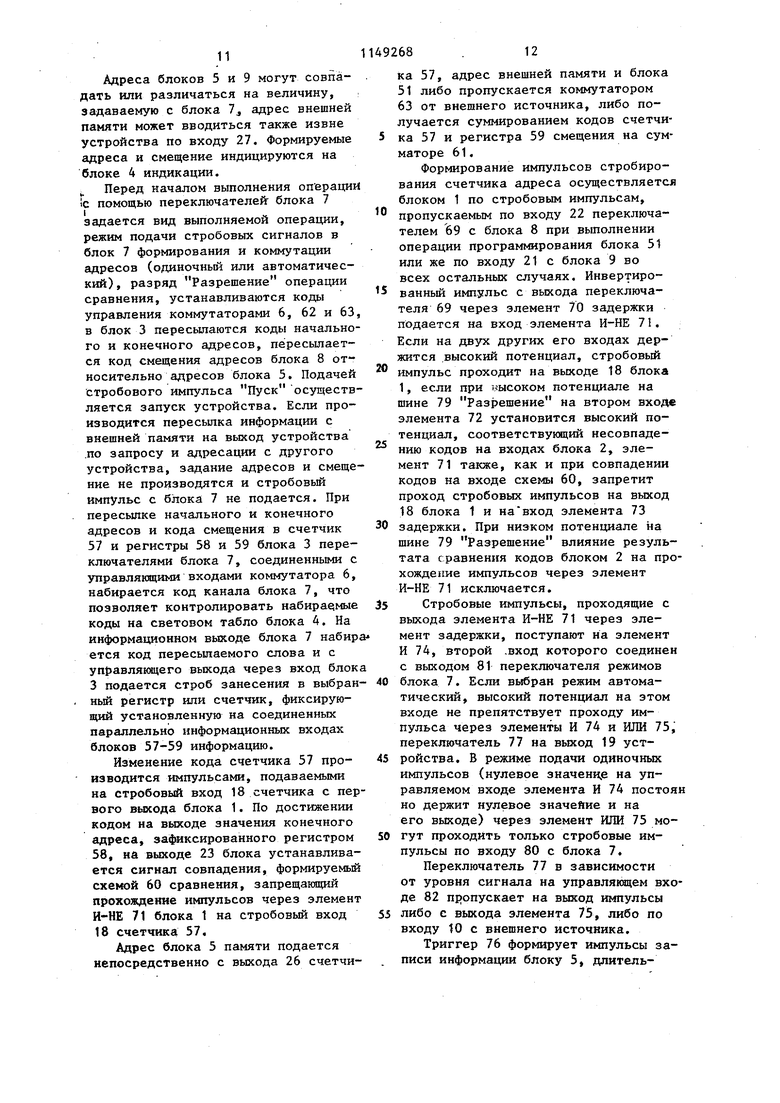

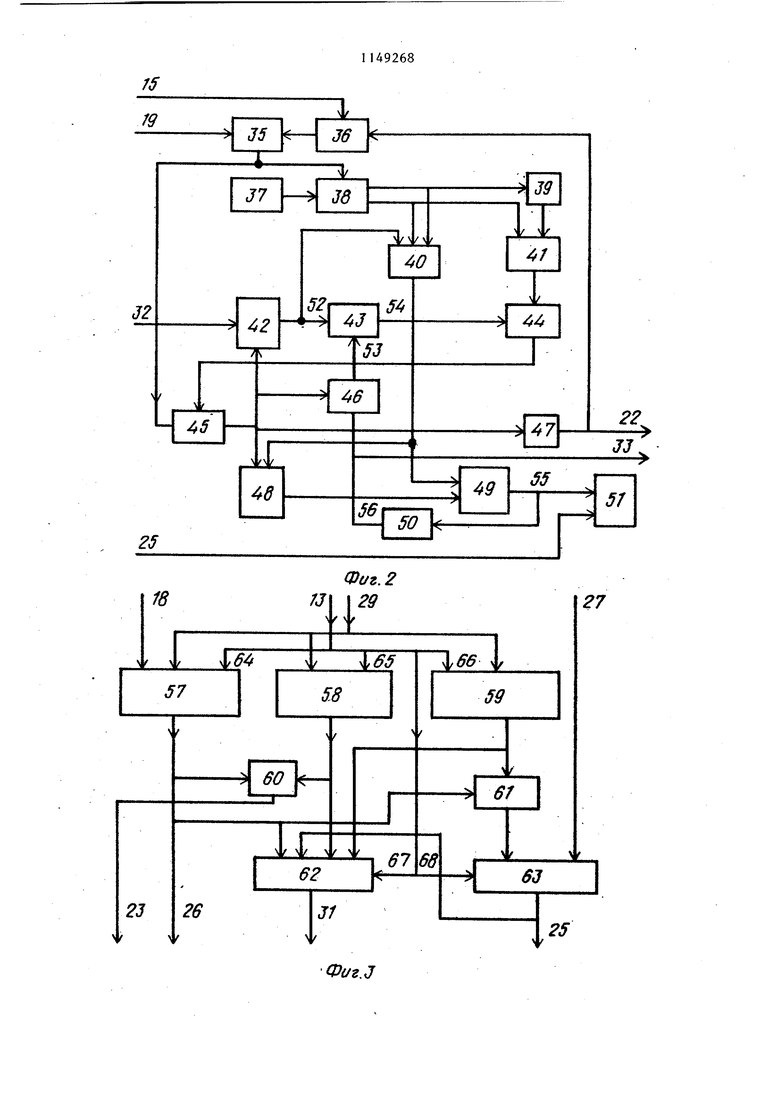

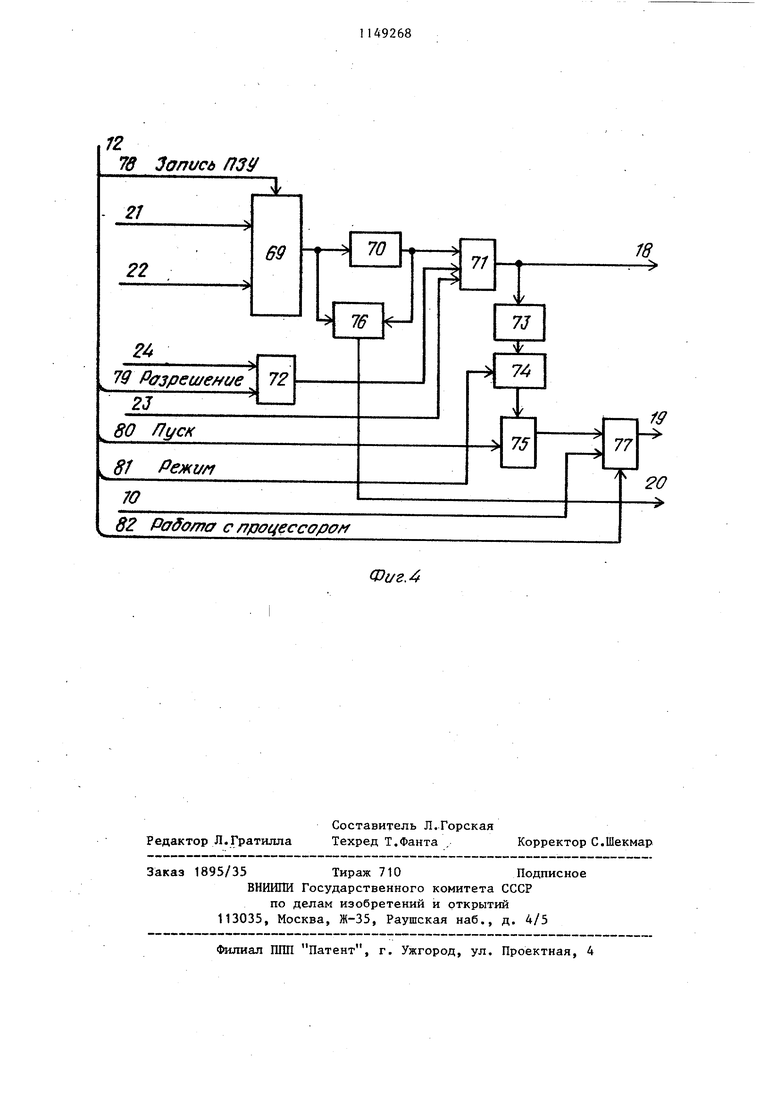

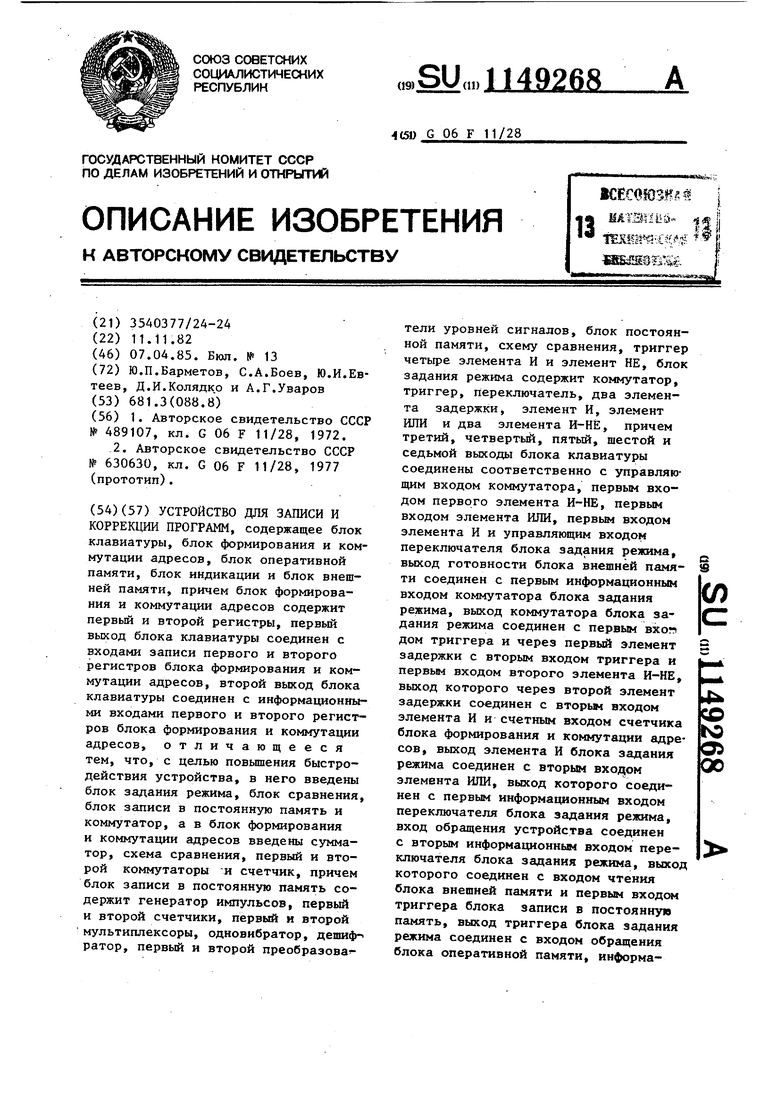

Изобретение относится к вычислительной технике и может быть исполь зовано для отладки программ микроЭВМ и микропроцессорных устройств. Известно устройство отладки прог рамм для постоянного запоминакнцего устройства, содержащее блок регистров, распределитель, блоки формирования адреса и адреса участка, блок управления, запоминающее устройство без разрушения информации, блок приема и выд-ачи команд, блок подключения постоянного запоминакиде го устройства, числовые, адресные и командную шины l . Недостатками данного устройства являются отсутствие возможности занесения откорректированной программы в ПЗУ, а также необходимость ручного набора адреса исправляемой команды, что затрудняет корректиров ку, связанную со значительными изменениями программ. Наиболее близким к изобретению по технической сущности является устройство для отладки программ, со держащее блок клавиатуры, регистры, оперативную память, перфоратор, накопитель на магнитной ленте 2J. Недостатками известного устройст ва являются необходимость применени дополнительной аппаратуры для занесения программ в постоянное запоминакицее устройство, а также сложност введения пропущенных команд и, как следствие, низкая производительност при отладке программ. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для записи и коррекции программ, содержащее блок клавиатуры, блок формирования и ком мутации адресов, блок оперативной памяти, блок индикации и блок внешней памяти, причем блок формирования и коммутации адресов содержит первый и второй регистры, первь(й вькод блока клавиатуры соединен с входами записи первого и второго регистров блока формирования и коммутации адресов, второй выход блока клавиатуры соединен с информационными входами первого и второго регистров блока формирования и коммутации адресов, введены блок задания режима, блок сравнения, блок записи в постоянную память и коммутатор, а в блок формирования и коммутации адресов введены сумматор, схема сравнения первый и второй коммутаторы и счетчик, причем блок записи в постоянную память содержит генератор импульсов, первый и второй счетчики, первьй и второй мультиплексоры, одновибратор, дешифратор, первый и второй преобразователи уровней сигналов, блок постоянной памяти, схему сравнения, триггер, четыре элемента И и элемент НЕ, блок задания режима содержит коммутатор, триггер, переключатель,два элемента задержки, элемент И, элемент ИЛИ и два элемента И-НЕ, причем третий, четвертый, пятый,шестой и седьмой выходы блока клавиатуры соединены соответственно с управляю1цим входом коммутатора, первым входом первого элемента И-НЕ, первым входом элемента ШШ, первым входом элемента И и уп14авляющим входом перек:вочателя блока задания режима, выход готовности блока внешней памяти соединен с первым информахшонным входом коммутатора блока задания режима, выход коьо утатора блока задания режима соединен с nepaiM входом триггера и через первый элемент задержки с вторьм входом триггера и первьм входом второго элемента И-НЕ, выход которого через второй элемент задержки соединен с вторьм входом элемента И и счетнь входом счетчика блока формирования и коммутации адресов, выход элемента И блока задания режима соединен с вторым входом элемента ИЛИ, выход которого соединен с первьм информационным входом переключателя блока задания режима, вход обращения устройства соединен с вторым информационным входом переключателя блока задания режима, выход которого соединен с входом чтения блока внешней памяти и первым входом триггера блока записи в постоянную память, выход триггера блока задания режима соединен с входом обращения блока оперативной памяти информационньй выход которого соединен с первым входом коммутатора и первым входом блока сравнения, выход блока сравнения соединен с вторым входом первого элемента И-НЕ блока задания режима, выход первого элемента И-НЕ блока задания режима соединен с вторым входом второго элемента И-НЕ блока задания режима, информационньй вькод первого регистра блока формирования и коммутации адресов соединен с входом первого операнда сумматора и с первым информационным входом первого коммутатора выход которого соединен с входом блока индикации, информационный выхой второго регистра блока формирования и коммутадаи адресов соединен с вторым информационным входом первого коммутатора и первым входом схемы сравнения, вькод которой соединен с третьим входом второго элемента И-НЕ блока задания режима, вход записи счетчика блока формирования и коммутации адресов соединен с первым выходом блока клавиатуры, информационный выход счетчика соединен с вторьм входом схемы сравнения третьим информационным входом первого коммутатора, входом второго операнда сумматора и адресным входом блока оперативной памяти, адресный вход устройства соединен с первым информационным входе второго коммутатора блока формирования и коммутации адресов, вькод которого соединен с четвертьи информационным входом первого коммутатора блока формироваНИИ и коммутации адресов, адресными входами блока внешней памяти, адресньй4и входами блока постоянной памяти блока записи в постоянную память, первьй выход блока клавиатуры соедиг ней с управляющими входами первого и второго коммутаторов блока формиро вания и коммутации адресов, второй выход блока клавиатуры соединен с вторым информационным входом коммута-j тора, выход которого соединен с вторым входом блока индикации, входом блока сравнения, с информационными входами блока оперативной памяти, блока внешней памяти, с информационным- входом первого мультиплексора, блока записи в постоянную память, восьмой, девятьй и десятый выходы блока клавиатуры соединены соответственно с управляющим входом коммутатора, с входом записи блока внешней памяти, с первым входом первого элемента И блока записи в постоянную память, выход первого элемента И блока записи в постоянную память соединен с вторым входом триггера, единичный выход которого соединен с входом разрешения счета первого счетчика и счеткым входом второго счетчика блока записи в постоянную память, выход генератора импульсов соединен со счетным входом первого счетчика, информационный выход которого соединен с первыми входами второго и третьего элементов И блока записи в постоянную память, выход переполне ния первого счетчика блока записи в постоянную память через элемент НЕ соединен с вторым входом третьего элемента И, выход которого соединен с первым входом четвертого элемента И блока записи в постоянную память, выход схемы сравнения блока записи в постоянную память соединен с вторым входом четвертого элемента И, выход которого соединен с информационным входом второго счетчика, информационный выход которого соединен с информационными входами первого и второго мультиплексоров и первым входом дешифратора блока запи си в постоянную память, выходы первого и второго мультиплексоров блока записи в постоянную память соединены соответственно с первым и вторым входами схемы сравнения, выход первого мультиплексора блока записи в постоянную память соединен с вторым входом второго элемента И, выход которого соединен с вторым входом дешифратора и первым входом первого преобразователя уровней сигналов, выход которого соединен с информационным входом блока постоянной памяти и через второй преобразователь уровней с вторым входом мультиплексора и с третьим информационным входом коммутатора, выход второго счетчика блока записи в постоянную память через одновибратор соединен с вторым входом первого элемента И блока записи в постоянную память и с вторым информационным входом коммутатора блока задания режима, выход дешифратора блока записи в пос тоянную память соединен с вторым входом первого преобразователя уров ней сигналов, информациоиньй выход блока внешней памяти соединен с четвертым информационным входом коммутатора и является информационнь1м выходом устройства, одиннадцатый выход блока клавиатуры соединен с входом чтения блока оперативной памяти. На фиг. 1 приведена структурная схема устройства для записи и корре ции программ; на фиг. 2 - структурные схемы блока записи в постоянную памятьi на фиг. 3 - блок формирования и коммутации адресов; на фиг.4 блок задания режима. Устройство содержит блок 1 задания режима, блок 2 сравнения, блок 3 формирования и коммутации адресов блок А индикации, блок 5 оперативной памяти, коммутатор 6, блок 7 клавиатуры, блок 8 записи в постоян .кую память, блок 9 внешней памяти; вход 10 блока 1, вьпсод 11 блока 7, входы 12-17 блока 1, блока 3 формирования и коммутации адресов, блоков 5 и 8, блока 9 внешней памяти и коммутатора 6, выходы 18-20 блока 1, выходы 21 и 22 блоков 9 и 8, выход 23 блока 3 формирования и коммутации адресов, выход 24 сигнала Совпадение блока 2 сравнения, адресные входы 25 блоков 8 и 9, адрес ный вход 26 блока 5, адресный вход 27 устройства, выход 28 блока 7, информационные входы 29 и 30 блока 3 формирования и коммутации адресов и коммутатора 6, выход 31 индикации блока 3 формирования и коммутации адресов, выход 32 коммутатора, выходы 33 и 34 блоков 8 и 9 и триггер 35, элемент И 36, генератор 37 импульсов, счетчик 38, элемент НЕ 39, элементы И 40 и 41, мультиплексор 42, схему 43 сравнения, элемент И 4 счетчик 45, мультиплексор 46, однов ратор 47, дешифратор 48, преобразователи 49 и 50 уровней сигналов; 686 блок 51 постоянной памяти, выход 52 мультиплексора 42, выход 53 мультиплексора 46, выход 54 схемы сравнения, вход/выход 55 блока 51, выход 56 преобразователя 50 уровня, счетчик 57, регистры 58 и 59, схему 60 сравнения, сумматор 61, коммутаторы 62 и 63, входы 64-66 занесения информации счетчика.и регистров, входы 67 и 68 коммутаторов, коммутатор 69, элемент 70 задержки, элементы И-НЕ 71 и 72, элемент 73 задержки, элемент И 74, элемент ИЛИ 75, триггер 76, переключатель 77, входы 7882. Блок 9 обеспечивает стирание, запись хранение к вьщачу по выходу 34 на вход коммутатора 6 и выход устройства кодов программ, а также формирование на выходе 21 стробового импульса, сопровождающего при чтении установление на выходе блока кода, считьшаемого с блока постоянной памяти слова, или конец операции при стирании и записи кода в блок постоянной памяти. Задание вида операции производится по входу 16 с блока 7, стробовый сигнал начала операции подается с выхода 19 блока 1, коды записываемых в блок постоянной памяти слов пересылаются с выхода 32 коммутатора 6. Блок 8 служит для записи кодов в блок постоянной памяти, считывания информации на вход ко «1утатора 6 и формирования на выходе 22 стробового импуль-. са окончания записи слова в блок постоянной памяти. Сигнал Запись подается по управляющему входу 15 с выхода 11 блока 7, стробовый сигнал начала записи - с выхода 19 блока 1, код прожигаемого слова поступает с выхода 32 коммутатора 6. Блок 8 обес печивает также формирование и индикацию сигнала неисправимой ошибки, возникающей при программировании лишнего разряда или при несоответствии адресации блока постоянной памяти паспортным данным. Кою утатор 6 служит для подключения на вход блсжа памяти, в который записывается информация, выхода блока-источника информации. В качестг не последнего могут выступать блоки 5-9, соединенные своиьш выходами с информационнь ш входами коммутатора. Приемникаьш могут быть блоки 5, 8 и 9, соединенные своиими информационными входами;i с выходом 32 коммутатора 6, а также блок 4 индикации, постоянно воспроизводящий код выхода коммутатора на световом табло. Адрес коммутируемого канала задается по управлякяцему входу 17 блока 7.

Блок 7, соединенный информационным выходом 28 через вход блока 3 . формирования и коммутации адресов с информационными входами счётчика 57 адресов, регистров 58 и 59, а также через коммутатор 6 - с информационнь1ми входами блоков 5, 8 и 9 и блока 4 индикации, осуществляет подачу начального и конечного адресов выбираемого сегмента памяти с произвольным доступом блока 5 и кода смещения адреса внешней памяти относительно адреса в блок 3, подачу кодов слов в запоминающие устройства с их одновременной индикацией блоком 4,

Выкод 11 блока 7 соединяется груповыми линиями связи с входами 12, 13, 16 и 17 блока 1, блока 3 формир вания и коммутации адресов, блока 9 внешней памяти, коммутатора 6 и одиночными линиями связи с входами 14 и 15 блока 5 памяти с произвольным доступом и блока 8.

С выхода 11 блока 7 задаются режим работы устройства (работы с вычислительным устройством, автоматического чтения, контроля или записи участка программы, однократного чтения или записи по адресу), вид выполняемой операции - запись в блок 5 (вход 14), запись в блок 9 внешней памяти (вход 16) прожиг блока 51 (входы 15 и 78), стирание информации в блоке 51 (вход 16),

Управлякйций выход служит также для подачи стробов занесения информации в счетчик 57 (вход 64) и ре.гистры 58 и 59 (входы 65 и 66) для разрешения или запрещения подачи синала сравнения на элемент И-НЕ 71, (вход 79) для подачи стробового сигнала Пуск (вход 80) в блок 1.

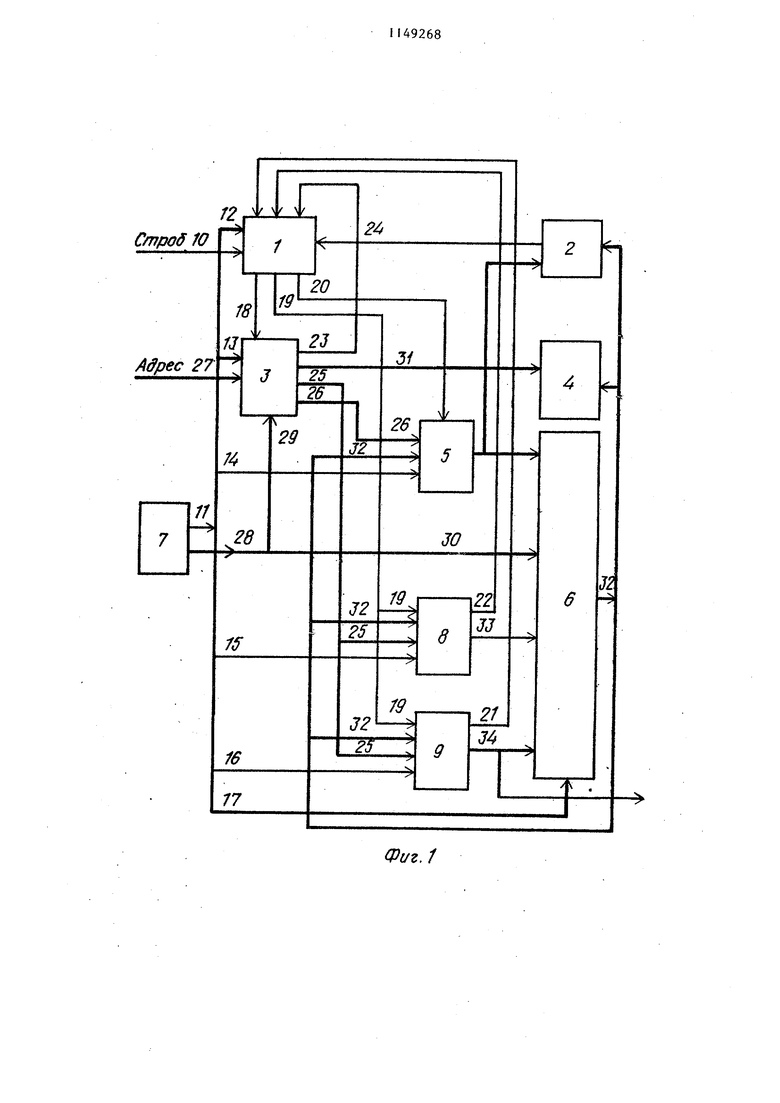

Блок t формирует на выходах 18 и 19 сигналы стробирования счетчика 57 адресов, блоков 9 и 8, а также н выходе 20 сигнал Выбор микросхемы блока 5, используемый последним при записи информации. Необходимая длительность цикла считывания информации с блока внешней памяти обеспечивается элементами 70 и 73 задержки, длительность импульса Выбор микросхемы в режиме записи и момент его подачи - элементом 70, которая также задерживает прохождение стробового импульса с коммутатора 69 на элемент И-НЕ 71 до момента установления сигнала сравнения на втором ее входе

Элемент И-НЕ 71 служит для запрещения или разрешения прохождения стробового сигнала на счетчик 57 и элемент И 74 по уровням сигналов со схем 2 и 60 сравнения сигнала по входу 79.

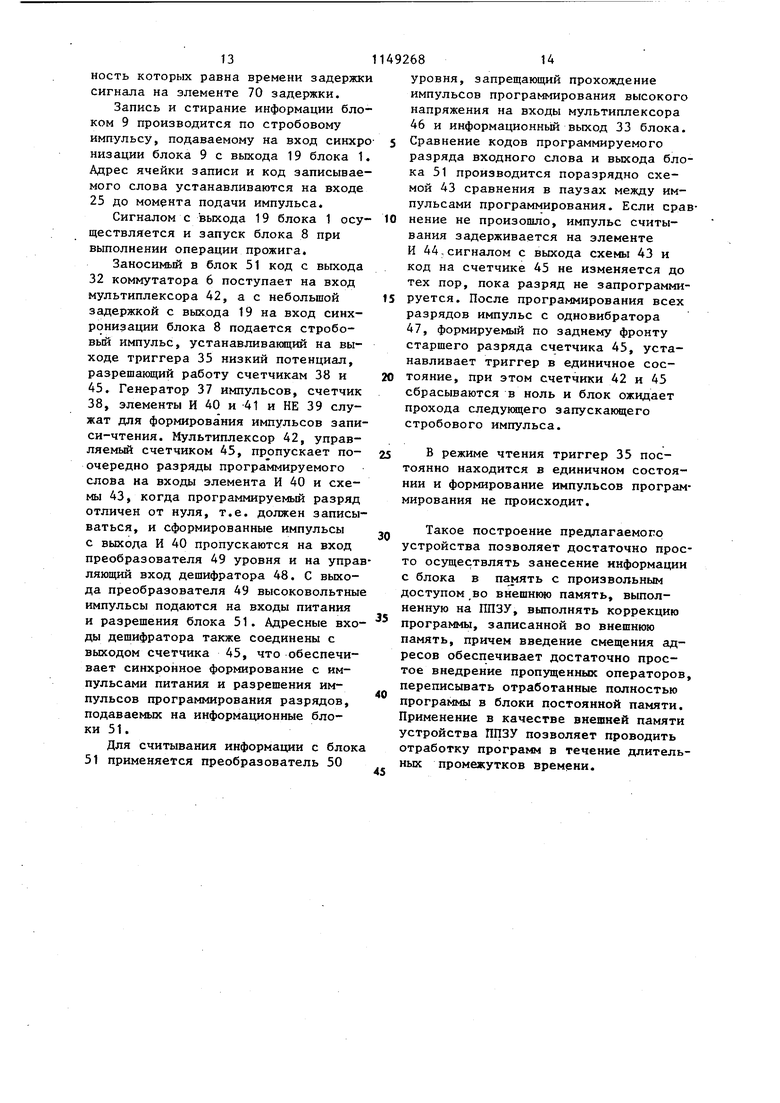

Блок 3 формирования и коммутации адресов осуществляет адресацию блоков 5, 8 и 9, с помощью коммутатора 62 по выходу 31 производит выдачу кодов текущего адреса блоков 5 и 9 и блока 5 конечного адреса и кода смещения в блок 4 индикации, выполняет коммутацию коммутатором 63 адреса блока 9 внешней памяти с внешнего источника адреса, поступающего на вход 27, или осуществляет с выхода сумматора 61 формирование схемой 60 сравнения сигнала Окончание операции при совпадении текущего адреса блока 5 и конечного адреса, записанного в регистре 58.

БЛОК 8 обеспечивает подачу импульсов высокого напряжения в режиме прол;я1 3 на информационные входы-выходы 5./ блока 51, а также на входы Питание и Выбор микросхемы путем инверсии и умощнения импульсов с выходов дешифратора 48 и элемента И 40 преобразователем 49 уровней сигналов. Дешифратор 48, соединенный адресньм входом с выходом счетчика 45 прожигаемого разряди -и управляющим входом с выходом элемента И 40, формирукяцего импульс записи при единичном значении программируемого разряда, служит для подачи импульса прожига через преобразователь 49 уровня на тот вход блока 51, который подлежит программированию. Генератор 37 тактовых импульсов, счетчик 38, элемент НЕ 39, элементы И 40 и 41 предназначены для формирования пос,ледовательности импульсов записи ( элемента 40) и чтения (выход элемента 4,1) с заданной длительностью и скважностью. Триггер 35, соединенный выходом со схемами установки в ноль счетчиков 38 и 45, управляет работой, последних, устанавли9вая их в исходное (нулевое) состояние и разрешая или запрещая изменение значений на выходе. Счетчик 45 номера программируемого разряда (кроме дешифратора) задает номер коммутируемого канала мультиплексору 42, пропускающему поразрядно код программируемого слова и мультиплексору- 46, входом которого является информационный выход блока 51, пропускаемый через преобразователь 50 уровня. Разряд программируе мого слова с выхода мультиплексора 42 проходит на третий вход элемент И 40 и в зависимости от значения пропускает или запрещает прохождени импульса записи на его выход. Одноразрядная схема 43 сравнения вьшолняет сравнение значений разрядов программируемого слова и выхода блока 51, разрешая проход импульса чтения через элемент И 44 на счетчик 45 разрядов при совпадении и запрещая при несовпадении, а также, вырабатывает и индицирует сигнал Неисправимая ошибка, если значени разряда блока 51 равно 1, а програм мируемого слова - 0. Устройство работает следующим Ьбразом. I Отладки программ осуществляют выполнением операций первоначального занесения кодов команд программы с блока 7 в блок 5, визуальной про верки по индикации блока 4 правильности занесения кодов программы, перезаписи программы в блок 9, конт роля перезаписи сравнением содержимого блоков 5 и 9 схемой 2 сравнени выявления ошибок в программе путем анализа ее выполнения на вычислительном устройстве, подключаемом к блоку 9 внешней памяти (если конкретное выполнение ВУ не допускает размещение программы во внешней памяти, последняя также может быть пе реписана с блока внешней памяти в память ВУ через стандартные блоки параллельного обмена) корректировки программы в блоках 5 и 9 и записи ее отлаженного варианта (в случае необходимости) в интегральные схемы блока 51. Корректировка программы может заключаться в исправлении кодов команд, вставке или удалении отдельных команд, или целых блоков программы. Исправление ошибок в кодах 68 команд в зависимости от вида ошибки (замена 1 на О или О на Г ) и с интегральных схем перепрограммируемых постоянных запоминающих устройств (ИС ПИЗУ), применяемых в блоке 9, может быть выполнено непосредственной записью правильного кода в блок внешней памяти с блока 7 либо с предварительным исправлением информации в блоке 5, стиранием содержимого блока -9, записью в блок 9 исправленной программы, сравнением содержимого блоков 5 и 9 с целью контроля правильности записи информации. При вставке или удалении команд программа переписывается из блока внешней памяти в блок памяти с произвольным доступом, причем та часть программы, в которой изменилась нумерация команд, переписывается с соответствующим смещением адресации блока 9 относительно блока 5, задаваемьм с блока 7.После записи добавляемых команд исправленная программа вновь заносится в блок внешней памяти. Помимо отладки программ устройство позволяет также дублировать содержимое блока 51 с программами или таблицами, записанными ранее, исправлять восстановившиеся или запрограммировавшиеся в процессе эксплуатации разряды, осуществлять контроль правильности занесенной в блок 51 информации. При дублировании содержимого блока 51 эталонная схема устанавливается в блоке 8, после переписи информации со схемы в блок 5 памяти она заменяется на схему, подлежащую программированию (прожигу). Управление работой устройства осуществляется с блока 7, при этом устройство может записьгаать коды команд с блока 7 в один из блоков 5 и 9 или программировать блок 51, переписывать информацию из одного блока памяти в другой, переписывать информацию в выбранный блок памяти, сравнивать содержимое блока 5 памяти с содержимым внешней памяти блока 51 или с кодом, набираемым на блоке 7, индицировать содержимое блоков памяти, выхода блока 7 или блока 51, выводить информацию из внешней памяти по запросу и адресации другого стройства. Вид операции, выполняемой устройтвом, задается с помощью переключа-, елей блока 7.

Адреса блоков 5 и 9 могут совпадать или различаться на величину, задаваемую с блока 7, адрес внешней памяти может вводиться также извне устройства по входу 27. Формируемые адреса и смещение индицируются на блоке 4 индикации.

Перед началом выполнения операций 1C помощью переключателей блока 7

задается вид выполняемой операции, режим подачи стробовых сигналов в блок 7 формирования и коммутации адресов (одиночный или автоматический) , разряд Разрешение операции сравнения, устанавливаются коды управления коммутаторами 6, 62 и 63, в блок 3 пересылаются коды начального и конечного адресов, пёресьшается код смещения адресов блока 8 относительно адресов блока 5. Подачей стробового импульса Пуск осуществляется запуск устройства. Если производится пересьшка информации с внешней памяти на выход устройства .по запросу и адресации с другого устройства, задание адресов и смещение не производятся и стробовьй импульс с блока 7 не подается. При пересыпке начального и конечного адресов и кода смещения в счетчик 57 и регистры 58 и 59 блока 3 переключателями блока 7, соединенными с управлякяцими входами коммутатора 6, набирается код канала блока 7, что позволяет контролировать набираемые коды на световом табло блока 4. На информационном выходе блока 7 набира ется код пересьшаемого слова и с управлякщего выхода через вход блока 3 подается строб занесения в выбранньй регистр или счетчик, фиксирующий установленную на соединенных параллельно информационных входах блоков 57-59 информацию.

Изменение кода счетчика 57 производится импульсами, подаваемыми на стробовый вход 18 счетчика с первого выхода блока 1. По достижении кодом на выходе значения конечного адреса, зафиксированного регистром 58, на выходе 23 блока устанавливается сигнал совпадения, формируемый схемой 60 сравнения, запрещающий прохождение импульсов через элемент И-НЕ 71 блока 1 на стробовый вход 18 счетчика. 57.

Адрес блока 5 памяти подается непосредственно с выхода 26 счетчика 57, адрес внешней памяти и блока 51 либо пропускается коммутатором 63 от внешнего источника, либо получается суммированием кодов счетчика 57 и регистра 59 смещения на сумматоре 61.

Формирование импульсов стробирования счетчика адреса осуществляется блоком 1 по стробовым импульсам,

пропускаемым по входу 22 переключателем 69 с блока 8 при выполнении операции программирования блока 51 или же по входу 21 с блока 9 во всех остальных случаях. Инвертированный импульс с выхода переключателя 69 через элемент 70 задержки подается на вход элемента И-НЕ 71. Если на двух других его входах держится .высокий потенциал, стробовый

импульс проходит на выходе 18 блока 1, если при кысоком потенциале на шине 79 Разрешение на втором входе элемента 72 установится высокий потенциал, соответствующий несовпадению кодов на входах блока 2, элемент 71 также, как и при совпадении кодов на входе схемы 60, запретит проход стробовых импульсов на выход 18 блока 1 и навход элемента 73

0 задержки. При низком потенциале на шине 79 Разрешение влияние результата сравнения кодов блоком 2 на прохождение импульсов через элемент И-НЕ 71 исключается.

5 Стробовые импульсы, проходящие с выхода элемента И-НЕ 71 через элемент задержки, поступают на элемент И 74, второй .вход которого соединен с выходом 81 переключателя режимов

0 блока 7. Если выбран режим автоматический, высокий потенциал на этом входе не препятствует проходу импульса через элементы И 74 и ИЛИ 75, переключатель 77 на выход 19 устройства. В режиме подачи одиночных импульсов (нулевое значени е на управляемом входе элемента И 74 постоям но держит нулевое значение и на его выходе) через элемент ШШ 75 могут проходить только стробовые импульсы по входу 80 с блока 7.

Переключатель 77 в зависимости от уровня сигнала на управляилдем входе 82 пропускает на выход импульсы

3 либо с выхода элемента 75, либо по входу 10 с внешнего источника.

Триггер 76 формирует импульсы записи информации блоку 5, длительность которых равна времени задержк сигнала на элементе 70 задержки. Запись и стирание информации бло ком 9 производится по стробовому импульсу, подаваемому на вход синхр низации блока 9 с выхода 19 блока 1 Адрес ячейки записи и код записывае мого слова устанавливаются на входе 25 до момента подачи импульса. Сигналом с выхода 19 блока 1 осу ществляется и запуск блока 8 при выполнении операции прожига. Заносимьй в блок 51 код с выхода 32 коммутатора 6 поступает на вход мультиплексора 42, ас небольшой задержкой с выхода 19 на вход синхронизации блока 8 подается стробовый импульс, устанавливающий на выходе триггера 35 низкий потенциал, разрешающий работу счетчикам 38 и 45. Генератор 37 импульсов, счетчик 38, элементы И 40 и 41 и НЕ 39 служат для формирования импульсов запи си-чтения. Мультиплексор 42, управляемый счетчиком 45, пропускает поочередно разряды программируемого слова на входы элемента И 40 и схемы 43, когда программируемый разряд отличен от нуля, т.е. должен записы ваться, и сформированные импульсы с выхода И 40 пропускаются на вход преобразователя 49 уровня и на упра ляющий вход дешифратора 48. С выхода преобразователя 49 высоковольтны импульсы подаются на входы питания и разрешения блока 51. Адресные вхо ды дешифратора также соединены с выходом счетчика 45, что обеспечивает синхронное формирование с импульсами питания и разрешения импульсов программирования разрядов, подаваемых на информационные блоки 51 . Для считывания информации с блок 51 применяется преобразователь 50 6814 уровня, запрещающий прохождение импульсов программирования высокого напряжения на входы мультиплексора 46 и информационньм выход 33 блока. Сравнение кодов программируемого разряда входного слова и выхода блока 51 производится поразрядно схемой 43 сравнения в паузах между импульсами программирования. Если оравнение не произошло, импульс считывания задерживается на элементе И 44.сигналом с выхода схемы 43 и код на счетчике 45 не изменяется до тех пор, пока разряд не запрограммируется. После программирования всех разрядов импульс с одновибратора 47, формируемый по заднему фронту старшего разряда счетчика 45, устанавливает триггер в единичное состояние, при этом счетчики 42 и 45 сбрасываются в ноль и блок ожидает прохода следукнцего запускающего стробового импульса. В режиме чтения триггер 35 постоянно находится в единичном состоянии и формирование импульсов программирования не происходит. Такое построение предлагаемого устройства позволяет достаточно просто осуществлять занесение информации с блока в память с произвольным доступом во внешнкяо память, выполненную на ППЗУ, выполнять коррекцию программы, записанной во внешнюю память, причем введение смещения адресов обеспечивает достаточно простое внедрение пропущенных операторов, переписывать отработанные полностью программы в блоки постоянной памяти. Применение в качестве внешней памяти устройства ППЗУ позволяет проводить отработку программ в течение длительных промежутков времени.

16

/J

м

/

57

5,8

Фиг. 2

27

±

165

f

59

6 Г

/ W f

62

26

23

Л Ф{/г.J

/

67

68

5J

25

78 Запись ПЗУ

Фиг,4 79 Pff3psu/efff/e 80 Луск 81 Режи/ 82 Робота с npocfeccopffff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство отладки программ для постоянного запоминающего устройства | 1972 |

|

SU489107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отладки программ | 1977 |

|

SU630630A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1982-11-11—Подача