Изобретение относится к области вычислительной техиики.

Известны однородные вычислительные среды, содержащие матрицу структурно избыточных ячеек с перестраиваемыми функциональными блоками и блоки перестройки ячеек по числу строк матрицы, каждый из которых содержит регистры и коммутатор, входы которого соединены с выходами регистров.

Общим недостатком известных однородных вычислительных сред является относительно низкая функциональная .надежность.

В предложенной однородной вычислительной среде указанный недостаток в значительной мере устранен.

Это достигнуто тем, что каждая ячейка вычислительной среды содержит дополнительные схемы запрета, схему антисовпадения и разделительный диод. Выход индикатора отказов функционального блока .каждой ячейки f-й строки матрицы соединен со входом дополнительной схемы антисовпадения той же ячейки и через разделительный диод соединен с f-й щиной индикации отказов, подключенной ко входам дополнительных схем антисовпадения всех ячеек i-й строки матрицы и к управляющему входу коммутатора блока перестройки ячеек той же строки. Выход до.полнительной схемы антисовпадения каждой ячейки соединен со входами всех дополнительных

2

схем запрета той же ячейки, выходы которых соединены с управляющими входами перестраиваемого функционального блока ячейки. Вторые входы /-х дополнительных схем запрета всех ячеек i-fi строки матрицы соединены с -/-м выходом коммутатора блока перестройки ячеек той же строки. Последний выход коммутатора соединен с кле.ммой индикации невосстанавливаемых отказов.

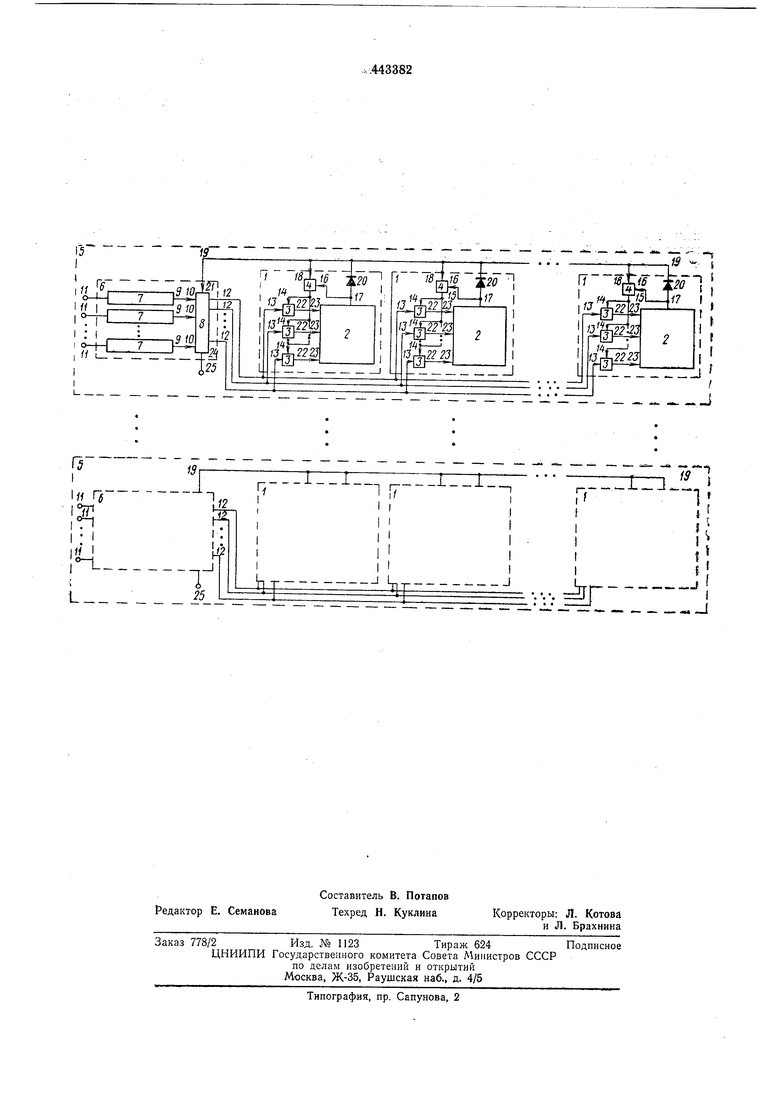

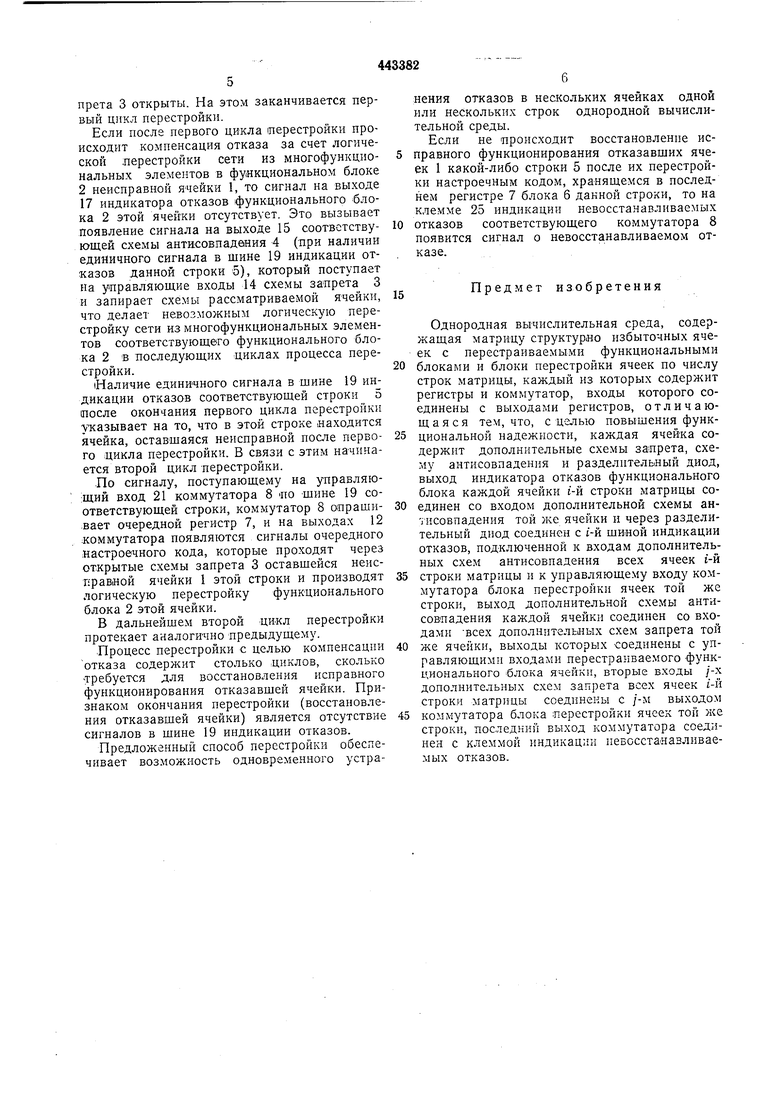

Блок-схема однородной вычислительной среды приведена на чертеже.

Для упрощения описания процесса настройки функциональных блоков среды iia реализацию заданной функции и процесса перестройки среды при появлении отказов на чертеже не указаны функциональные связи между ячейками, а приведены только связи, используемые в процессе настройки и перестройки.

Однородная вычислительная среда состоит

из объединенных в матрицу структурно избыточных ячеек , в состав каждой из которых входят перестраиваемый функциональный блок 2, выполненный, например, в виде логически устойчивой сети из многофункцпональных элементов с кодовой перестройкой логики, схе.мы запрета 3 и схема аятисовпадения 4.

В состав каждой строки 5 матрицы ячеек 1 входит блок 6 перестройки ячеек, состоящий из хранящих настроечные коды для

перестройки блоков 2 регистров 7 (по числу циклов перестройки), необходимых для обеспечения логической устойчивости сети из многофункциональных элементов перестраиваемого функционального блока 2 любой ячейки 1 строки 5 в классе реализуемых функций, и коммутатор 8 выходов регистров 7. Выходы 9 каждого регистра 7 подключены к входным шииам 10 коммутатора 8, а входы 11 регистров 7 соединены с выходными шинами запоминающего устройства настроечных кодов функций, реализуемых ячейками 1 однородной вычислительной среды.

Каждый из выходов 12 коммутатора 8 подключен к функциональному входу 13 одной из схем запрета 3 каждой ячейки 1 соответствующей строки 5 однородной среды. Управляющие входы 14 схем запрета 3 каждой ячейки 1 соединены параллельно и подключены к выходу 15 схемы антисовпадения 4, управляющий вход 16 которой соединен с выходом 17 индикатора отказов функционального блока 2.

Функциональный вход 18 каждой схемы антисовпадения 4 иодключен к шине 19 индикации отказов соответствующей строки 5 матрицы. Шина 19 каждой строки соединена разделительные диоды 20 с выходами 1/ индикаторов отказов перестраиваемых функциональных блоков 2 этой строки и подключена к управляющему входу 21 соответствующего коммутатора 8, а выходы 22 схем запрета 3 каждой ячейки 1 соединены с управляющими входами 23 соответствующего -перестраиваемого функционального блока 2.

Сигналы, поступающие на управляющие входы 23 функционального блока 2, производят его настройку на реализацию заданной функции.

Выход 24 коммутатора 8 строки 5 подключен к клемме 25 индикации невосстанавливаемых отказов.

Если перед началом работы все ячейки 1 однородной вычислительной среды находятся ,в исправном состоянии, то процесс настройки любой строки 5 на реализацию произволоной из класса реализуемых функций осуществляется следующим образом.

В регистры 7 блока 6 перестройки ячеек 1 каждой строки из запоминающего устройства заносятся настроечные коды, обеспечивающие настройку на.заданную функцию, во всем диапазоне логической устойчивости сетей из многофункциональных элементов перестраиваемых функциональных блоков 2 соответствующей строки 5 однородной вычислительной среды. Настроечные коды с выходов 9 регистров 7 поступают на входы 10 коммутатора 8, который пропускает на выходы 12 только код с первого регистра 7. Первым регистром считается тот, в котором хранится настроечный код, обеспечивающий логическую устойчивость функциональных блоков 2 к максимальному числу отказов, компенсируемых на одном настроечном коде. Следующие по порядку регистры 7 содержат настроечные коды, обеспечивающие убывающую способность функционального блока 2 к компенсации отказов. При этом совокупность всех настроечных кодов обеспечивает компенсацию в 5 функциональном блоке 2 всех возможных отказов. Настроечные коды с выходов 12 коммутаторов 8 поступают на функциональные входы (13 схем запрета 3 каждой ячейки 1 соответствующей строки 5 вычислительной

10 среды.

В связи с тем, что ячейки 1, как было условлено, находятся в исправном состоянии, то сигналы иа выходах 17 индикаторов отказов функциональных блоков 2 и в шине 19 индикации отказов каждой строки отсутствуют, и на управляющие 16 и функциональные 18 входы схем антисовпадения 4 поступают нулевые потенциалы. Это обуславливает отсутствие сигналов на выходах 15 схем аитисов0 -падения 4 и на управляющих входах 14 схем запрета 3. Сигналы, поступающие на функциональные входы 13 схем запрета 3, беспрепятственно проходят на управляющие входы 23 перестраиваемых функциональных блоков 2

5 ячеек каждой строки 5 и производят настройку каждого блока 2 соответствующей строки на реализацию заданной функции.

Настроенные таким способом ячейки 1 од0 иородной вычислительной среды функционируют без логической перестройки до тех пор, пока в одной из ячеек не появится отказ, обнаруживаемый в зависимости от принципа построения среды либо аппаратурной

5 системой контроля, либо с помощью тестового контроля.

При обнаружении неисправности в функциональном блоке 2 строки 5, приводящей к искажению выходного сигнала, на выходе 17

0 соответствующего индикатора отказов появится сигнал об отказе. Этот сигнал поступает на управляющий вход 16 соответствующей схемы антисовиадения 4 и, проходя через разделительный диод 20, поступит в шину 19

5 индикации отказов соответствующей строки 5, на функциональные входы 18 всех схем антисовиадения 4 данной строки и на управляющий вход 21 коммутатора 8. По этому сигналу коммутатор 8 опрашивает следующий по порядку регистр 7, и иа его выходы 12 поступает очередной настроечный код, который проходит на функциональные входы 13 схем запрета 3 всех ячеек 1 данной строки 5. Схемы запрета исправных ячеек этой строки

5 запираются, поэтому сигналы настроечного кода, поступающие на функциональные входы 13 схем запрета 3 исправных ячеек, не проходят на управляющие входы 23 перестраиваемых функциональных блоков 2 этих ячеек и

0 ие производят логической перестройки этих блоков. Логическая перестройка функционального блока 2 происходит лишь в той ячейке, в которой проявляется неисправность, приводящая к искажению выходного сигнала, так как только в этой ячейке схемы запрета 3 открыты. На этом заканчивается первый цикл перестройки.

Если после первого цикла перестройки происходит компенсация отказа за счет логической .перестройки сети из многофункциональных элементов в функциональном блоке 2 неисправной ячейки 1, то сигнал на выходе 17 индикатора отказов функционального блока 2 этой ячейки отсутствует. Это вызывает появление сигнала на выходе 15 соответствующей схемы антасовпадения 4 (при наличии единичного сигнала в шине 19 индикации отказов данной строки 5), который поступает на управляющие входы 14 схемы запрета 3 и запирает схемы рассматриваемой ячейки, что делает невозможным логическую перестройку сети из многофункциональных элементов соответствующего функционального блока 2 в последующих циклах процесса перестройки.

Наличие единичного сигнала в шине 19 индикации отказов соответствующей строки 5 после окончания первого цикла перестройки указывает на то, что в этой строке находится ячейка, оставшаяся неисправной после первого дикла перестройки. В связи с этим начинается второй цикл перестройки.

По сигналу, поступающему на управляющий вход 21 коммутатора 8 ПО шине 19 соответствующей строки, коммутатор 8 апраши.вает очередной регистр 7, и на выходах 12 коммутатора появляются сигналы очередного настроечного кода, которые проходят через открытые схемы запрета 3 оставшейся неисправной ячейки 1 этой строки и производят логическую перестройку функционального блока 2 этой ячейки.

В дальнейшем второй цикл перестройки протекает аналогично предыдущему.

Процесс перестройки с целью компенсации отказа содержит столько циклов, сколько -требуется для восстановления исправного функционирования отказавшей ячейки. Признаком окончания перестройки (восстановления отказавшей ячейки) является отсутствие сигналов в шине 19 индикации отказов.

Предложенный способ перестройки обеспечивает возможность одновременного устранения отказов в нескольких ячейках одной или нескольких строк однородной вычислительной среды. Если не происходит восстановление исправного функционирования отказавших ячеек 1 какой-либо строки 5 после их перестройки настроечным кодом, хранящемся в последнем регистре 7 блока б данной строки, то на клемме 25 индикации невосстанавливаемых

отказов соответствующего коммутатора 8 появится сигнал о невосстанавливаемом отказе.

Предмет изобретения

15

Однородная вычислительная среда, содержащая матрицу структурно избыточных ячеек с перестраиваемыми функциональными

блоками и блоки перестройки ячеек по числу строк матрицы, каждый из которых содержит регистры и коммутатор, входы которого соединены с выходами регистров, отличающаяся тем, что, с ц-глью повышения функциональной надежности, каждая ячейка содержит дополнительные схемы запрета, схему антисовпадения и разделительный диод, выход индикатора отказов функционального блока каждой ячейки t-й строки матрицы соединен со входом дополнительной схемы антисовпадения той же ячейки и через разделительный диод соединен с i-й шиной индикации отказов, подключенной к входам дополнительных схем антисовпадения всех ячеек t-й

строки матрицы и к управляюще.му входу коммутатора блока перестройки ячеек той же строки, выход дополнительной схемы антисовпадения каждой ячейки соединен со входами -всех дополнительных схем запрета той

же ячейки, выходы которых соединены с управляющими входами перестраиваемого функционального бло.ка ячейки, вторые входы /-х дополнительных схем запрета всех ячеек 1-й строки матрицы соединены с /-м выходом

коммутатора блока перестройки ячеек той же строки, последний выход коммутатора соединен с клеммой индикации невосста-навливаемых отказов.

} Р

t9W

.7

L qra

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| БЛОК НАСТРОЙКИ ЯЧЕЙКИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1973 |

|

SU407311A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| Ячейка однородной среды | 1989 |

|

SU1756898A1 |

| Однородная вычислительная среда | 1979 |

|

SU826336A1 |

| ЯЧЕЙКА МАТРИЧНОГО КОММУТАТОРА С ПОТОКОВОЙ НАСТРОЙКОЙ | 2001 |

|

RU2194302C2 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2133054C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

Авторы

Даты

1974-09-15—Публикация

1973-02-14—Подача