г-

112

Изобретение относится к вычисли- i тельной технике и может быть использовано в электронных вычислительных машинах устройствах вычислительной техники и автоматики, контроллерах и устройствах управления.

Цель изобретения - расширение области применени за счет возможности перезаписи, информации.

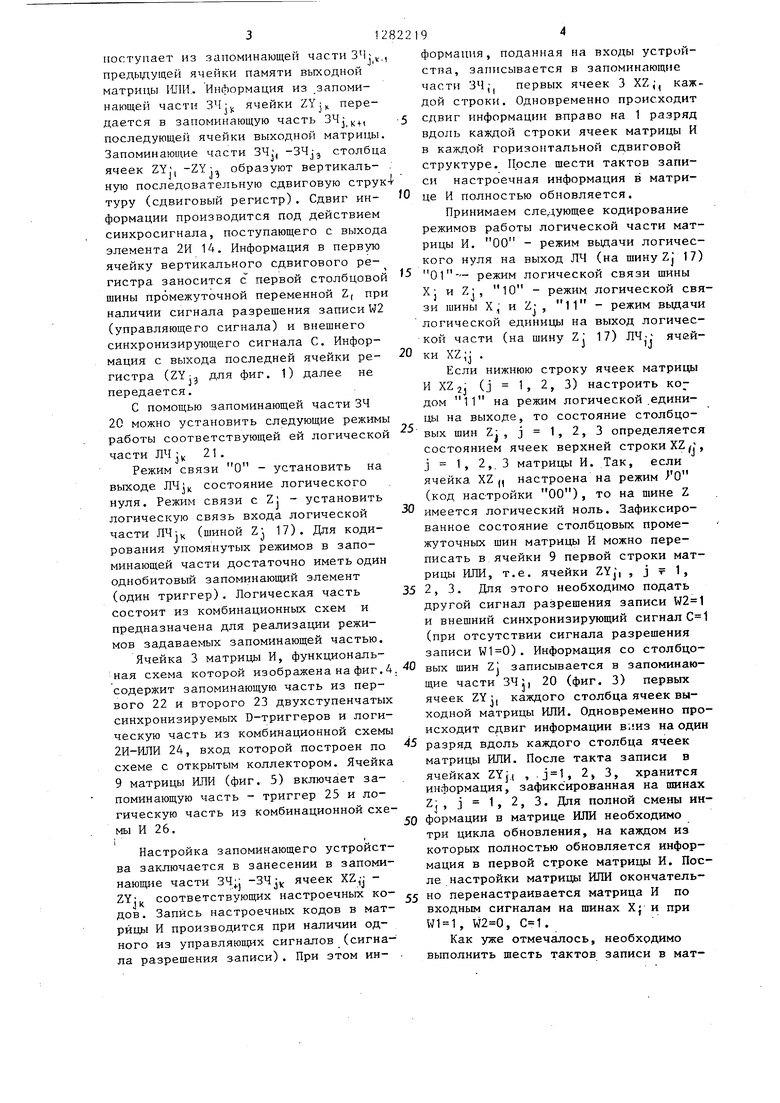

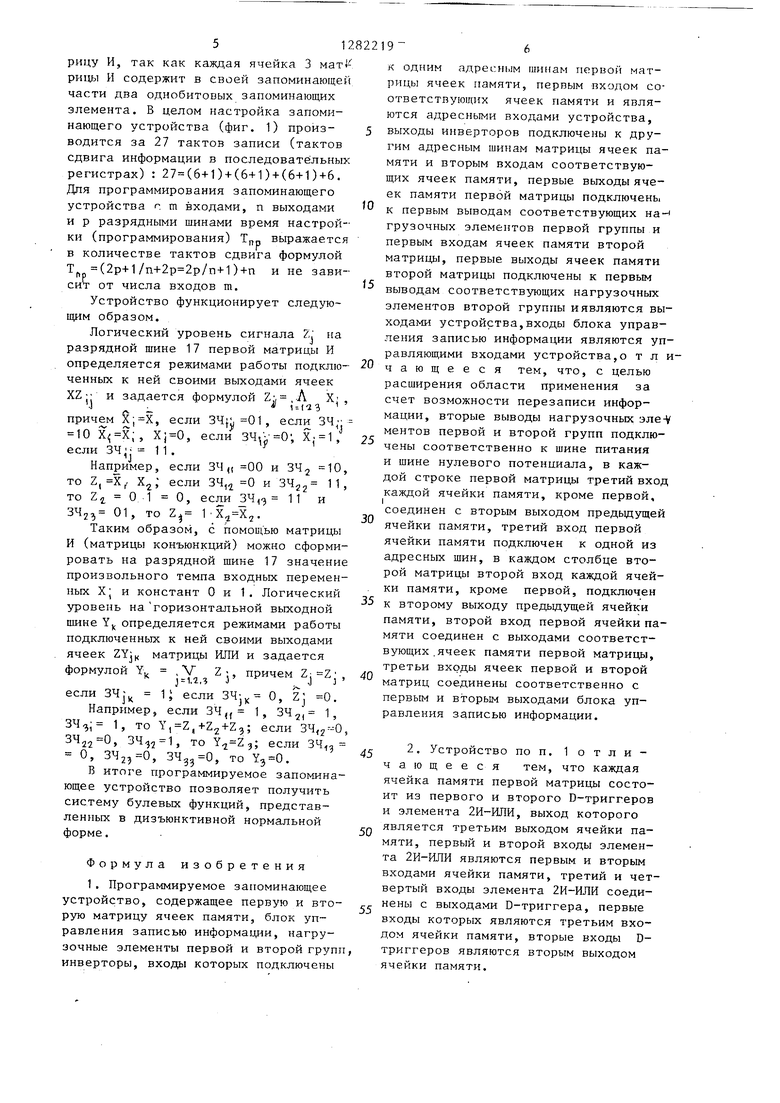

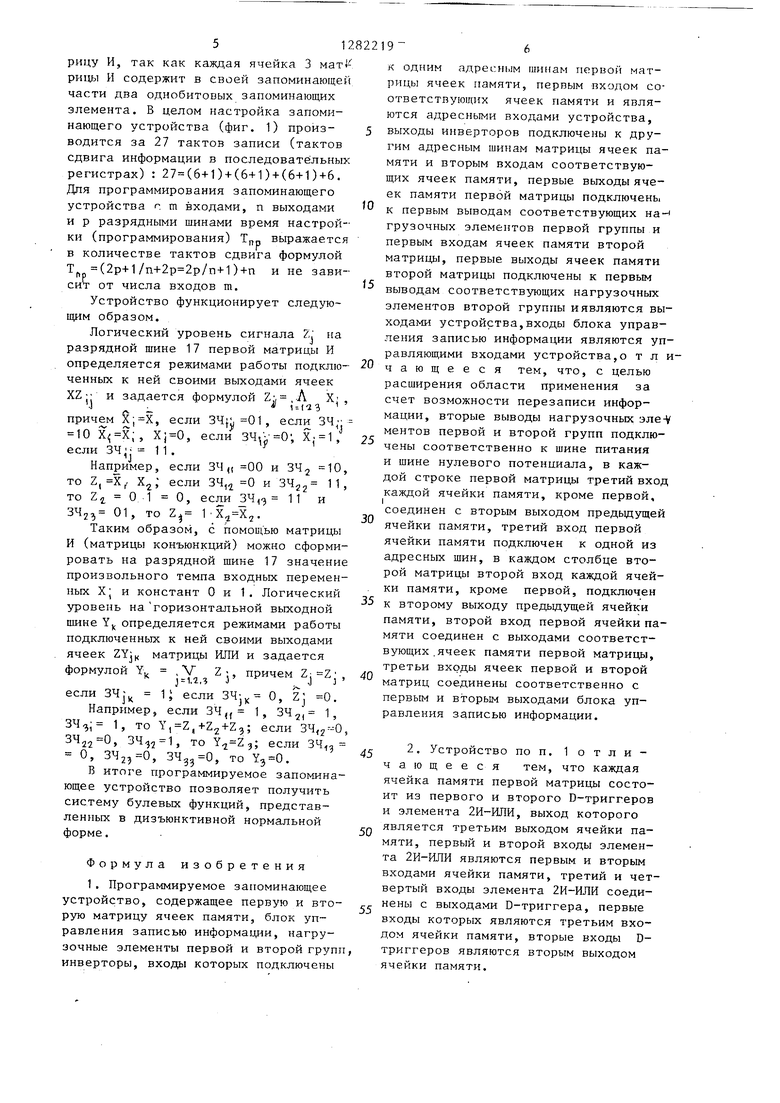

На фиг. 1 изображена структурная схема программируемого запоминающего устройства; на фиг. 2 - структурная схема ячейки памяти первой матрицы на фиг. 3 - структурная схема ячейки памяти второй матрицы/ на фиг.- 4 - функциональная схема ячейки памяти первой матрицы; на фиг. 5 - функциональная схема ячейки памяти второй матрицы

Программируемое запоминающее уст ройство содержит первую 1 и вторую 2 матрицы ячеек памяти. Первая 1 матрица ячеек 3 памяти состоит из адресных (строковых) шин 4 и 5, по кото- рым поступают входные напряжения Xj и Х„, инверторов 6, ячейки 3 памяти обвазуют входную матрицу И. Каждая из ячее|с 3 памяти через соответствующие нагрузочные элементы 7 первой группы подключены к шине 8 питания и ячейкам 9 памяти второй матрицы. Ячейки 9 памяти образуют выходную матрицу ШШ. Первые выходы ячеек 9 памяти соединены с одними из выводов нагрузочных элементов 10 второй группы и являются управляющими выходами 11 устройства, вторые выводы нагрузочных элементов 10 подключены к шине 12 нулевого потенциала. Блок 13 управления состоит из элементов 2И 14 и 15, одни входы которых являются синхронизирующими входами, а другие управляющими входами 16 устройства. По разрядным (столбцовьм) шинам 17 (Z) первой матрицы передаются сигналы промежуточных переменных Z , Zj, Zj. Ячейка 3 памяти представ

ляет собой совокупность ячеек XZ;. (J 1,2,3, i 1,2). Ячейка 9 памяти представляет собой совокупность ячеек ZYj| (J 1, 2, 3, , 2, 3), где Y - выходные шины 11, на которых формируются выходные переменные Y,;, .

Ячейка 3 памяти XZj (фиг. 2) содержит запоминающую часть 34jj 18 и логическую часть ЛЧ, 19. Запоминающая часть 34jj 18 предназначена для

20

8221

i 5

. к. а3я, :

30

40

ь , я

50

55

92

хранения кодов режимов функционирования логической части 19. Информация в запоминающую часть 18 34 , j поступает из запоминающей части предыдущей ячейки 3 памяти входной матрицы И. Информация из запоминающей части 34j: ячейки XZjj может быть передана в запоминающую часть последующей ячейки XZ,,. Запоминающие части 34 34; строки ячеек образуют горизонтальную последовательную сдвиговую струк-- туру (сдвиговый регистр), сдвиг в .которой производится под действием синхросигнала записи информации, поступающего с выхода элемента 2И 14. Информация в первую ячейку XZ; горизонтального сдвигового регистра заносится с шины 4 для прямого значения входной переменной Х- при наличии управляющего сигнала - сигнала разрешения записи W1 и внешнего синхронизирующего сигнала С на входе 16. Информация с выхода последней ячейки 3 XZjj (фиг. 1) далее не передается.

С помощью запоминающей части 34; 18 можно установить следующие режи- мы работы соответствующей ей логической части Л4 - 19.

Режим О - установить на выходе Л4)| (на шине Z/) состояние логического нуля. Режим 1 - установить на выходе Л4;; состояни е логической единицы. Режим связи с X; - установить логическую связь между первьш входом логической части Л4,; (шиной Xj 5) и выходом логической части Л4,- (шиной Zj). Режим связи с X; - установить логическую связь между вторым входом логической части Л4;: (шириной Xj 4) и выходом логической часу

ти Л4,. (шиной Z,; ) . I U J

Для кодирования четырех упомянутых режимов достаточно иметь в запоминающей части 34jj два однобитовых запоминающих элемента (два триггера). Логическая часть 19 состоит из комбинационных схем, и предназначена . для реализации режимов, задаваемых запоминающей частью 18.

Ячейка 9 2Y;,j выходной матрицы ИЛИ (фиг. 3) содержит запоминающую часть 34JI5 20 „и логическую часть Л4j 21. Запоминающая часть предназначена для хранения кодов режимов функционирования логической части. Информация в запоминающую часть ЗЧ;/,

поступает из запоминающей части 34

предыдущей ячейки памяти выходной матрицы ИЛИ.. Информация из ,запоми

части 34

Ji

ячейки

)

В запоминающую часть 34

последующей ячейки выходнои матрицы. Запоминающие части 34;, SHj столбца ячеек ZYji . образуют вертикаль- кую последовательную сдвиговую струк туру (сдвиговый регистр). Сдвиг информации производится под действием синхросигнала, поступающего с выхода элемента 2И 14. Информация в первую ячейку вертикального сдвигового регистра заносится с первой столбцовой шины промежуточной переменной Z, при наличии сигнала разрешения записи W2 (управляющего сигнала) и внешнего синхронизирующего сигнала С. Информация с выхода последней ячейки регистра (ZY- для фиг. 1) далее не передается.

С помощью запоминающей части 34 20 можно установить следующие режимы работы соответствующей ей логической

,-,

части ЛЧj 21.

Режим связи О - установить на выходе состояние логического нуля. Режим связи с Z: - установить логическую связь входа логической части ЛЧjц (шиной Zj 17). Для кодирования упомянутых режимов в запоминающей части достаточно иметь один однобитовый запоминающий элемент (один триггер). Логическая часть состоит из комбинационных схем и предназначена для реализации режимов задаваемых запоминающей частью.

Ячейка 3 матрицы И, функциональная схема которой изображена на фиг.4. содержит запоминающую часть из первого 22 и второго 23 двухступенчатых синхронизируемых D-триггеров и логическую часть из комбинационной схемы 2И-ИЛИ 24, вход которой построен по схеме с открытым коллектором. Ячейка 9 матрицы ИЛИ (фиг. 5) включает запоминающую часть - триггер 25 и логическую часть из комбинационной схемы И 26. iI

Настройка запоминающего устройства заключается в занесении в запоминающие части 34;: -34 j ячеек XZ,-j 30

35

40

дом 11 на режим логической .единицы на выходе, то состояние столбцовых шин Zi, j 1, 2, 3 определяется состоянием ячеек верхней строки , j 1, 2, 3 матрицы И. Так, если ячейка XZ настроена на режим 0 (код настройки 00), то на шине Z имеется логический ноль. Зафиксированное состояние столбцовых промежуточных шин матрицы И можно переписать в ячейки 9 первой строки матрицы ИЛИ, т.е. ячейки ZYj, , j v 1, 2, 3. Для этого необходимо подать другой сигнал разрешения записи и внешний синхронизирующий сигнал (при отсутствии сигнала разрешения записи ). Информация со столбцовых шин Zj записывается в запоминаю-

34;, 20 (фиг. 3) первых

3

щие части

ячеек ZYj, каждого столбца ячеек выходной матрицы ИЛИ. Одновременно происходит сдвиг информации БЛИЗ на один 45 разряд вдоль каждого столбца ячеек матрицы ИЛИ. После такта записи в

ячейках ZYj,( , .j 1, 2, 3, хранится информация, зафикбиронанная на тинах Zj, 3 1, 2, 3. Для полной смены ин- 50 формации в матрице ИЛИ необходимо три цикла обновления, на каждом из которых полностью обновляется информация в первой строке матрицы И. ПосZY

JK

ле настройки матрицы ИЛИ окончатель- соответствующих настроечных ко- „о перенастраивается матрица И по

дов. Запись настроечных кодов в матрицы И производится при наличии одного из управляющих сигналов (сигнала разрешения записи). При этом инвходным сигналам на шинах Xj и при , , .

Как уже отмечалось, необходимо выполнить шесть тактов записи в мат-

. . 4-

.

fO

15

, 25

30

35

40

формация, поданная на входы устройства, записывается в запоминающие части 34 (| первых ячеек 3 XZ;, каждой строки. Одновременно происходит сдвиг информации вправо на 1 разряд вдоль каждой строки ячеек матрицы И в каждой горизонтальной сдвиговой структуре. После шести тактов записи настроечная информация в матрице И полностью обновляется.

Принимаем следующее кодирование режимов работы логической части матрицы И. 00 - режим выдачи логического нуля на выход Л4 (на шину Zj 17) режим логической связи шины Х- и Z;, 10 - режим логической связи шины X; и Zj , 11 - режим выдачи логической единицы на выход логической части (на шину Z 17) ЛЧ-: ячей20 ки XZ;j .

Если нижнюю строку ячеек матрицы настроить коИ XZjj (j 1, 2, 3)

дом 11 на режим логической .единицы на выходе, то состояние столбцовых шин Zi, j 1, 2, 3 определяется состоянием ячеек верхней строки , j 1, 2, 3 матрицы И. Так, если ячейка XZ настроена на режим 0 (код настройки 00), то на шине Z имеется логический ноль. Зафиксированное состояние столбцовых промежуточных шин матрицы И можно переписать в ячейки 9 первой строки матрицы ИЛИ, т.е. ячейки ZYj, , j v 1, 2, 3. Для этого необходимо подать другой сигнал разрешения записи и внешний синхронизирующий сигнал (при отсутствии сигнала разрешения записи ). Информация со столбцовых шин Zj записывается в запоминаю-

34;, 20 (фиг. 3) первых

3

щие части

ячеек ZYj, каждого столбца ячеек выходной матрицы ИЛИ. Одновременно происходит сдвиг информации БЛИЗ на один 45 разряд вдоль каждого столбца ячеек матрицы ИЛИ. После такта записи в

ячейках ZYj,( , .j 1, 2, 3, хранится информация, зафикбиронанная на тинах Zj, 3 1, 2, 3. Для полной смены ин- 50 формации в матрице ИЛИ необходимо три цикла обновления, на каждом из которых полностью обновляется информация в первой строке матрицы И. Посвходным сигналам на шинах Xj и при , , .

Как уже отмечалось, необходимо выполнить шесть тактов записи в мат-

512

рнцу и, так как каждая ячейка 3 матК рицы И содержит в своей запоминающей части два однобитовых запоминающих элемента. В целом настройка запоминающего устройства (фиг. 1) производится за 27 тактов записи (тактов сдвига информации в последовательных регистрах) : 27(6+1)+(6+1)+(6+1)+6. Для программирования запоминающего устройства п m входами, п выходами и р разрядными шинами время настрой

ки (программирования) Т„„ выражается в количестве тактов сдвига формулой Т (2p+1/n+2p 2p/n+1)+n и не зависит от числа входов т.

Устройство функционирует следующим образом.

Логический уровень сигнала Z; на разрядной шине 17 первой матрицы И определяется режимами работы подключенных к ней своими выходами ячеек XZj и задается формулой Z:,-.А Х-,

причем , если 0 , если 34;;

10 , , если Х| 1, если 34;; 11.

Например, если 34,( 00 и 34 10,

то Z, Х Х ,

0 и 3422

если 34,2

, если 34, 1 1 то Z 1

11,

и

1 2

ТО Zj 0. 342, 01,

Таким образом, с помощью матрицы И (матрицы конъюнкций) можно сформировать на разрядной шине 17 значение произвольного темпа входных переменных Xj и констант О и 1. Логический уровень на горизонтальной выходной шине Y определяется режимами работы подключенных к ней своими выходами ячеек ZYjK матрицы ИЛИ и задается

-JK формулой Y.

если 34

7 7

i

k , V Z, причем .2, J

j 1; если 34- О, Z; 0. Например, если 34,, 1, 34 1, 34,; 1, то Y,Z,+Z2+Z3; если 34, , , то если 34,, О, , , то .

В итоге программируемое запоминающее устройство позволяет получить систему булевых функций, представленных в дизъюнктивной нормальной форме.

Формула изобретения

1, Лрограммируемое запоминающее устройство, содержащее первую и вторую матрицу ячеек памяти, блок управления записью информации, нагрузочные элементы первой и второй груп инверторы, входы которых подключены

5

0

к адресН1,1м шинам первой матрицы ячеек памяти, первым входом соответствующих ячеек памяти и являются адресными входами устройства, выходы инверторов подключены к другим адресным шинам матрицы ячеек памяти и вторым входам соответствующих ячеек памяти, первые выходы ячеек памяти первой матрицы подключены к первым выводам соответствующих на- грузочных элементов первой группы и первым входам ячеек памяти второй матрицы, первые выходы ячеек памяти второй матрицы подключены к первым выводам соответствующих нагрузочных элементов второй группы иявляются выходами устройства,входы блока управления записью информации являются управляющими входами устройства,о т л и- чающееся тем, что, с целью расширения области применения за счет возможности перезаписи информации, вторые выводы нагрузочньгх эле-у ментов первой и второй групп подключены соответственно к шине питания и шине нулевого потенциала, в каждой строке первой матрицы третий вход каждой ячейки памяти, кроме первой, соединен с вторым выходом предьщущей ячейки памяти, третий вход первой ячейки памяти подключен к одной из адресных шин, в каждом столбце второй матрицы второй вход каждой ячейки памяти, кроме первой, подключен 5 к второму выходу предьщущей ячейки памяти, второй вход первой ячейки памяти соединен с выходами соответствующих, ячеек памяти первой матрицы, третьи входы ячеек первой и второй матриц соединены соответственно с первым и вторым выходами блока управления записью информации.

5

I

0

0

2. Устройство по п. 1 отличающееся тем, что каждая ячейка памяти первой матрицы состоит из первого и второго D-триггеров и элемента 2И-ИЛИ, выход которого является третьим выходом ячейки памяти, первый и второй входы элемента 2И-Р1ПИ являются первым и вторым входами ячейки памяти, третий и четвертый входы элемента 2И-ИЛИ соединены с выходами D-триггера, первые входы которых являются третьим входом ячейки памяти, вторые входы D- триггеров являются вторым выходом ячер ки памяти.

71282219 . 8

3. Устройство по п. 1, о т л и - ходом ячейки памяти, первый вход

чающееся тем, что каждая ячейка памяти второй матрицы состоит из В -триггера и элемента И, выход D-триггера подключен к первому входу элемента И и является первым выD-триггера является вторым входом ячейки памяти, второй вход D-триггера является третьим выходом ячей- ки памяти, выход элемента И является вторым выходом устройства.

ffo,4

1 , 15 Ь

(IKft.f

tf}ui.2

If/I1«

Га1

{i

I

//

jfi

щ

Составитель Л.Амусьева Редактор Е.Папп Техред В.Кадар Корректор М.Шароши

Заказ 7276/52 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Ра лпская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Устройство для считывания и обработки изображений | 1988 |

|

SU1513486A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU649038A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ИНФОРМАЦИИ | 1971 |

|

SU424141A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

| Ассоциативная ячейка памяти | 1989 |

|

SU1635216A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах, устройствах вычислительной техники и автоматики, контроллерах и устройствах управления. Целью изобретения является расширение области применения, за счет возможности перезаписи| информации. Поставленная цель достигается введением внутренних связей между ячейками памяти либо по строкам, либо по столбцам. Это позволяет осуществлять безадресную некоординатную настройку ячеек памяти путем последовательной передачи информации от одной ячейки памяти к другой. При этом время настройки сокращается и не требуется доступ к вертикальным тинам выборки элементов памяти. 2 з.п. ф-лы. 5 ил. (Л to 00 ю ND

| Патент США №4177452, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Патент США № 4293783, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1987-01-07—Публикация

1985-01-29—Подача