1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устрействах телемеханики для анализа признаке сообщений, а также в устройствах формирсжания последсеательности операций, управляемых по программе с ЦВМ.

Известны устройства для кодирсшария числоимпульснсго кода, содержащие счетчик, выходы которого соединены со входами дешифратора и схемы сравнения, схему временной задержки а регистр, входы которых соединены с шинами кода программы, а выходы регистра соединены со входами схемы сравнения, триггеры управления, единичный вход которого соединен с одним из выход ж схемы сброса, другой выход которой соединен с установочным входом счетчика, нулевой выход триггера управления соединен со входом схемы сброса, схему ИЛИ , схему совпадения и инвертер.

Однако наличие в таком устройстве задающей двухтактной схемы записи информации в счетчик его быстродейс-рвие.

Целью изобретения является повышение быстродействия устройства декодирования чиспримпульсного кода.

Это достигается тем, что в нем нулевой вход триггера управления и вход считывания схемы сравнения соединены через схему временной задержки с единичным выходом триггера управления, соединенным с первым входом схемы ссжпадения, входная шина устройства соединена с дополнительным входом схемы сброса и через инвертор - со вторым входом схемы совпадения, выход которой через схему ИЛИ соединен со входом счетчика, выход переполнения последнего соединен С другим входом схемы ИЛИ, выход схемы сравнения соединен со входс считьюания дeшифpaтqpa.

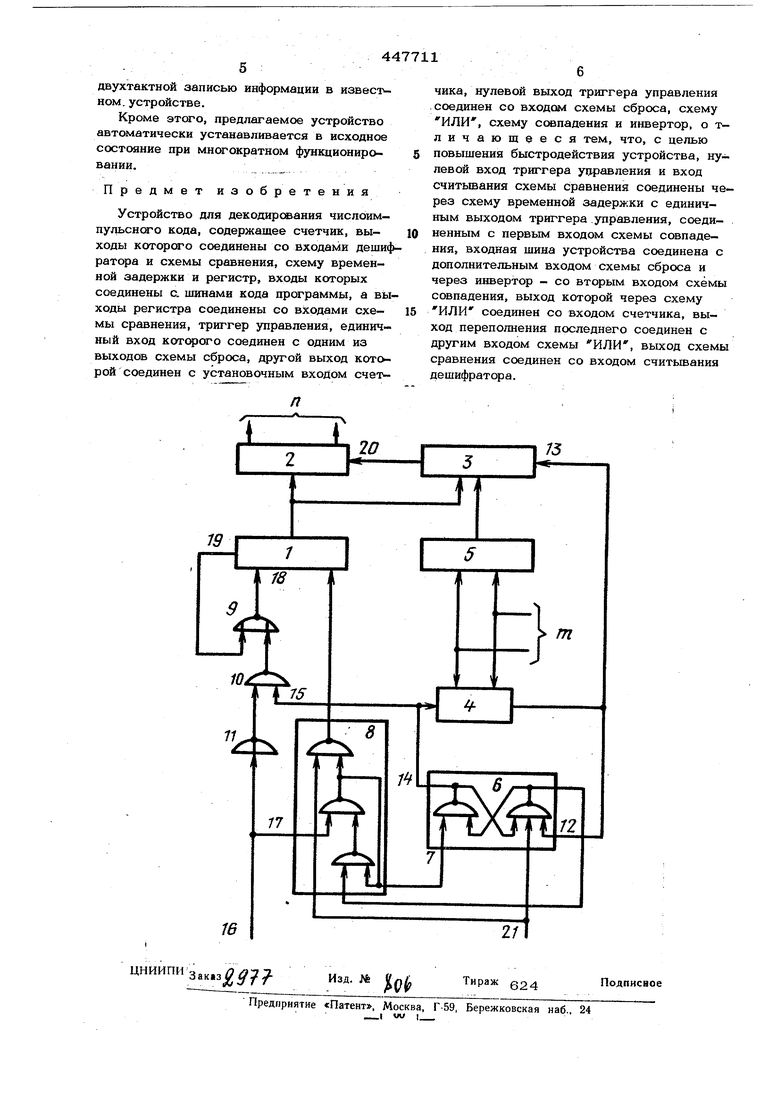

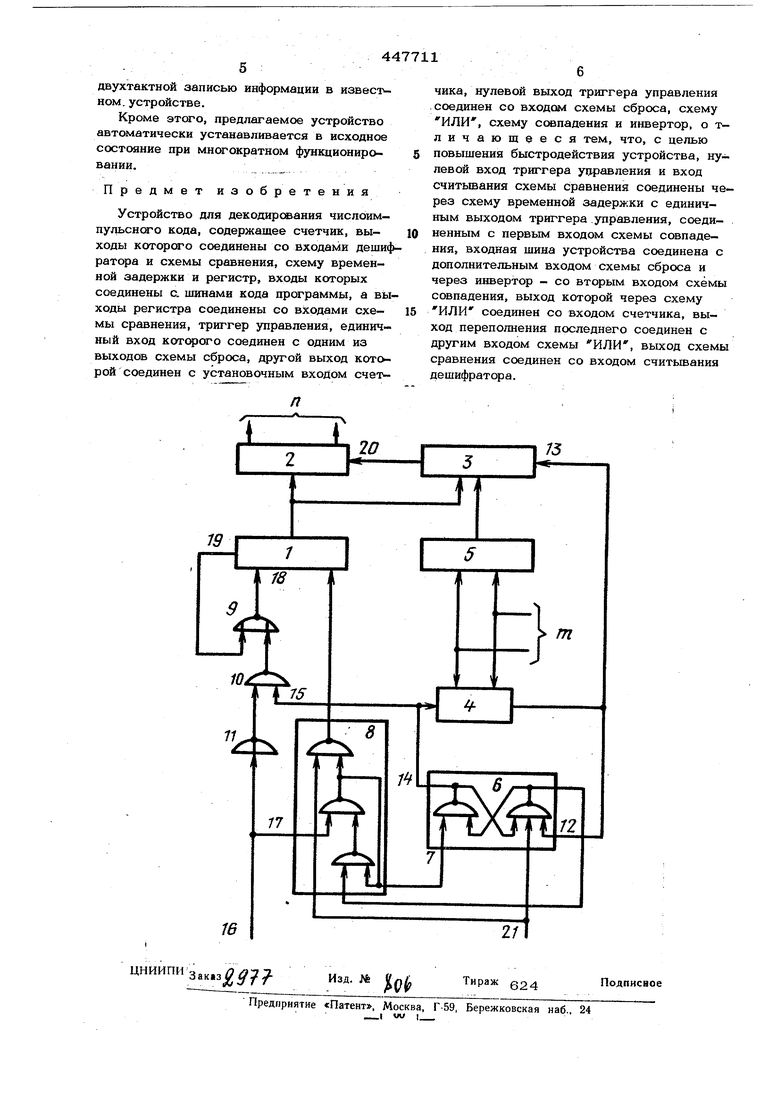

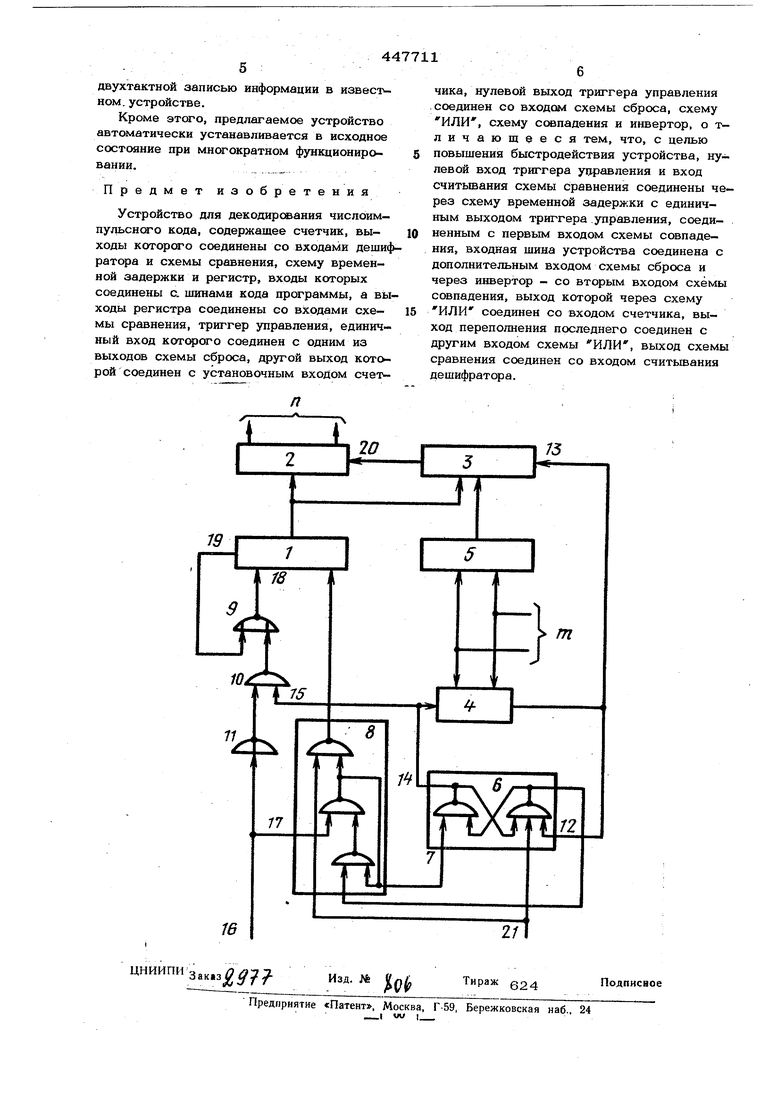

На чертеже изображена функциональная схема предлагаемого устройства.

Устрсйство содержит счетчик 1, выхо ды которого соединены со входами дешифратора 2 и схемы сравнения 3, схему временной задержки 4 и регистр 5, входы которых соединены с Щ -шинами кода программы, а выходы регистра 5 соединены со входами схемы сравнения 3, триггер управления 6, единичный вход 7 которого соединен с одним из выходов схемы сброса 8, другой выход которой соединен с установочным входом счетчика 1, нулевой выход триггера управления 6 соединен с другим входом схемы сброса 8, схему ИЛИ 9, схему совпадения 10 и инвертор 11. При этом нулевой вход 12 триггера управления 6 и вход 13 считывания схемы сравнения 3 соединены через схему временной задержки 4 с единичным выходом 14 триггера управления 6, соединенным с первым входом 15 схемы совпадения 10, входная шина 16 устройства соединена с дополнительным входом 17схемы сброса 8 и через инвертор 11 - со вторым входом схемы совпадения 1О, выход которой через схему ИЛИ 9 соединен со входом 18 с: четчика 1, выход переполнения 19 последнего соединен с входом схемы ИЛИ 9, выход схемы сравнения 3 соединен со входом 20 считывания дешифратора 2. Устройство содержит также шину 21 сброса и ft -шин выходных сигналов устройства. Устройство работает следующим образо В исходное состояние схема устанавливается импульсом низкого потенциала, пос тудаюшего по шине 21 сброса. При этом на выходе инвертора 11 высокий уровень потенциала, на входных шинах fn -разрядного кода программы и на входной шине 16 -устройства - .низкие уровни потенциалов. По окончании импульса сброса на выходах счетчика 1, на ft-выходах дешифратора 2, на выходе 14 триггера 6, йа входе 12 триггера 6 и на входе 13 схемы сравнения 3, на выходе схемы сброса 8 и на выходе схемы совпадения 10 устанав ливается низкий потенциал, а на выходе схемы ИЛИ 9 и выходе 19 счетчика 1 высокий потенциал. .. Перед поступлением сигналов по входной шине 16 на шины fft -разрядного кода программы поступает код, соответствую ший чиспоимпульсному входному коду, при этом соответственно настраивается и схема временной задержки 4. В момент поступления первого входного импульса по егь переднему фронту с одного выхода схемы сброса подается дополнитель ный сигнал на установку в исходное COCTOS ние счетчика 1,а с долопнительного выхода на вход 7 триггера 6 - низкий потенцяал,о которого срабатывает триггер 6, на входе которого устанавливается высокий потенциал, а на противоположном - низкий потенциал. При этом потенциалом с выхода 14 триггера 3 запускается схема временной задержки 4. По заднему фронту входного сигнала схема сброса 8 заканчивает формирование сигнала Сброс на установку счетчика 1 в исходное состояние и удерживается в таком состоянии на все время работы схемы : временной; задержки 4 низким уровнем с нулевого плеча триггера 6. При этом че- рез инвертор 11, схему совпадения 10 и схему ИЛИ 9 на вход счетчика 1 постуг пает передний фронт первого импульса числоимпульсного кода. В последующие моменты поступления очередных входных сигналов по шине 16 по их переднему фронту схема сброса 8 и триггер 6 не изменяют своего состояния, по заднему фронту осуществляется запись в счетчик 1 всего числоимпульсного кода. При поступлении ожидаемого числоимпульсного кода и сравнении с заданным по программе, который хранится в регис-рре памяти 5, похиотовится к работе схема сравнения 3. В момент срабатывания схемы времен ной задерлски 4 низким потенциалом с ее выхода триггер 6 устанавливается по входу 12 в исходное состояние и проводится опрос по входу 13 схемы сравнения 3, с выхода которой вырабатывается сигнал считывания по входу 2О дещифратора 2. При этом на соответствующем одном из ft -выходов появляется сигнал, соответст- вуюший входному числоимпульсному коду, а схема совпадения Ю гвходу 15 и схе-)ма ИЛИ 9 будут установлены в исходное-. состояние. При последующих мнсяг-ократных анализах соответствующих числоимпульсных кодов схема устройства сбрасывается автоматически передним фронтом входного сигнала, поступающего по шине 16. В случае поступления искаженного числоимпульсного кода не срабатывает схема сравнения 3, а по опросному сигналу на входе 13 {со схемы временной задержки 4) не вырабатывается сигнал считывания по входу 20 дешифратора 2 и, соответственно, на М- -выходах устройства не появляется выходной сигнал. При переполнении счетчика 1 с выхода 19 низким потенциалом отключается схема ИЛИ 9, запрещая поступление входных сигнале по щине 16. Таким образом, предлагаемое устройство, обеспечивающее запись информации в счетчик по заднему фронту входного сигнала, обладает повышенным быстродействием по счетному входу по с авнён1ию с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Устройство для выделения первого и последнего импульсов в серии | 1989 |

|

SU1647866A2 |

| Формирователь пачек импульсов | 1980 |

|

SU961117A1 |

| ЦИКЛИЧЕСКИЙ ИНДИКАТОР ОТКАЗОВ | 1969 |

|

SU243683A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1970 |

|

SU273688A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Устройство для считывания графической информации | 1990 |

|

SU1728872A1 |

| Селектор импульсов по длительности | 1979 |

|

SU817998A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

Авторы

Даты

1974-10-25—Публикация

1973-05-16—Подача