Изобретение относится к области вычислительной техники и предназначено для подсчета одноименных цифр в двоичных кодах.

Известно устройство для параллельного счета количества единиц (нулей), содержащее входной и выходной регистры и логическую схему, выполненную на комбинационных сумматорах.

Недостатками такого устройства, обусловленными низкой степенью регулярности связей, являются:

-большое количество пересечений связей между собой;

-большая длина линий связи между сумматорами логической схемы;

-необходимость применения конструктивно относительно сложных ячеек сумматоров.

Вследствие этого устройство в целом усложняется; кроме того, при реализации устройства методами микроэлектроники уменьшается технологичность его изготовления.

Целью изобретения является упрощение устройства.

Указанная цель достигается созданием регулярной структуры связей между сумматора мн логической схемы, для чего входы каждого X) сумматора k-n группы соединены с выхо( переноса 2г-го и (2t-1)-го сумматоров группы и с выходом суммы (i-1)-го 1 k-K группы; выходы 2t-ro и (2t-1)го разрядов входного регистра соединены со входами г-го сумматора первой группы.

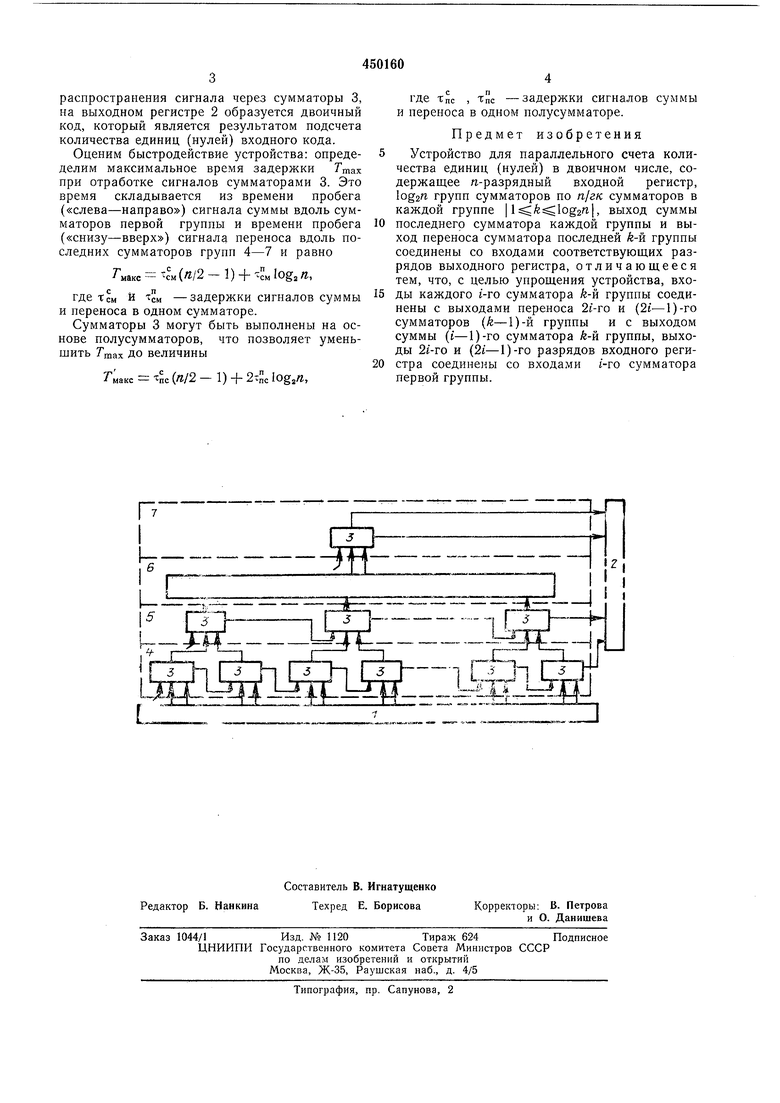

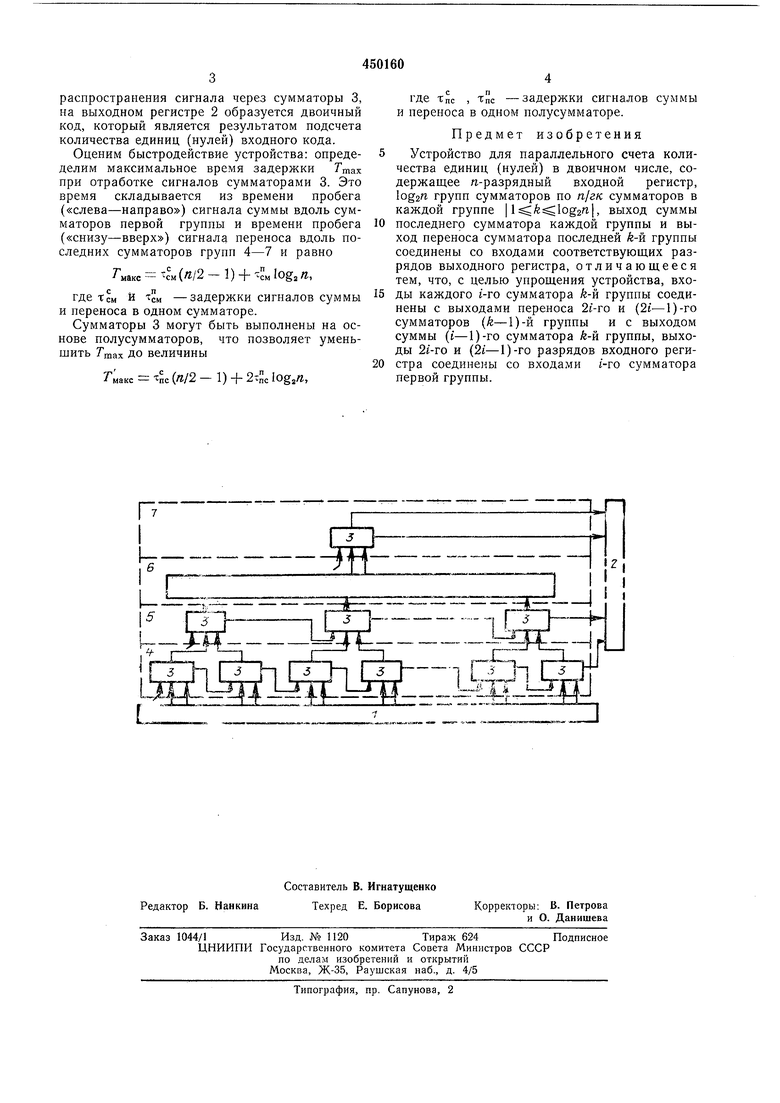

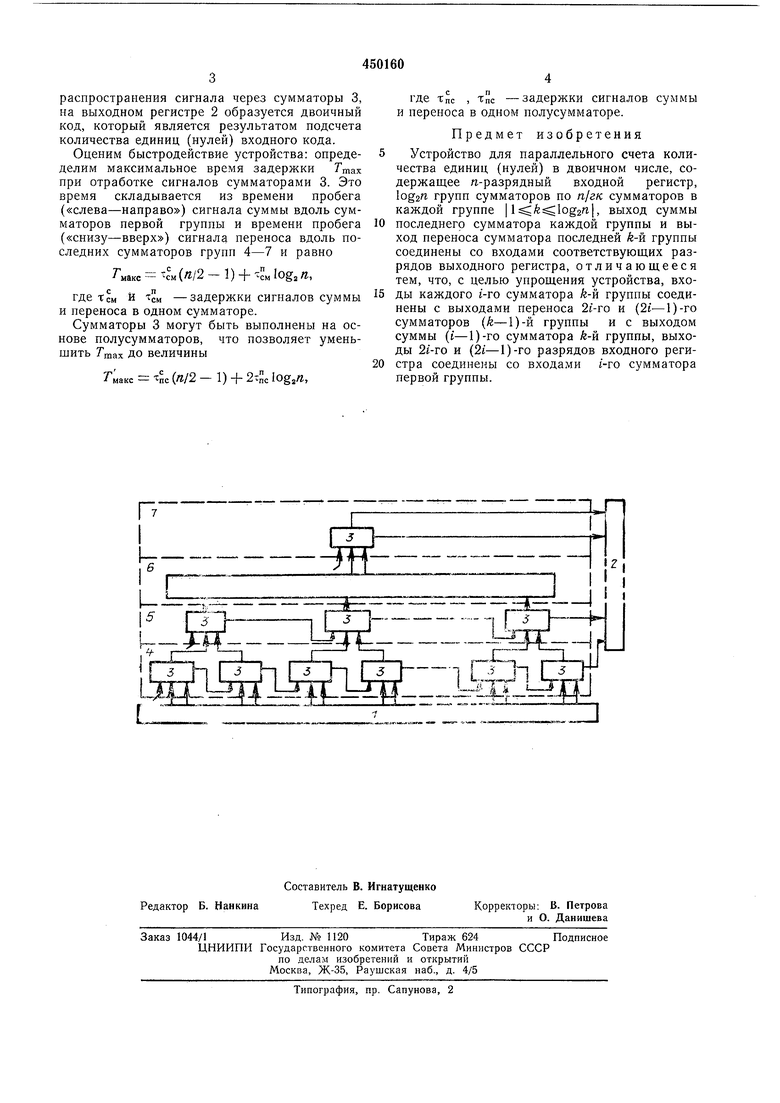

Схема устройства изображена на чертеже.

Устройство содержит п-разрядный входной регистр 1, выходной регистр 2, сумматоры 3, объединенные в группы 4-7.

Число групп равно Iog2«., число сумматоров в каждой группе равно

n/2k, где k-, 2,..., logs и.

Устройство имеет следующую структуру связей.

Выходы 2i-ro и (21-1)-го разрядов входного регистра соединены со входами t-ro сумматора первой группы. В последующих группах входы каждого г-го сумматора k-u группы соединены с выходами переноса 2t-ro и (2/-1)-го сумматоров (k-1)-й группы и с выходом суммы (г-1)-го сумматора й-й группы. Выход суммы последнего сумматора каждой грунпы и выход переноса сумматора последней группы соединены со входами соответствующих разрядов (й+1)-разрядного выходного регистра. Третий вход первого сумматора каждой группы свободен от связи. Он будет задействован в том случае, если число выходов переноса с сумматоров предыдущей группы является нечетным.

После установки очередного кода в регистре 1 через некоторое время, равное времени

распространения сигнала через сумматоры 3, на выходном регистре 2 образуется двоичный код, который является результатом подсчета количества единиц (нулей) входного кода.

Оцепим быстродействие устройства: опредеделим максимальное время задержки Гтах при отработке сигналов сумматорами 3. Это время складывается из времени пробега («слева-направо) сигнала суммы вдоль сумматоров первой группы и времени пробега («снизу-вверх) сигнала переноса вдоль последних сумматоров групп 4-7 и равно

Тмакс -см (/г/2 - 1) -f -см lOgj «,

где Тем и -задержки сигналов суммы и переноса в одном сумматоре.

Сумматоры 3 могут быть выполнены на основе полусумматоров, что позволяет уменьшить Гшах до величины

Тыакс пс (п/2 - 1) + 2пс Iogj/г,

где Тпс , Тпс -задержки сигналов суммы и переноса в одном полусумматоре.

Предмет изобретения

Устройство для параллельного счета количества единиц (нулей) в двоичном числе, содержащее д-разрядный входной регистр, Iog2n групп сумматоров по п/гк сумматоров в каждой группе | I: fe: log2i|, выход суммы последнего сумматора каждой группы и выход переноса сумматора последней й-й группы соединены со входами соответствующих разрядов выходного регистра, отличающееся тем, что, с целью упрощения устройства, входы каждого t-ro сумматора k-и группы соединены с выходами переноса 2f-ro и (2i-1)-го сумматоров (k-1)-й группы и с выходом суммы (i-1)-го сумматора й-й группы, выходы 2г-го и (21-1)-го разрядов входного регистра соединены со входами f-ro сумматора первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля правильности приема информации в кодах Бергера | 1981 |

|

SU964626A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Устройство для контроля двоичной информации в кодах Бергера | 1982 |

|

SU1068942A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для подсчета количества единиц в @ -разрядном двоичном коде | 1990 |

|

SU1783617A1 |

| Сумматор двоичных чисел | 1974 |

|

SU506852A1 |

| Устройство для параллельного счета количества единиц (нулей) в двоичном числе | 1979 |

|

SU781811A2 |

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

Авторы

Даты

1974-11-15—Публикация

1972-09-25—Подача