Изобретение относится к автоматике и вычислительной технике и может быть использовано для свертки чисел по модулю.

Цель изобретения - сокращение аппаратурных затрат.

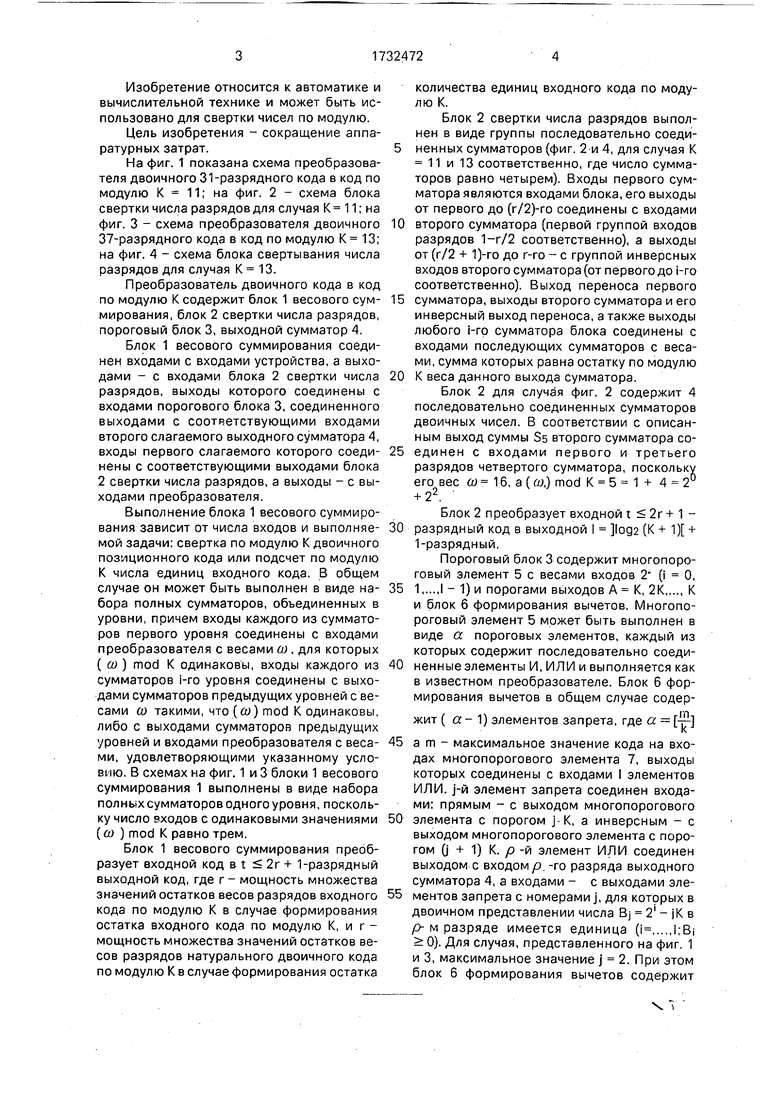

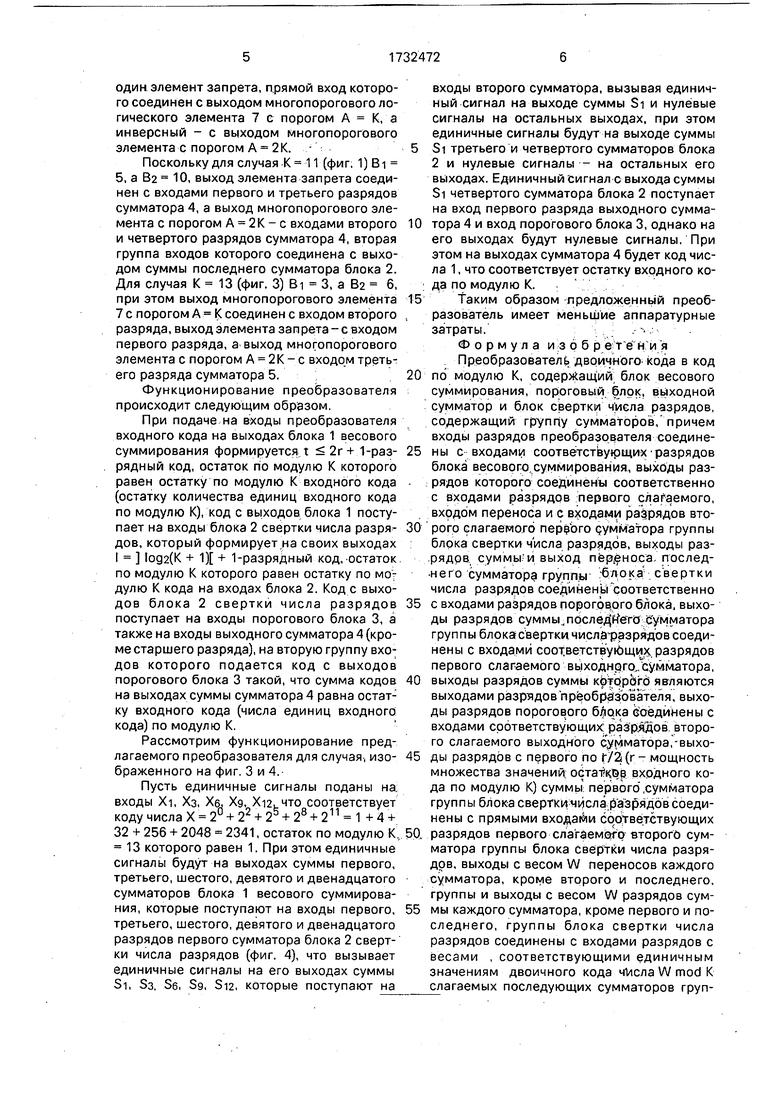

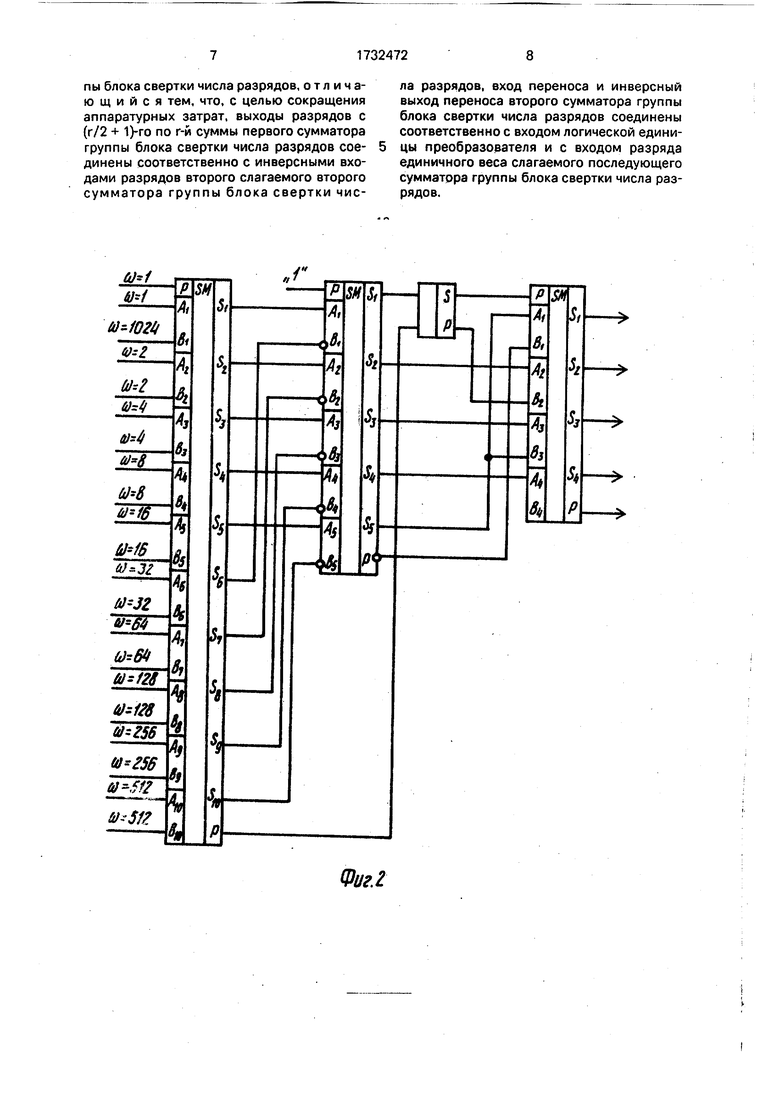

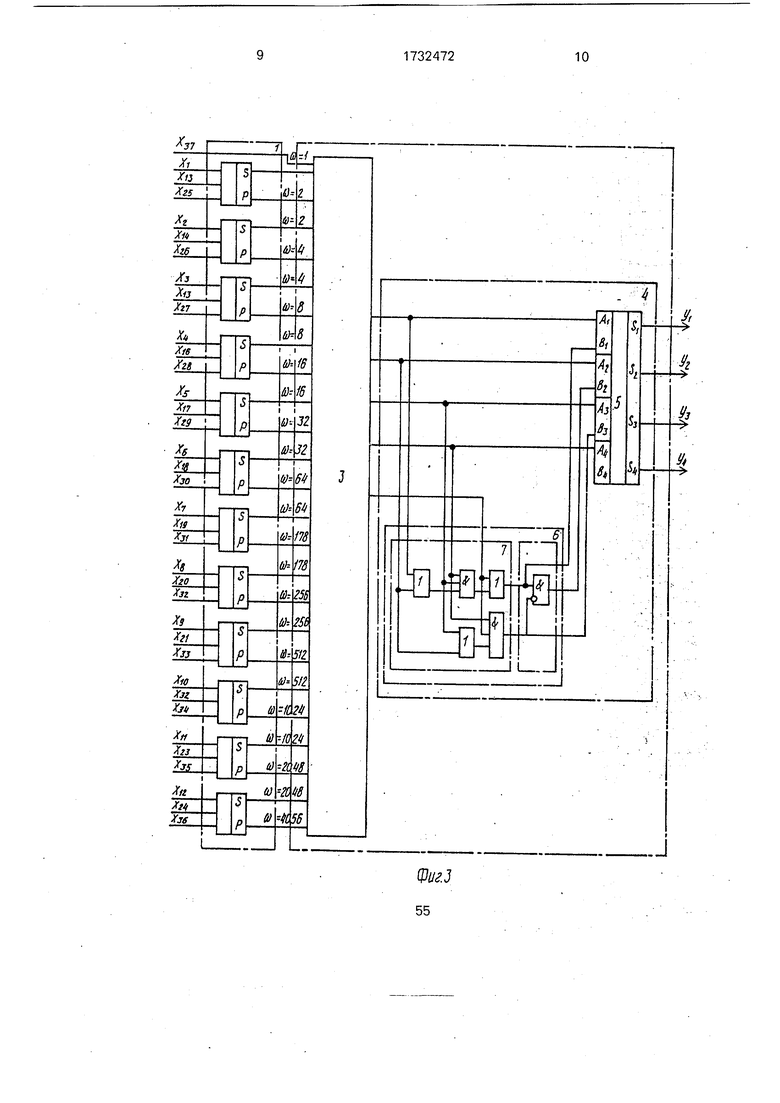

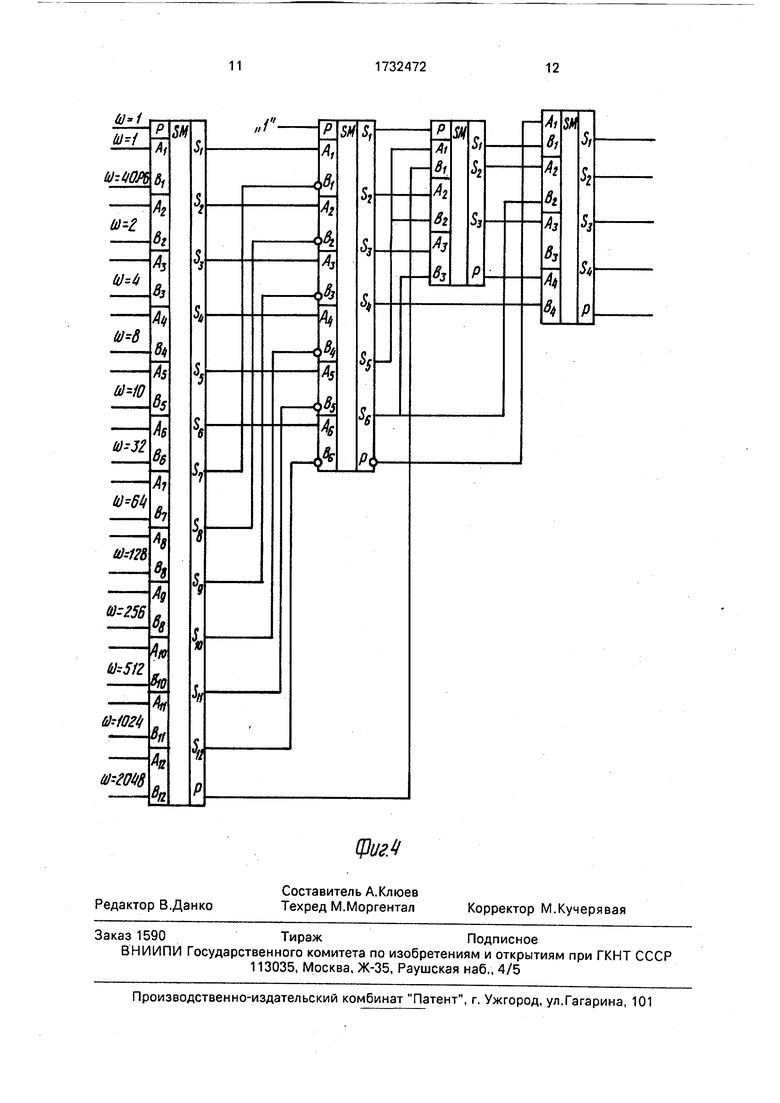

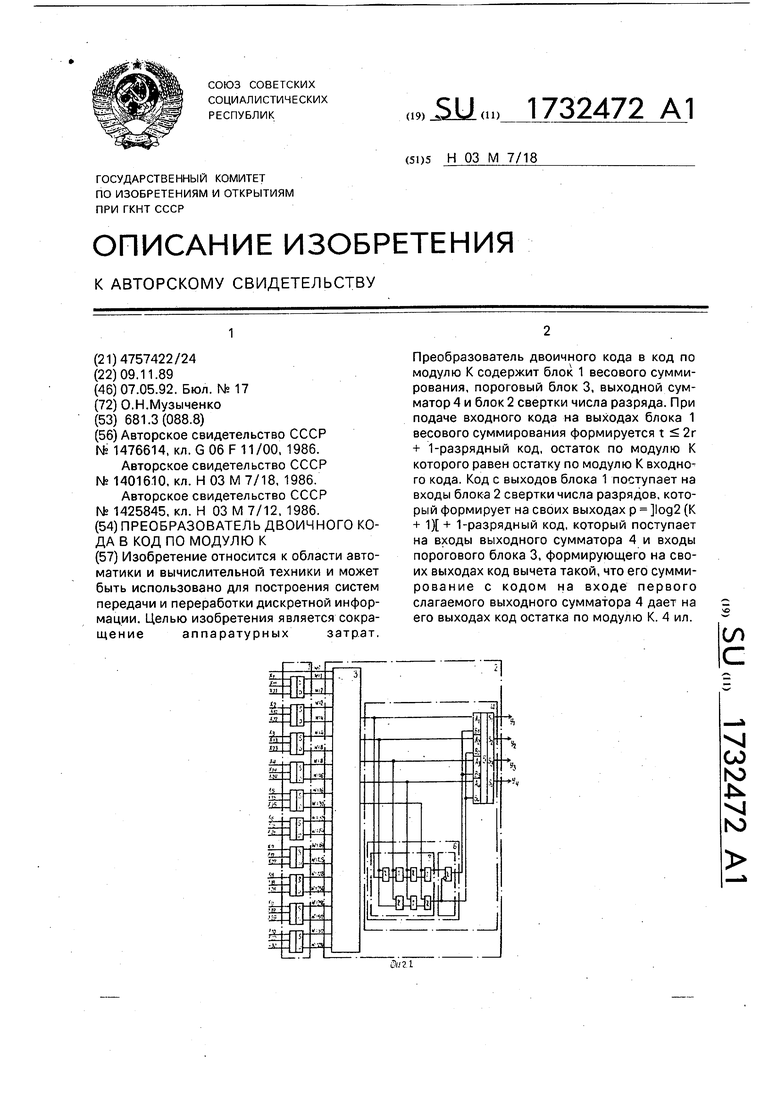

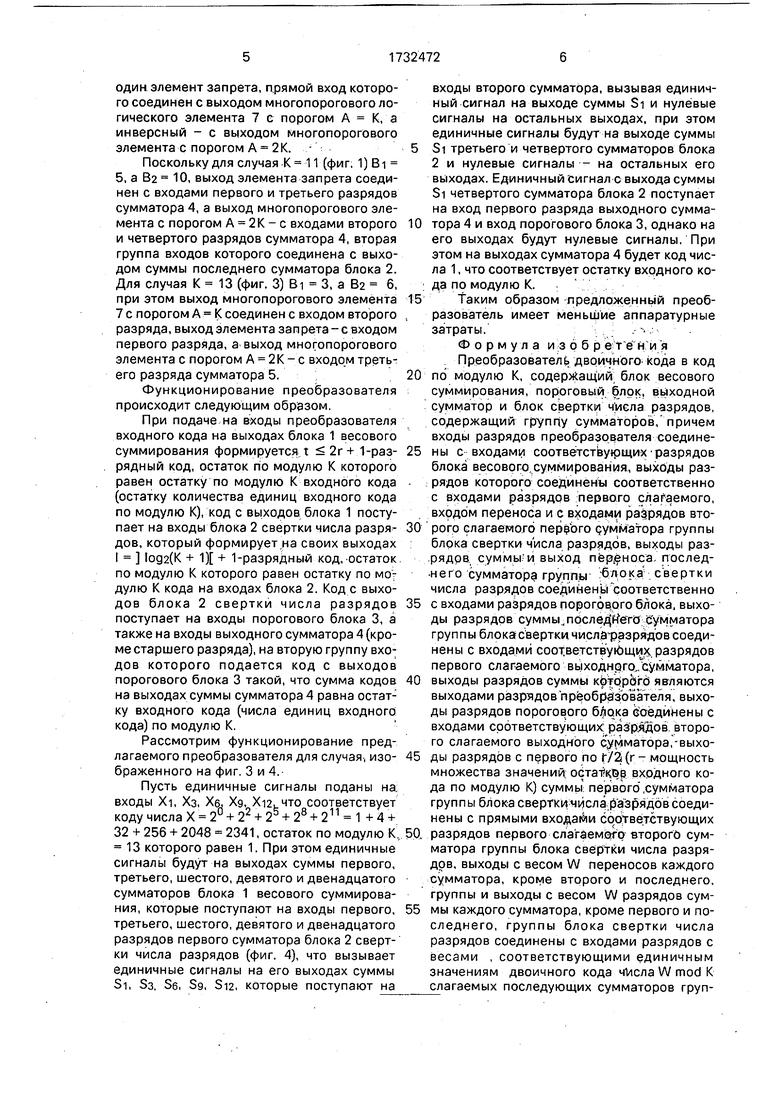

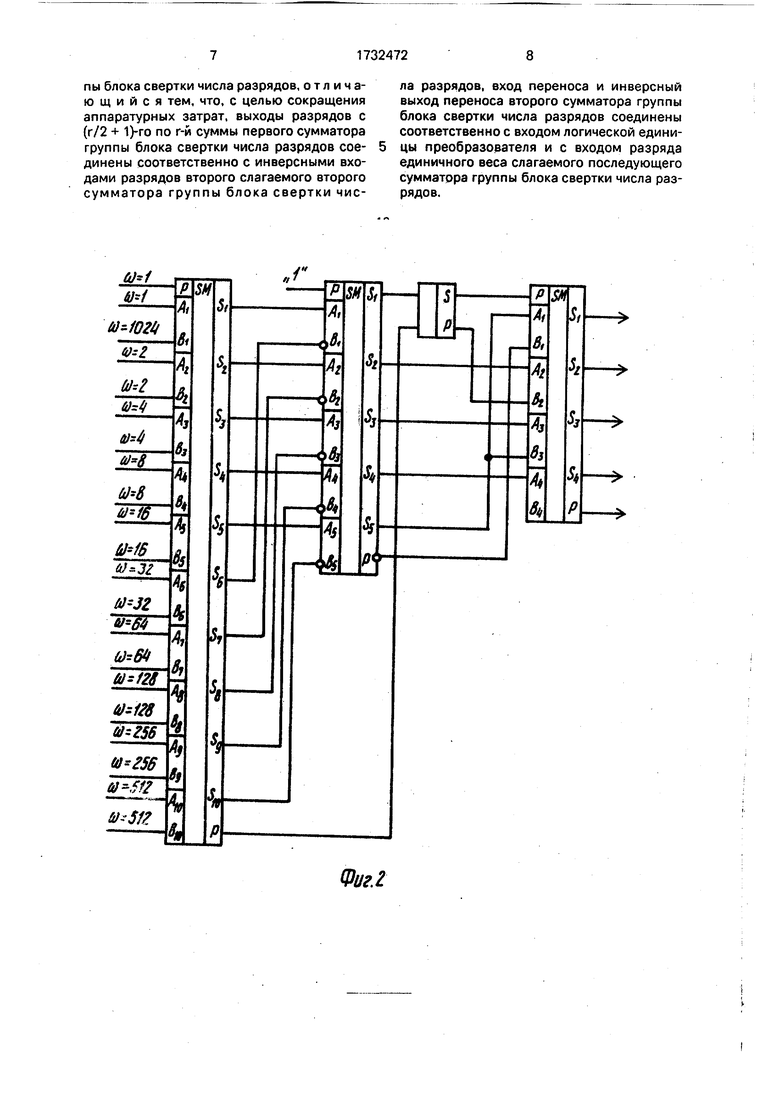

На фиг. 1 показана схема преобразователя двоичного 31-разрядного кода в код по модулю К 11; на фиг. 2 - схема блока свертки числа разрядов для случая К 11; на фиг. 3 - схема преобразователя двоичного 37-разрядного кода в код по модулю К 13; на фиг. 4 - схема блока свертывания числа разрядов для случая К 13.

Преобразователь двоичного кода в код по модулю К содержит блок 1 весового суммирования, блок 2 свертки числа разрядов, пороговый блок 3, выходной сумматор 4.

Блок 1 весового суммирования соединен входами с входами устройства, а выходами - с входами блока 2 свертки числа разрядов, выходы которого соединены с входами порогового блока 3, соединенного выходами с соответствующими входами второго слагаемого выходного сумматора 4, входы первого слагаемого которого соединены с соответствующими выходами блока 2 свертки числа разрядов, а выходы - с выходами преобразователя.

Выполнение блока 1 весового суммирования зависит от числа входов и выполняемой задачи: свертка по модулю К двоичного позиционного кода или подсчет по модулю К числа единиц входного кода. В общем случае он может быть выполнен в виде набора полных сумматоров, объединенных в уровни, причем входы каждого из сумматоров первого уровня соединены с входами преобразователя с весами со, для которых ( ft)) mod К одинаковы, входы каждого из сумматоров i-ro уровня соединены с выходами сумматоров предыдущих уровней с весами со такими, что (со) mod К одинаковы, либо с выходами сумматоров предыдущих уровней и входами преобразователя с весами, удовлетворяющими указанному условию. В схемах на фиг. 1 и 3 блоки 1 весового суммирования 1 выполнены в виде набора полных сумматоров одного у ровня, поскольку число входов с одинаковыми значениями (а) ) mod К равно трем.

Блок 1 весового суммирования преобразует входной код в t 2r + 1-разрядный выходной код, где г - мощность множества значений остатков весов разрядов входного кода по модулю К в случае формирования остатка входного кода по модулю К, и г - мощность множества значений остатков весов разрядов натурального двоичного кода по модулю К в случае формирования остатка

количества единиц входного кода по модулю К.

Блок 2 свертки числа разрядов выполнен в виде группы последовательно соединенных сумматоров (фиг. 2 и 4, для случая К 11 и 13 соответственно, где число сумматоров равно четырем). Входы первого сумматора являются входами блока, его выходы от первого до (г/2)-го соединены с входами

второго сумматора (первой группой входов разрядов 1-г/2 соответственно), а выходы от (г/2 + 1)-го до г-го - с группой инверсных входов второго сумматора (от первого до i-ro соответственно). Выход переноса первого

сумматора, выходы второго сумматора и его инверсный выход переноса, а также выходы любого i-ro сумматора блока соединены с входами последующих сумматоров с весами, сумма которых равна остатку по модулю

К веса данного выхода сумматора.

Блок 2 для случая фиг. 2 содержит 4 последовательно соединенных сумматоров двоичных чисел. В соответствии с описанным выход суммы Ss второго сумматора соединен с входами первого и третьего разрядов четвертого сумматора, поскольку его вес со 16, а (ад) mod K 4 2° + 22.

Блок 2 преобразует входной t 2г + 1 разрядный код в выходной I loga (К + 1) + 1-разрядный.

Пороговый блок 3 содержит многопороговый элемент 5 с весами входов 2 (i О,

11 - 1) и порогами выходов А К, 2К,..., К

и блок б формирования вычетов, Многопороговый элемент 5 может быть выполнен в виде а. пороговых элементов, каждый из которых содержит последовательно соединенные элементы И, ИЛИ и выполняется как в известном преобразователе. Блок 6 формирования вычетов в общем случае содержит ( а - 1) элементов запрета, где а -Ј

к

a m - максимальное значение кода на входах многопорогового элемента 7, выходы которых соединены с входами I элементов ИЛИ. j-й элемент запрета соединен входами: прямым - с выходом многопорогового

элемента с порогом j-К, а инверсным - с выходом многопорогового элемента с порогом (j + 1) К. р -и элемент ИЛИ соединен выходом с входом р -го разряда выходного сумматора 4, а входами - с выходами элементов запрета с номерами j, для которых в двоичном представлении числа Bj 2 - jK в

р- м разряде имеется единица (,

0). Для случая, представленного на фиг. 1 и 3, максимальное значение j 2. При этом блок 6 формирования вычетов содержит

один элемент запрета, прямой вход которого соединен с выходом многопорогового логического элемента 7 с порогом А К, а инверсный - с выходом многопорогового элемента с порогом А 2К.

Поскольку для случая К 11 (фиг, 1) Вт 5, а 62 10, выход элемента запрета соединен с входами первого и третьего разрядов сумматора 4, а выход многопорогового элемента с порогом А 2К - с входами второго и четвертого разрядов сумматора 4, вторая группа входов которого соединена с выходом суммы последнего сумматора блока 2. Для случая К 13 (фиг. 3) Вт 3, а Ва 6, при этом выход многопорогового элемента 7 с порогом А К соединен с входом второго разряда, выход элемента зап рета - с входом первого разряда, а выход многопорогового элемента с порогом А 2К - с входом третьего разряда сумматора 5

Функционирование преобразователя происходит следующим образом

При подаче на входы преобразователя входного кода на выходах блока 1 весового суммирования формируется t 2г + 1-разрядный код, остаток по модулю К которого равен остатку по модулю К входного кода (остатку количества единиц входного кода по модулю К), код с выходов блока 1 поступает на входы блока 2 свертки числа разрядов, который формирует на своих выходах I log2(K + 1) + 1-разрядный код, остаток по модулю К которого равен остатку по модулю К кода на входах блока 2 Код с выходов блока 2 свертки числа разрядов поступает на входы порогового блока 3, а также на входы выходного сумматора 4 (кроме старшего разряда), на вторую группу входов которого подается код с выходов порогового блока 3 такой, что сумма кодов на выходах суммы сумматора 4 равна остатку входного кода (числа единиц входного кода) по модулю К

Рассмотрим функционирование предлагаемого преобразователя для случая, изображенного на фиг 3 и 4

Пусть единичные сигналы поданы на входы Xi, Хз, Хб, Xg, Xi2. что соответствует коду числа Х 2° + 22 +25 +28 +211 1 + 4 + 32 + 256 + 2048 2341, остаток по модулю К 13 которого равен 1. При этом единичные сигналы будут на выходах суммы первого, третьего, шестого, девятого и двенадцатого сумматоров блока 1 весового суммирования, которые поступают на входы первого, третьего, шестого, девятого и двенадцатого разрядов первого сумматора блока 2 свертки числа разрядов (фиг. 4), что вызывает единичные сигналы на его выходах суммы Si, 83 Se, Sg, 812, которые поступают на

входы второго сумматора, вызывая единичный сигнал на выходе суммы Si и нулевые сигналы на остальных выходах, при этом единичные сигналы будут на выходе суммы

Si третьего и четвертого сумматоров блока 2 и нулевые сигналы - на остальных его выходах. Единичный сигнал с выхода суммы Si четвертого сумматора блока 2 поступает на вход первого разряда выходного сумма0 тора 4 и вход порогового блока 3, однако на его выходах будут нулевые сигналы. При этом на выходах сумматора 4 будет код числа 1, что соответствует остатку входного кода по модулю К.

5 Таким образом предложенный преобразователь имеет меньшие аппаратурные затраты

Формула изобретения Преобразователь двоичного кода в код

0 по модулю К, содержащий блок весового суммирования, пороговый блок, выходной сумматор и блок свертки числа разрядов содержащий группу сумматоров, причем входы разрядов преобразователя соедине5 ны с входами соответствующих разрядов блока весового суммирования, выходы разрядов которого соединены соответственно с входами разрядов первого слагаемого, входом переноса и с входами разрядов вто0 рого слагаемого первого сумматора группы блока свертки числа разрядов, выходы раз- рядрв суммы и выход переноса последнего сумматора группы блока свертки числа разрядов соединены соответственно

5 с входами разрядов порогового блока, выходы разрядов суммы., последнего сумматора группы блока свертки числаразрядов соединены с входами соответствующих разрядов первого слагаемого выходного сумматора,

0 выходы разрядов суммы крторого являются выходами разрядов преобразователя, выходы разрядов порогового блока соединены с входами соответствующих разрядов второго слагаемого выходного сумматора,-выхо5 ды разрядов с первого по f/2(r- мощность множества значений, остатков входного кода по модулю К) суммы первого сумматора группы блока сверткичисла разрядов соединены с прямыми входами соответствующих

0 разрядов первого слагаемого второго сумматора группы блока свертки числа разрядов, выходы с весом W переносов каждого сумматора, кроме второго и последнего, группы и выходы с весом W разрядов сум5 мы каждого сумматора, кроме первого и последнего, группы блока свертки числа разрядов соединены с входами разрядов с весами соответствующими единичным значениям двоичного кода чТлсла W mod К слагаемых последующих сумматоров труппы блока свертки числа разрядов, отличающийся тем, что, с целью сокращения аппаратурных затрат, выходы разрядов с (г/2 + по r-й суммы первого сумматора группы блока свертки числа разрядов соединены соответственно с инверсными входами разрядов второго слагаемого второго сумматора группы блока свертки числа разрядов, вход переноса и инверсный выход переноса второго сумматора группы блока свертки числа разрядов соединены соответственно с входом логической едини- цы преобразователя и с входом разряда единичного веса слагаемого последующего сумматрра группы блока свертки числа разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения по модулю К | 1989 |

|

SU1691834A1 |

| Устройство для преобразования количества единиц двоичного кода в код по модулю К | 1987 |

|

SU1527714A1 |

| Устройство для свертки двоичного кода в код по модулю К | 1986 |

|

SU1425845A1 |

| Преобразователь двоичного кода | 1986 |

|

SU1476614A1 |

| Устройство для контроля параллельного двоичного кода по модулю К | 1986 |

|

SU1425676A1 |

| Устройство для контроля параллельного двоичного кода по модулю К | 1986 |

|

SU1361557A1 |

| Преобразователь двоичного кода в код по модулю К | 1987 |

|

SU1429322A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1993 |

|

RU2110886C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для построения систем передачи и переработки дискретной информации. Целью изобретения является сокращениеаппаратурныхзатрат. Преобразователь двоичного кода в код по модулю К содержит блок 1 весового суммирования, пороговый блок 3, выходной сумматор 4 и блок 2 свертки числа разряда. При подаче входного кода на выходах блока 1 весового суммирования формируется t 2г + 1-разрядный код, остаток по модулю К которого равен остатку по модулю К входного кода. Код с выходов блока 1 поступает на входы блока 2 свертки числа разрядов, который формирует на своих выходах р log2 (К + 1) + 1-разрядный код, который поступает на входы выходного сумматора 4 и входы порогового блока 3, формирующего на своих выходах код вычета такой, что его сумми- рование с кодом на входе первого слагаемого выходного сумматора 4 дает на его выходах код остатка по модулю К. 4 ил. (Л С 1 со ю i ю 01121

Фиг. г

Фиг.3

55

| Преобразователь двоичного кода | 1986 |

|

SU1476614A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1401610A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для свертки двоичного кода в код по модулю К | 1986 |

|

SU1425845A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-05-07—Публикация

1989-11-09—Подача