Изобретение относится к вычислительной технике, предназначено для подсчета одноименHbix вдфр в двоичных кодах. По основному авт.св. № 450160 известно устройство для параллельного счета количества ещжиц (нулей) в двоичном числе, содержащее п-разрядкый входной регистр, log п групп сумматоров по n/2k сумматоров в каждой группе (1 k log п), выход суммы последнего сумматора каждой группы и выход переноса сумматора последней k-й группы соединены со входами соответствующих разрядов выходного регистра, входы каждого i-ro сумматора k-й группы соединены с выходами переноса 2i-ro к (21-1)-го сумматоров (k-I)-и группы с вы хо суммы (i-l)-ro сумматора k-й группы, выходы 2(-го и (2i-l)-ro разрядов входного регистра соединены со входами i-ro сумматора первой группы 1 . Устройство производит счет количества единиц двоичного п-разрядного числа как такового независимо от смыслового содержания информации в разрядах числа, т.е. для устройства безразлично то обстоятельство, что часть разрядов числа может содержать рабочую информацию (например операнд), а другая часть разрядов - вспомогательную информацию (например cn)OKe6Hbie признаки, контрольные разряды и т.п.). Однако при использовании такого устройства в ряде систем вычислительной техники возникает необходимость обеспечения двух режимов работы устройства. Подсчет числа единиц во всех п разрядах исходного числа (т.е. выполнение основной функции) - режим 1. Этот режим обеспечивает, например, периогдаческий счет числа функционирующих устройств вычислительной системы. Каждый разряд исходного числа соответствует определенному устройству. О в разряде - устройство не работает, 1 - устройство функционирует. Подсчет числа единиц в (п-1) разрядах - режим 2 п-й )азряд является контрольным и счету не подлежит. Этот режим необходим, когда информация на вход устройства поступает из каналов связи и каждое (п-1) разрядное входное число сопровождается контрольным разрядом.

37

Если на входной регистр известного устройства поступает двоичное число, у которого п-й разряд контрольный (контроль по mod 2 на нечетность), а просуммировать необходимо единицы в (п-1) разрядах, то в тех случаях, когда п-й разряд содержит 1 на вь ходном регистре устройства фиксируется число на единицу больше, чем следует.

Предполагая, что исходное число (с контролным разрядом) не искажается в тракте передачи от источника до входного регистра устройства, и само устройство функционирует правильно, анализ позволяет сделать следующие выводы:

а)младший разряд выходного регистра всег да устанавливается в 1, т.е. 1 в этом разряде - признак правильной работы устройства;

б)когда контрольный разряд равен О, число на выходном регистре соответствует

числу единиц в (п-1) разрядах исходного двоичного числа;

в)когда контрольный разряд равен 1, число на выходном регистре на единицу больше количества единиц в (п-1) разрядах исходного числа.

Таким образом, устройство не обеспечивает точного суммирования единиц для двоичных слов, имеющих один контрольный разряд.

Цель изобретения - расширение функциональных возможностей устройства, т.е. обеспечение возможности работы с двоичными числами, содержащими контрольный разряд, а также повышение достоверности, контроль правильности приема исходного двоичного числа и функционирования устройства.

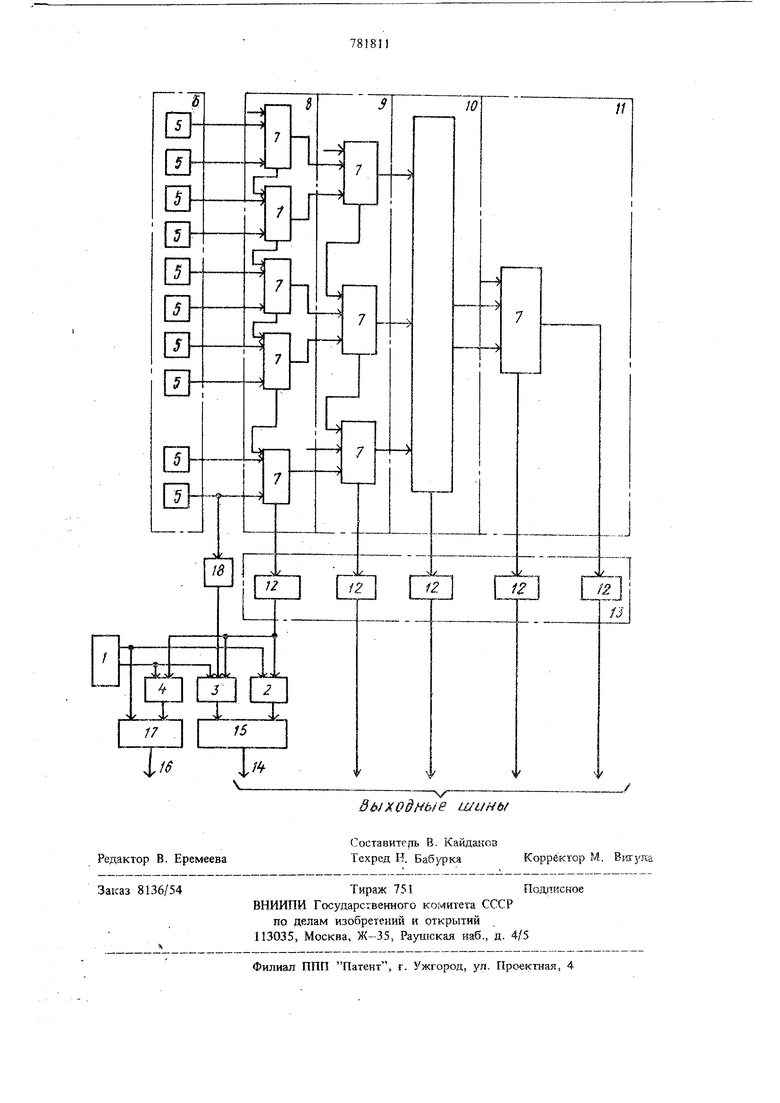

Поставленная цель достигается тем, что в устройство для параллельного счета количества единиц (нулей) в двоичном числе дополнительно введены три элемента И, два элемента ИЛИ элемент НЕ и триггер режима, причем первые входы элементов И соединены с выходом триггера младшего разряда выходного регистра второй вход первого элемента И соединен с первым выходом триггера режима и первым входом первого элемента ИЛИ, второй вход второго элемента И соединен с выходом элемента НЕ, вход которого соединен с выходом триггера контро. разряда входного регистра, третий вход второго элемента И соединен со вторым выходом триггера режима и вторым входом третьего элемента И, выходы первого и второго элементов И подключены соответ;ственно к первому -и второму входам второго элемента ИЛИ, выход которого является выходом младшего разряда выходного регистра, а выход третьего элемента И соединён со вторым входом первого элемента ИЛИ, выход которой соединен с шиной контроля.

На чертеже изображена схема устройства

4

Устройство содержит триггер I режима, элементы И 2-4, триггеры 5 входного регистра 6 сумматоры 7, объединенные в группы 8-1, триггеры 12 выходного регистра 13, выходную шину 14 разряда, элемент ИЛИ 15, шину 16 контроля, элемент ИЛИ 17, элемент НЕ 18.

Устройство работает следующим образом.

Перед началом работы триггер 1 режима устанавливается в одно из состояний Режим 1 или Режим 2, что и определяет функционирование устройства.

В первом режиме разрешающий потенциал с первого выхода триггера 1 подается на элемент И 2, запрещающий потенциал - со второго выхода триггера на вход1 1 элементов И 3 и 4. Элементы И 3 и 4 в этом режиме не функционируют. Исходное число фиксируется на триггерах 5 входного регистра 6. В результате работы сумматоров 7, объединенных в групы 8-11, на триггерах 12 врлходного регистра 13 фиксируется двоичный код, который является результатом подсчета единиц исходного числа. Выдача этого кода происходит в выходные шины устройства, причем все выходные шины, кроме одной (выходной шипы 14 младшего разряда). подключены к выходам триггеров 12. Выходная же шина 14 младшего разряда подключена к выходу элемента ИЛИ 1 Сигнал на шине 14 для данного режима работы устройства всегда соответствует сигналу на выходе триггера младшего разряда регистра 13 На шине 16 контроля постоянно фиксируется сигнал 1 отсутствия ошибки, поступающий с первого выхода триггера 1 режима через элемент ИЛИ 17.

Рассмотренный режим работы устройства применяется, когда необходимо суммировать единицы во всех п-разрядах исходного двоичного числа, т.е. этот режим полностью соответствует режиму работы известного устройства.

Второй режим применяется тогда, когда на вход устройства поступают двоичные числа, у которых п-й разряд контрольный, а суммировать единицы необходимо только в первых (п-1) разрядах.

Триггер 1 режима устанавливается в состояни когда элемент И 2 заблокирован,а на элементы И 3 и 4 подается с триггера 1 разрешаюцщй потенциал.

Рассмотрим два случая для этого режима, при условии, что при отсутствии искажения исходного числа в тракте передачи результат суммирования всегда дает 1 в младшем разряде (поскольку всегда число единиц в исходном числе должно быть нечетным) и наличие этой 1 является признаком правильной работы устройства. а)При поступлении на вход устройства исходного двончЕтого числа его контрольный разряд равен О. В этом случае результат суммирования на выходном регистре 13 равен числу единиц в (п-1) разрядах исходного чис ла и на выходной шине 14 младшего разряда имеет место тот же потенциал, что и на выходе триггера младшего разряда, т.е. 1. Это обеспечивается разрешающим потенциалом с выхода элемента НЕ 18 по входу, подключенн му к выходу триггера контрольного n-fb разряда исходного числа (поскольку контрольный разряд равен О). Для дан(гого случая на оба входа элемента И 4 подаются разрешающие потенциалы с триггера 1 режима и с вь1хода триггера младшего разряда регистра 13. Поэтому на шине 16 контроля фиксируется сигнал отсутствия ошибки 1. б)Контрольный разряд исходного числа равен 1. Результат суммирования, зафиксированный на регистре 13, на единицу больше, че следует иметь на выходе устройства. Коррекция содержимого регистра 13 на, -1 при выдаче в выходные шины устройства производится путем подачи запрешающего потенциала с выхода элемента НЕ 18 на вход элемента И 3. При этом на выходной шине 14 фиксируется О. На шине контроля 16, как и для случая а), фиксируется сигнал отсутствия ошибки, т.е. 1. Таким образом, в зависимости от состояния контрольного разряда исходного числа на выходной шине 14 младшего разряда результата фиксируется 1 (когда контрольный раз ряд равен О) или О (когда контрольный разряд равен 1). Если при передаче по тракту связи произошел единичный сбой в каком-либо разряде исходного числа (или групповой нечетный . сбой), то количество единиц в исходном числ станет четным и в результате суммирования этих единиц триггер младшего разряда регистра 13 установится в О. Наличие зтого О - признак искажения исходного числа. На шине 16 контроля при этом появляется сигнал ошибки, т.е. О. Следовательно, в режиме 2 устройством осзтцествляется не то1иько суммирование единиц (п-1) - разрядов исходного числа, но и контроль исходного птела. Сигнал О на шине 16 контроля появляется не только при сбое исходного числа, но и в том случае, когда исходное число верно, а неверно функционирует само устройство, т.е. осушествляется контроль функционирования устройства. Введение дополнительных элементов в состав устройства обеспечивает расширение его функций. Устройство может работать с числами, содержащими контрольный разрядки позволяет осуществить контроль правильности приема исходного числа и контроль функционирования устройства. Формула изобретения Устройство для параллельного счета количества единиц (нулей) в двоичном числе по авт.св. № 450160, отличающееся тем, что, с целью расширения его функциональных возможностей за счет работы с числами, содержащими контрольный разряд, и повышения достоверности, в него дополнительно введены три элемента К, два элемента ИЛИ, элемент НЕ и триггер режима, причем первые входы элементов И соединены с выходом триггера младшего разряда выходного регистра, второй вход первого элемента И соединен с первым вь.1ходом триггера режима и первым входом первого элемента ИЛИ, второй вход второго элемента И соединен с выходом элемента НЕ, вход которого соединен с выходом триггера контрольного разряда входного регистра, третий вход второго элемента И соединен со вторым выходом триггера режима и вторым входом третьего элемента И, выходы первого и второго элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого является выходом младшего разряда выходного регистра, а выход третьего элемента И соединен со вторым входом первого элемента ИЛИ, выход которой соединен с шиной контроля. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 450160, кл. G 06 F 5/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного счета количества единиц (нулей) в двоичном числе | 1981 |

|

SU968801A2 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Преобразователь число-импульсного кода в параллельный двоичный код | 1980 |

|

SU941992A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СИТУАЦИЙ | 2000 |

|

RU2195703C2 |

Авторы

Даты

1980-11-23—Публикация

1979-02-12—Подача