(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Устройство для подсчета количества единиц | 1990 |

|

SU1829119A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

Изобретение относится к вычислительной технике и позволяет вычислять частное Хот деления на константу (21+1) на комбинационной схеме, т.е. за один такт. Целью изобретения является повышение быстродействия. Устройство содержит элементы НЕ 2.1 и первый сумматор 1.1. домножающие делимое А на величину , а также последующие сумматоры 1.2-1.г, домножающие полученный результат на ряд величин (2+1), (2+1) и т.д., так что 1-й сумматор группы домножает на величину 2 I - Н (2 устройства результат А(2 + 1)...(2 I) и это определяет на выходе результат А(2Ч)(22{+1)(241+ + 1) + 1)...(2 2ГЈ X (2 -1), т.е. искомую величину X в старших разрядах результата. 1 ил.

in

vj

CJ

о

Os

ю

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ.

Известно устройство для деления, содержащее сумматор, регистр делимого, регистр делителя и матрицу умножения.

Недостатком устройства является его сложность.

Наиболее близким к предлагаемому является устройство для деления на константу (2+1), содержащее первый сумматор, регистр делимого, промежуточный регистр, группу элементов И, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, группу элементов НЕ, причем n-разрядный информационный вход регистра делимого является входом делимого устройства, а выходы п разрядов регистра делимого соединены с соответствующими входами первой группы входов сумматора, {младших выходов сумматора соединены с первыми входами соответствующих элементов И группы, выходы которых являются выходами остатка устройства, выходы сумматора (1+1), (1+2)п соединены с информационными входами промежуточного регистра, 1-й выход промежуточного регистра, i 1, n-f+1, соединен с входом соответствующего элемента НЕ группы, выход которого соединен с i-м входом второй группы входов сумматора, первый выход промежуточного регистра соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, (f+1)-u выход сумматора соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является старшим выходом остатка устройства и соединен с первым входом элемента И-НЕ, первый выход сумматора соединен с вторым входом элемента И-НЕ, выход счетчика соединен с входом разрешения счета счетчика и третьим инверсным входом элемента И-НЕ, выход которого соединен с входом разрешения приема промежуточного регистра и вторыми входами элементов И группы, синхровход промежуточного регистра обьединен с вычитающим входом счетчика и является тактовым входом устройства, вход сброса промежуточного регистра объединен с входом установки счетчика и син- хровходом регистра делимого и является

входом запуска устройства, входы (n-f+1)

п второй группы входов сумматора вход переноса сумматора подключены к единичной шине, старшие выходы сумматора (1+1), ..., п являются выходами частного устройства.

Недостатком устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия.

На чертеже представлена структурная схема устройства.

Устройство содержит сумматоры 1.1

НЕ 2.12.п, вход 3 делимого устройства и

выход 4 частного устройства. На входы 3 поступает делимое - n-разрядное двоичное число А,

Получение искомого частного X можно описать уравнением

или

А/(2Т+1) Х

А 2f- X+X

0) (2)

Отсюда следует, что частное X совпадает с делимым, сдвинутым на {двоичных разряда в сторону младших разрядов, при этом имеет место погрешность, которая определяется значением X. Эта величина тем меньше, чем больше величина сдвига, т.е. коэффициент при X в формуле (2). Эту величину сдвига можно увеличить умножая правую и левую части равенства на величину

(2с-1). Тогда в правой части имеет место выражение (2 -1). Дальнейшее увеличение коэффициента достигается умножением правой и левой части на величину (2+1),

HL

далее на величину (2 +1), вплоть до умножег - 1

ния на величину(2

A(2L-1)(22I+1)...(2

+ 1):

24

+ 1) (2 -1)Х,

(3)

0

5

где г - количество описанных домножений, дающих в правой части выражения величи24

ну (2 -1)Х, что определяет (2 {-п-1) точных разрядов результата.

Устройство вычисляет частное от деления величины А на (2+1) путем определения величины выражения, стоящего в правой части формулы (3).

Делимое А поступает на п младших входов первого слагаемого сумматора 1.1 через

группу элементов НЕ 2.1 2.п. Это же

делимое А поступает на входы второго слагаемого сумматора 1.1 с (t+1)-ro по (п+1)-й, г.е. сдвинутым монтажно на (.разрядов, что соответствует величине 2т. Сумматор 1.1 выполняет операцию вычитания з дополни- 5 тельном коде. При эт.ом с его выходов снимается величина А(). Она поступает на следующий сумматор, который выполняет домножение величины А(2-1) на коэффициент (2 +1). Величина A(2t -1) поступает на

0

(n+О младших входов первого слагаемого сумматора 1.2 и на входы второго слагаемого с (2{+1)-го по (n+30-й сумматора 1.2, т.е. сдвинутой монтажно на 21, разрядов. Входы первого слагаемого с (n+t+1)-ro по ( и 21 младших входов второго слагаемого сумматора подключены к нулевой шине. С выхода сумматора 1.2 снимается величина А(2 -1)(2 +1). Для i-ro сумматора на входы первого слагаемого с первого по (п+( -1)Ј+1-2)-й поступает величина А(221 2 t

1)(22t+1)...(2+1), полученная на

выходах (Ы)-го сумматора. Эта же величина поступает на входы второго слагаемого i-ro сумматора с (2и+1)-го по (п+(2-1){+1-2)-й, т.е. монтажно сдвинутой на 2 Ч разрядов. При этом с выходов сумматора снимается вели 1

.2(,

чинаА(2Ч)()...(2

+ 1). Единица с

выхода переноса (i-1)-ro сумматора поступает на входы (n+(2-1){+i-1 и (n+(2i+1-1)l+M) сумматора i.C выходов сумматора 1.гснима2Г 1 С

ется величина А(21-1))...(2+1).

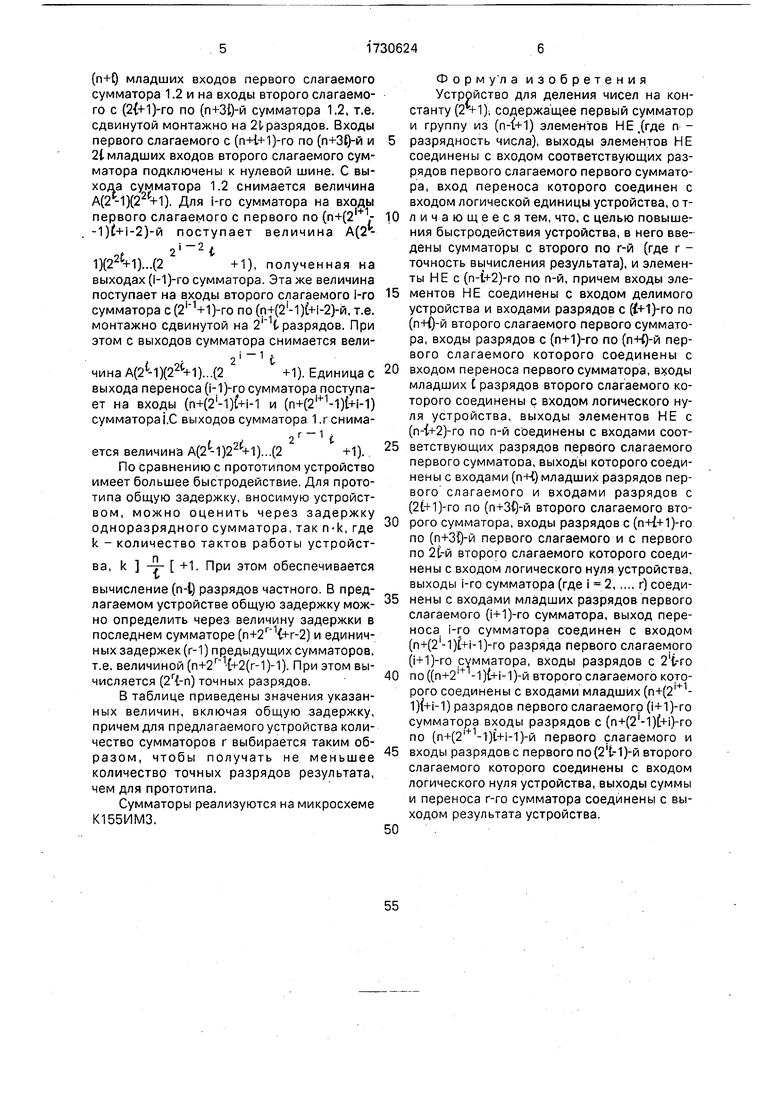

По сравнению с прототипом устройство имеет большее быстродействие. Для прототипа общую задержку, вносимую устройством, можно оценить через задержку одноразрядного сумматора, так n-k, где k - количество тактов работы устройства, k -г- +1. При этом обеспечивается

V

вычисление (п-1) разрядов частного. В предлагаемом устройстве общую задержку можно определить через величину задержки в последнем сумматоре (п+2г Ч+г-2) и единичных задержек (г-1) предыдущих сумматоров, т.е. величиной (п+2н{+2(г-1)-1). При этом вычисляется (2Ч-п) точных разрядов.

В таблице приведены значения указанных величин, включая общую задержку, причем для предлагаемого устройства количество сумматоров г выбирается таким образом, чтобы получать не меньшее количество точных разрядов результата, чем для прототипа.

Сумматоры реализуются на микросхеме К155ИМЗ.

0

5

0

5

0

5

0

5

0

Формула изобретения Устройство для деления чисел на константу (), содержащее первый сумматор и группу из () элементов НЕч(где п - разрядность числа), выходы элементов НЕ соединены с входом соответствующих разрядов первого слагаемого первого сумматора, вход переноса которого соединен с входом логической единицы устройства, о т- личающееся тем, что, с целью повышения быстродействия устройства, в него введены сумматоры с второго по r-й (где г - точность вычисления результата), и элементы НЕ с (п-(+2)-го по n-й, причем входы элементов НЕ соединены с входом делимого устройства и входами разрядов с (Ј+1)-го по (n+0-й второго слагаемого первого сумматора, входы разрядов с (п+1)-го по (п-К)-й первого слагаемого которого соединены с входом переноса первого сумматора, входы младших t разрядов второго слагаемого которого соединены с входом логического нуля устройства, выходы элементов НЕ с (n-i+2)-ro по n-й соединены с входами соответствующих разрядов первого слагаемого первого сумматооа, выходы которого соединены с входами (n-Ч) младших разрядов первого слагаемого и входами разрядов с (21+1)-го по (п+3()-й второго слагаемого второго сумматора, входы разрядов с ()-го по (п+3{)-й первого слагаемого и с первого по 2Ч-й второго слагаемого которого соединены с входом логического нуля устройства, выходы i-ro сумматора (где i 2г) соединены с входами младших разрядов первого слагаемого (i+1)-ro сумматора, выход переноса i-ro сумматора соединен с входом (п+(2-1)Ј+И)-го разряда первого слагаемого (i+1)-ro сумматора, входы разрядов с 2 i-ro по ((п+2 + -1){+М)-й второго слагаемого которого соединены с входами младших (n+(2l+1- 1)f+i-1) разрядов первого слагаемого (i+1)-ro сумматора входы разрядов с (п+(2-1)(+)-го по (п+(2 +1-1){+И)-й первого слагаемого и входы разрядов с первого по (21-1)-й второго слагаемого которого соединены с входом логического нуля устройства, выходы суммы и переноса r-го сумматора соединены с выходом результата устройства.

Примечание. Допустим Ј 4.

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1990-04-17—Подача