Изобретение относится к импульсной технике и может быть использовано для построения интегральных логических схем.

Цель изобретения - повышение стабильности параметров транзисторно-транзисторного логического элемента при непрерывных радиационных воздействиях.

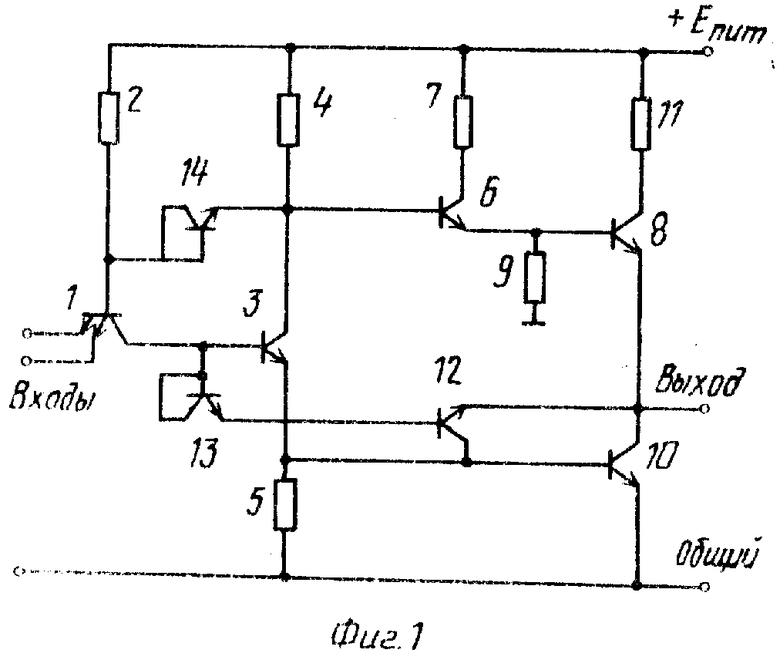

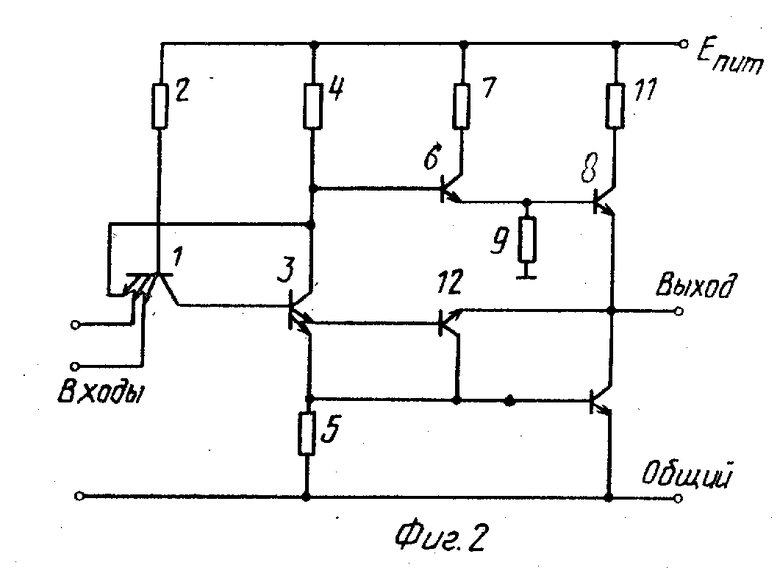

На фиг. 1 и 2 представлены принципиальные электрические схемы транзисторно-транзисторного логического элемента соответственно по пп.2,3 формулы изобретения.

Транзисторно-транзисторный логический элемент (фиг.1) содержит входной многоэмиттерный транзистор 1, база которого через резистор 2 соединена с шиной питания, коллектор - с базой фазоразделительного транзистора 3, коллектор которого через резистор 4 соединен с шиной питания, а эмиттер через резистор 5 - с общей шиной, к коллектору фазоразделительного транзистора 3 подключена база первого транзистора 6 выходного эмиттерного повторителя, коллектор которого через резистор 7 соединен с шиной питания, а эмиттер подключен к базе второго транзистора 8 выходного эмиттерного повторителя и через резистор 9 соединен с общей шиной, коллектор второго транзистора 8 выходного эмиттерного повторителя через резистор 11 соединен с шиной питания, а эмиттер соединен с коллектором выходного нагрузочного транзистора 10, эмиттер которого подключен к общей шине, а база соединена с эмиттером фазоразделительного транзистора 3 и коллектором рассасывающего транзистора 12, эмиттер которого подключен к общей шине, а база соединена с эмиттером фазоразделительного транзистора 3 и коллектором рассасывающего транзистора 12, эмиттер которого подключен к коллектору выходного нагрузочного транзистора 10, а база соединена с Р-областью первого дополнительного диодного элемента 13 на эмиттере первой дополнительной транзисторной структуры, база и коллектор которой соединены вместе и подключены к базе фазоразделительного транзистора 3, к коллектору фазоразделительного транзистора 3 подключена n-область второго дополнительного диодного элемента 14, выполненного на эмиттере второй дополнительной транзисторной структуры, база и коллектор которой соединены вместе и подключены к базе входного многоэмиттерного транзистора 1. На фиг.2 представлен вариант электрической схемы предлагаемого логического элемента, в котором роль дополнительных диодных элементов 13 и 14 (см.фиг.1) выполняют дополнительные эмиттеры соответственно фазоразделительного транзистора 3 и входного многоэмиттерного транзистора 1. Для улучшения передаточной характеристики (фиг.1 и 2) допускается вместо резистора 5 включать цепочку из двух резисторов и транзистора, эмиттер которого подключен к общей шине, а база и коллектор через соответствующие резисторы подключены к эмиттеру фазоразделительного транзистора 3.

Транзисторно-транзисторный логический элемент работает следующим образом.

Если на один или несколько входов элемента (фиг.1) поступает низкий уровень напряжения (Uвхo≈0,2В), то на базе многоэмиттерного транзистора 1 устанавливается напряжение ≈0,9 В. Фазоразделительный транзистор 3 и выходной нагрузочный транзистор 10 закрыты, поэтому на коллекторе фазоразделительного транзистора 3 устанавливается напряжение, близкое к напряжению питания. Транзисторы 6,8 выходного эмиттерного повторителя открыты, выходной нагрузочный транзистор 10 закрыт, на входе схемы устанавливается высокий уровень напряжения, через нагрузку протекает ток транзисторов 6, 8 выходного эмиттерного повторителя. Диодный элемент 14, включенный между коллектором фазоразделительного 3 и базой входного многоэмиттерного 1 транзисторов находится под обратным смещением. Рассасывающий транзистор 12 закрыт, его переход эмиттер-база и диодный элемент 13 находятся под обратным смещением. Следовательно, диодные элементы 13, 14 и транзистор 12 в режиме высокого уровня на выходе не влияют на статические характеристики элемента.

Когда на все входы элемента подается высокий уровень напряжения (Uвх 2,4 B), на базе входного многоэмиттерного транзистора 1 устанавливается напряжение порядка 2,1 В, транзистор 1 работает в инверсном активном режиме и открываются переходы: коллектор - база многоэмиттерного транзистора 1 и эмиттер - база фазоразделительного и выходного нагрузочного транзисторов 3, 10. На коллекторе фазоразделительного транзистора 3 устанавливается напряжение ≈1,4 В, транзисторы 6, 8 выходного эмиттерного повторителя закрыты, а выходной нагрузочный транзистор открыт и обеспечивает протекание тока от подключенных на выходе элементов. На выходе схемы устанавливается напряжение низкого уровня. Эмиттер рассасывающего транзистора 12 подключен к точке с низким потенциалом, а база через диодный элемент 13 соединена с точкой, потенциал которой равен ≈ 1,4 В. Следовательно, рассасывающий транзистор 12 открыт и шунтирует коллекторный переход выходного нагрузочного транзистора 10, ограничивая высокое быстродействие элемента при переключении из состояния низкого уровня в состояние высокого уровня.

2,4 B), на базе входного многоэмиттерного транзистора 1 устанавливается напряжение порядка 2,1 В, транзистор 1 работает в инверсном активном режиме и открываются переходы: коллектор - база многоэмиттерного транзистора 1 и эмиттер - база фазоразделительного и выходного нагрузочного транзисторов 3, 10. На коллекторе фазоразделительного транзистора 3 устанавливается напряжение ≈1,4 В, транзисторы 6, 8 выходного эмиттерного повторителя закрыты, а выходной нагрузочный транзистор открыт и обеспечивает протекание тока от подключенных на выходе элементов. На выходе схемы устанавливается напряжение низкого уровня. Эмиттер рассасывающего транзистора 12 подключен к точке с низким потенциалом, а база через диодный элемент 13 соединена с точкой, потенциал которой равен ≈ 1,4 В. Следовательно, рассасывающий транзистор 12 открыт и шунтирует коллекторный переход выходного нагрузочного транзистора 10, ограничивая высокое быстродействие элемента при переключении из состояния низкого уровня в состояние высокого уровня.

Диодный элемент 14 между базой входного многоэмиттерного транзистора 1 и коллектором фазоразделительного транзистора 3 открыт, стабилизируя напряжение на коллекторе на уровне ≈+ 1,4 В и ограничивая насыщение фазоразделительного транзистора 3, в результате чего обеспечивается высокое быстродействие схемы при переключениях.

Анализ распределения напряжений в предлагаемом элементе показывает, что величина выходного напряжения низкого уровня определяется из выражения

Uвыхо=(Uэбт3+Uэб10)-Uэбт12+Uэбд13), (1) где Uэбт3,Uэбт10,Uэбт12 - падения напряжений на открытых переходах эмиттер-база транзисторов 3,10,12, Uэбд13 - падение напряжения на прямосмещенном диодном элементе 13 в цепи рассасывающего транзистора 12.

Из анализа выражения (1) следует, что Uвыхо определяется разностью падений напряжения на двух парах параллельно включенных цепочек из переходов эмиттер-база. Разность падений напряжений на рассматриваемых парах переходов возникает за счет различия протекающих через них токов. Эта величина не может быть большой и, как правило, не превышает значений ≈0,1-0,2 В, так как вольтамперная характеристика (ВАХ) p-n-перехода описывается экспоненциальной функцией, а разность падений напряжений ΔU на переходах, через которые протекают разные токи I1 и I2, определяется из выражения

ΔU =  ln

ln , (2) где ϕ - температурный потенциал kТ/q (при Т ≈ 300 К ϕ≈ 0,026 В), m - коэффициент неидеальности ВАХ, который может принимать значения от 1 до 2. При одновременном изменении в допустимых пределах коэффициентов усиления всех транзисторов элемента разность падений напряжений ΔU остается постоянной, что обеспечивает стабильности выходного напряжения и быстродействия при внешних воздействиях (изменения коэффициентов усиления транзисторов, входящих в состав элемента, могут происходить, например, из-за колебаний температуры или из-за воздействия проникающих излучений).

, (2) где ϕ - температурный потенциал kТ/q (при Т ≈ 300 К ϕ≈ 0,026 В), m - коэффициент неидеальности ВАХ, который может принимать значения от 1 до 2. При одновременном изменении в допустимых пределах коэффициентов усиления всех транзисторов элемента разность падений напряжений ΔU остается постоянной, что обеспечивает стабильности выходного напряжения и быстродействия при внешних воздействиях (изменения коэффициентов усиления транзисторов, входящих в состав элемента, могут происходить, например, из-за колебаний температуры или из-за воздействия проникающих излучений).

Из сказанного выше следует, что выходное напряжение низкого уровня предлагаемого элемента имеет достаточно низкие значения, что обеспечивает большой запас помехоустойчивости, и достаточно стабильно при одновременном изменении коэффициента усиления транзисторов, например, из-за внешних воздействий.

В предлагаемом элементе напряжение на коллекторе фазоразделительного транзистора 3 (Uкфрт) меньше напряжения на базе входного многоэмиттерного транзистора 1 на величину падения напряжения на прямосмещенном диодном элементе 14 и составляет примерно 1,4 В.

Сопоставление величин напряжений в наиболее характерных точках известного и предлагаемого элементов свидетельствует о том, что характеристики известного элемента чувствительны к изменениям коэффициента усиления рассасывающих транзисторов и отклонениям от расчетных значений номиналов резисторов в цепи базы рассасывающих транзисторов, в то время как предлагаемый элемент не имеет этих недостатков, так как величина падения напряжения на эмиттерных переходах, изготовленных в одном технологическом цикле, практически не имеет разброса и слабо меняется при изменениях токов, которые могут быть вызваны вариацией коэффициентов усиления транзисторов при различных внешних воздействиях.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

Изобретение относится к импульсной технике и может быть использовано для построения интегральных логических схем. Цель изобретения - повышение стабильности параметров транзисторно-транзисторного логического элемента при непрерывных радиационных воздействиях. Транзисторно-транзисторный логический элемент содержит входной многоэмиттерный транзистор, фазоразделительный транзистор, первый и второй транзисторы выходного эмиттерного повторителя, выходной нагрузочный транзистор, рассасывающий транзистор, шесть резисторов и два дополнительных диодных элемента, при этом дополнительные диодные элементы могут быть реализованы на эмиттерных переходах дополнительных транзисторов, у которых коллектора соединены с базами или на дополнительных эмиттерных перепадах фазоразделительного транзистора и входного многоэмиттерного транзистора. Введение дополнительных диодных элементов позволяет понизить значение низкого логического уровня и повысить значение высокого логического уровня на выходе при сохранении быстродействия при радиационных воздействиях. 2 ил.

| Л. Б. РОДИНи К. Б. Турецкийj: ;I ^i>& | 0 |

|

SU344585A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-07-30—Публикация

1989-10-11—Подача