1

Изобретение относится к технике передачи дискретной информации и может быть применено при проектировании и построении аппаратуры передачи данных.

Из.вестны устройства для цикловой синхронизации, позволяющие определить фазу рекуррентной последовательности длины ;V по зачетному отрезку длины /.

Одна,ко в известных устройствах не предусмотрено исправление трансформированного символа в зачетном отрезке, что значительно снижает вероятность правильного определения на приеме закона формирования рекуррентной последовательности за время ее цикла, т. е. помехоустойчивости устройств.

Целью изобретения является повышение помехоустойчивости устройства для цикловой синхронизации.

Для этого между выходом сумматора по модулю два и входом счетчика включен дополнительный сумматор по модулю два, к второму входу которого подключен второй ключ, второй выход которого соединен с входом регистра сдвига с управляемой обратной связью, дополнительный выход которого соединен с входом второго ключа, а выход счетчика длины зачетного отрезка дополнительно подключен к второму входу второго ключа и пусковому входу дешифратора конца рекурренты.

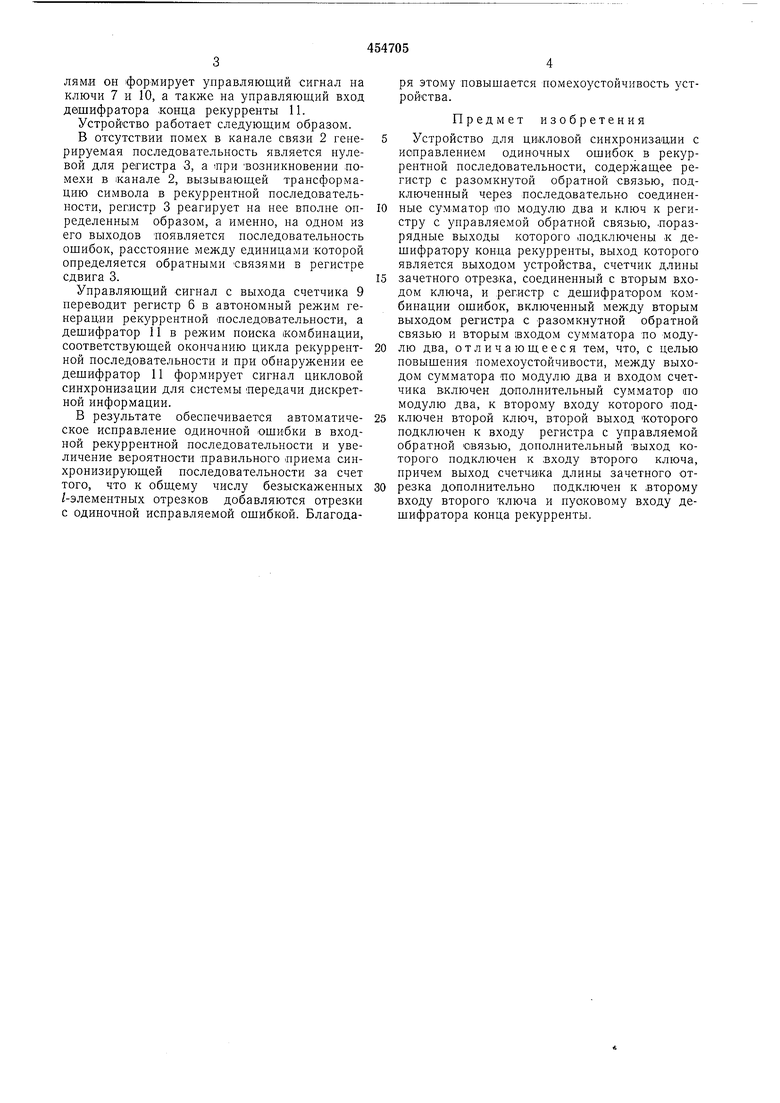

На чертеже приведена структурная схема устройства.

Устройство для циклической синхронизации с исправлением одиночных ошибок в рекуррентной последовательности содержит передающий генератор 1 рекуррентной последовательности на п-разрядном регистре сдвига с обратными связями, канал связи 2, через который генерируемая па выходе генератора 1

иоследовательность поступает па вход л-разрядного регистра сдвига 3 с разомкнутой обратной связью, регистр 4, на вход которого поступает последовательность ошибок с выхода регистра 3, причем регистр 4 содержит

дешифратор 4-1 комбинации ошибки в рекуррентной последовательности, который после дешифрации ошибки формирует управляющий сигнал на одпн вход сумматора по модулю два 5, на второй вход которого поступает рекуррентная последовательность с выхода регистра 3 с трансформированным символом.

Восстановленная рекуррентная последовательность с выхода сумматора 5 поступает па

вход регистра с управляемой обратной связью 6 через ключ 7 и заполняет регистр, а также на вход сумматора 8, на второй вход которого поступает последовательность. Выход сумматора 8 соединен с входом счетчика длины

зачетного отрезка 9 и при заполнении его нулями он формирует управляющий сигнал на ключи 7 и 10, а также на управляющий вход дещифратора конца рекурренты 11.

Устройство работает следующим образом.

В отсутствии помех в канале связи 2 генерируемая последовательность является нулевой для регистра 3, а при возникновении помехи в канале 2, вызывающей трансформацию символа в рекуррентной последовательности, регистр 3 реагирует на нее вполне определенным образом, а именно, на одном из его выходов появляется последовательность ощибок, расстояние между единицами которой определяется обратными связями в регистре сдвига 3.

Управляющий сигнал с выхода счетчика 9 переводит регистр 6 в автономный режим генерации рекуррентной последовательности, а дешифратор 11 в режим ноиска комбинации, соответствующей окончанию цикла рекуррентной последовательности и при обнаружении ее дещифратор 11 формирует сигнал цикловой синхронизации для системы передачи дискретной информации.

В результате обеспечивается автоматическое исправление одиночной ощибки в входной рекуррентной последовательности и увеличение вероятности правильного приема синхронизирующей последовательности за счет того, что к общему числу безыскаженных /-элементных отрезков добавляются отрезки с одиночной исправляемой ощибкой. Благодаря этому повыщается помехоустойчивость устройства.

Предмет изобретения

Устройство для цикловой синхронизации с исправлением одиночных ошибок в рекуррентной последовательности, содержащее регистр с разомкнутой обратной связью, подключенный через последовательно соединенные сум.матор то модулю два и ключ к регистру с управляемой обратной связью, .поразрядные выходы которого .подключены к дещифратору конца рекурренты, выход которого является выходом устройства, счетчик длины

зачетного отрезка, соединенный с вторым входом ключа, и регистр с дещифратором комбинации ошибок, включенный между вторым выходом регистра с разомкнутной обратной связью и вторым входом сумматора по модулю два, отличающееся тем, что, с целью повыщения помехоустойчивости, между выходом сумматора тто модулю два и входом счетчика включен дополнительный сумматор по модулю два, к второму входу которого подключей второй ключ, второй выход которого подключен к входу регистра с управляемой обратной связью, дополнительный выход которого подключен к входу второго ключа, причем выход счетчика длины зачетного отрезка дополнительно подключен к второму входу второго ключа и пусковому входу дещифратора конца рекурренты.

. ...

ufj-jfLf 4 1 r

liJiirur

7 Ft

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ И ДЕЦИМАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820337C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2803318C1 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| Устройство рекуррентного фазового пуска | 1986 |

|

SU1356250A1 |

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU944137A1 |

| УСТРОЙСТВО ПОРОГОВОГО ДЕКОДИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТИ ГОЛДА | 2024 |

|

RU2832456C1 |

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ С ФУНКЦИЕЙ ВЫДЕЛЕНИЯ ЗАЧЕТНЫХ ИМПУЛЬСОВ В СКОЛЬЗЯЩЕМ ОКНЕ | 2013 |

|

RU2553089C2 |

Авторы

Даты

1974-12-25—Публикация

1971-10-08—Подача