1

Изобретение относится к области цифровой техники и может использоваться в цифровых сиптезатора.ч частоты.

Известен счетчик с коэффициентом счета 2 + 1, содержащий схему блокировки, выход которой соединен с входом «-разрядного двоичиого счетчика на 1посл едовательно соединенных счетных триггерах, выходами подключенных к входам управляющего дешифратора, дополнительный счетный триггер, один из выходов которого соединен с управляющим входом схемы блокировки, входом соединенной с входом инвертора и входной щиной.

Целью изобретения является повышение быстродействия.

Для этого в предлагаемом счетчике выход инвертора соединен с опращивающим входом упра1вляющего дешифратора, выход которого подключен к счетному входу дополнительного счетного триггера, другим выходом соединенного с единичными установочными входами счетных триггеров «-разрядного двоичj;oro счетчика.

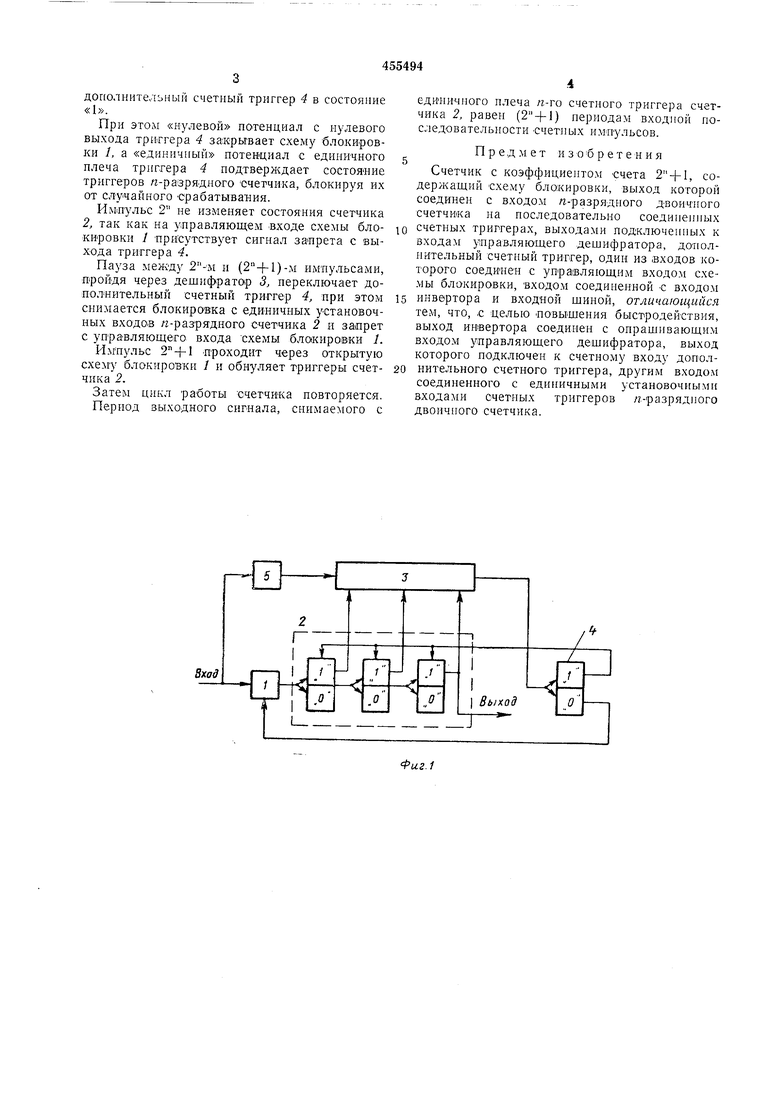

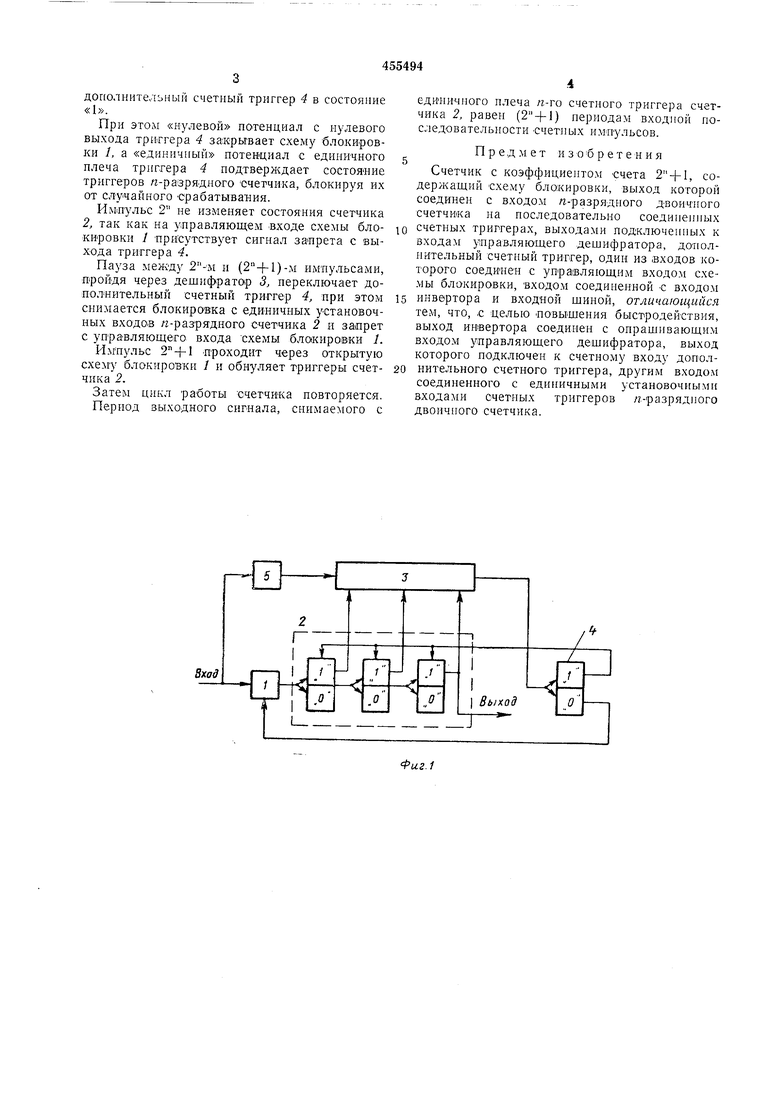

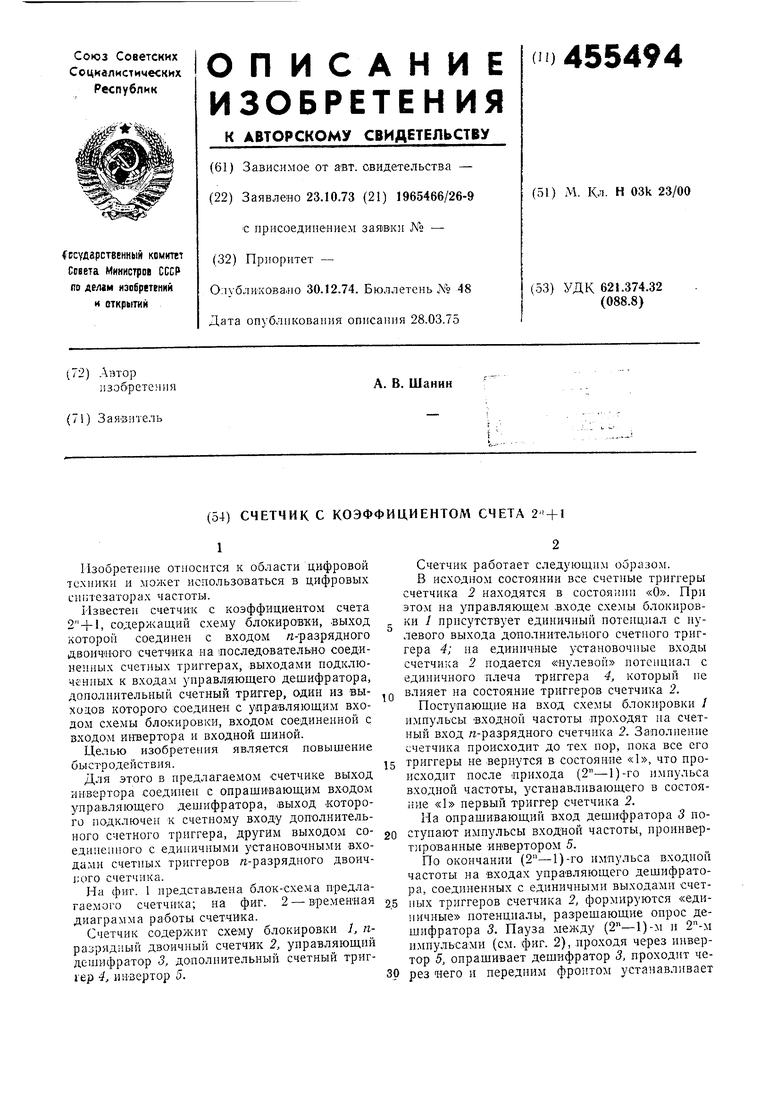

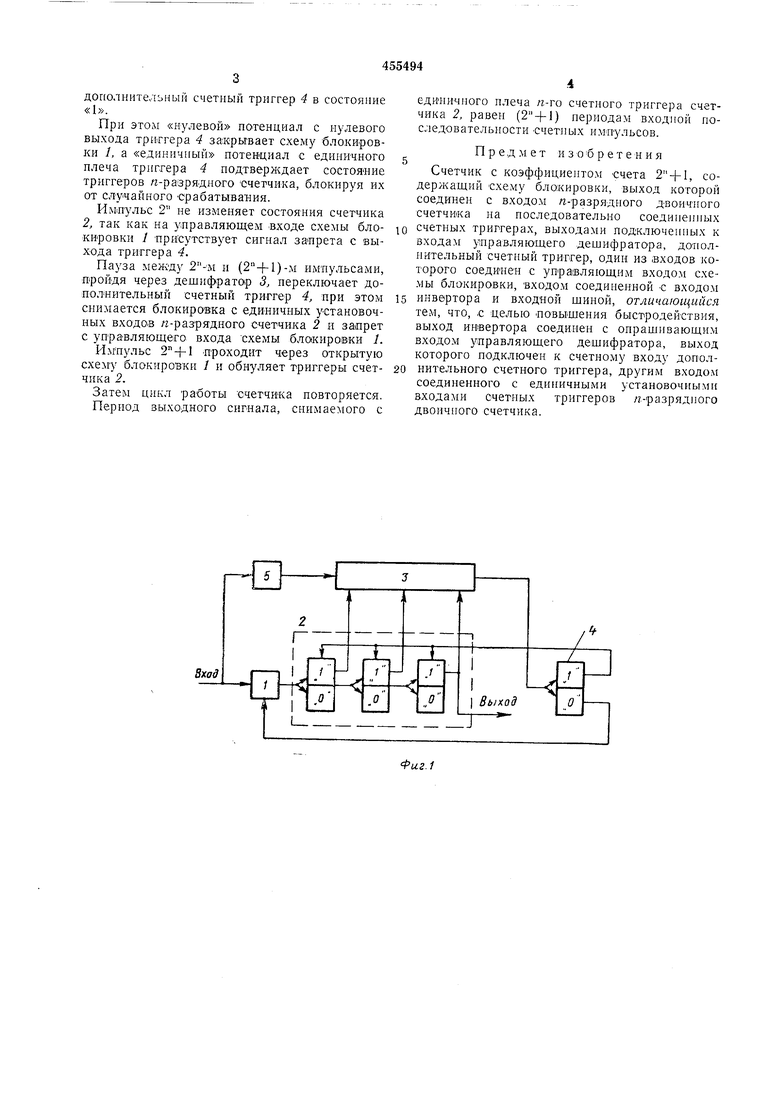

На фиг. 1 представлена блок-схема предлагаемого счетчика; на фиг. 2 -временная диаграмма работы счетчика.

Счетчик содержит схему блокировки 1, празрядиый двоичный счетчик 2, управляющий дешифратор 3, дополнительный счетный триггер 4, инвертор 5.

Счетчик работает следующим образом. В исходном состоянии все счетные триггеры счетчика 2 находятся в состоя .ши «О. При этом на управляющем входе схемы блокиров.. ки / присутствует единичный потенциал с нулевого выхода дополнительного счетного триггера 4; на единичные установочные входы счетчика 2 подается «нулевой иотсициал с единичного илеча триггера 4, который не

Q влияет на состояние триггеров счетчика 2.

Поступающие на вход схемы блокировки / и.мпульсы входной частоты проходят на счетный вход и-разрядного счетчика 2. Заполнепие счетчика происходит до тех пор, пока все его

5 триггеры не вернутся в состояние «1, что происходит после лрихода ()-го импульса входной частоты, устанавливающего в состояние «1 первый триггер счетчика 2. На опрашивающий вход дешифратора 3 поступают импульсы входной частоты, проинвертированные инвертором 5.

По окончании ()-го имнульса входной частоты на входах управляющего дешифратора, соединенных с единичными выходами счет,5 иых триггеров счетчика 2, формируются «единичные потенциалы, разрешающие опрос дешифратора 3. Пауза между ()-м и импульсами (см. фиг. 2), проходя через инвертор 5, опрашивает дешифратор 3, проходит через него и передним фронтом устанавливает

дополнительный счетный триггер 4 в состояние «1.

При этом «нулевой потенциал с нулевого выхода триггера 4 закрывает схему блокировки /, а «единичный потенциал с единичного плеча триггера 4 подтверждает состоящие триггеров я-разрядного очетчика, блокируя их от случайного срабатывания.

Имлульс 2 не изменяет состояния счетчика 2, так как на управляющем входе схемы блокировки 1 -присутствует сигнал запрета с выхода триггера 4.

Пауза между и ()-м импульсами, пройдя через дешифрато1р 3, переключает дополщительный счетный триггер 4, при этом снимается блокировка с единичных установочных входов «-разрядного счетчика 2 и запрет с управляющего входа схемы бло1кир0)вки 1.

Импульс проходит через открытую схему блокировки / и обнуляет триггеры счетчика 2.

Затем цикл работы счетчика повторяется.

Период выходного сигнала, снимаемого с

единичного илеча /г-го счетного триггера счетчика 2, равен () периодам входной носледовательности счетных имтгульсов.

Предмет изобретения

Счетчик с коэффициентом счета , содержащий с.хему блокировки, выход которой соединен с входом п-разрядного двончного счетчика на последовательно соединенных

счетных триггерах, выходами подключенных к входам унравляющего дешифратора, дополнительный счетный триггер, один из входов которого соедине-н с управляющим входом схе.мы блокировки, входом соединенной с входом

инвертора и входной шиной, отличающийся тем, что, с целью повышения быстродействия, выход инвертора соедннен с опрашнвающнм в.ходом управляющего дешифратора, выход которого подключен к счетному входу догюлнительного счетного триггера, другим входом соединенного с единичными установоч1 ыми входами счетных триггеров л-разрядного двоичного счетчика.

2 3 ff 5 8 7 В 9 W i1 12 13 1 15 16

- лшшп ишягтгишлВыход 1 -первого ,разрядй-.

Выход

второгс

разряда

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следованияиМпульСОВ | 1979 |

|

SU839066A1 |

| Счетчик с коэффициентом счета 2 +1 | 1978 |

|

SU766021A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ЛЮБЫЛ! ЦЕЛОЧИСЛЕ.ННЫМ КОЭФФИЦИЕНТОЛ^ ДЕЛЕНИЯ | 1972 |

|

SU347927A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Устройство для программного счета изделий | 1985 |

|

SU1365103A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕВЕРСОМ МАГНИТНОЙ ЛЕНТЫ | 1987 |

|

RU1540558C |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

1 3 Ч 5 6 7 8 ВыхоЗ wSepmopaS

Выход дешиф- - ратора 3

Выход 1 триггера

Выход О

.триггера

Выход

juuifUF LJumrumnub см мы 1

ял

L 3 W И 12 13 1J+ 15 18 jinjinjuiru

Авторы

Даты

1974-12-30—Публикация

1973-10-23—Подача