I

Изобретение относится к импульсн технике и может быть использовано в автоматике и синтезаторах частот радиотехнических систем.

Известен делитель частоты следования импульсов с любым целочисленн коэффициентом деления, состоящий из счетчика, триггера, дешифратора и схем совпадения l ,

Недостаток данного делителя низкое быстродействие.

.Наиболее близким по технической сущности к изобретению является пересчетное устройство, содержащее элемент блокировки, вькод которого соединен с входом п-разрядного двоичного счетчика на последовательно соединенных счетных триггерах, выходами подключенных к входам управляющего дешифратора, дополнительный счгетньй триггер, один из входов которого соединен с управляющим входом элемента блокировки, входом соединенного с входом инвертора к

входной шиной, при этом выход ин- веротора соединен с опрашивающим входом управлякяцего дешифратора, выход которого подключен к счетному входу дополнительного счетного . триггера, другим входом соединенного с единичными установочными входами счетных триггеров разрядного двоичного счетчика 2. .

Однако это устройство характеризуется недостаточно высоким быстродействием и ограниченными функциональшлми возможностями, так как оно позволяет получить.только один коэффициент деления.

Цель изобретения - повьш1ение быстродействия при одновременном расширении функциональных возможностей.

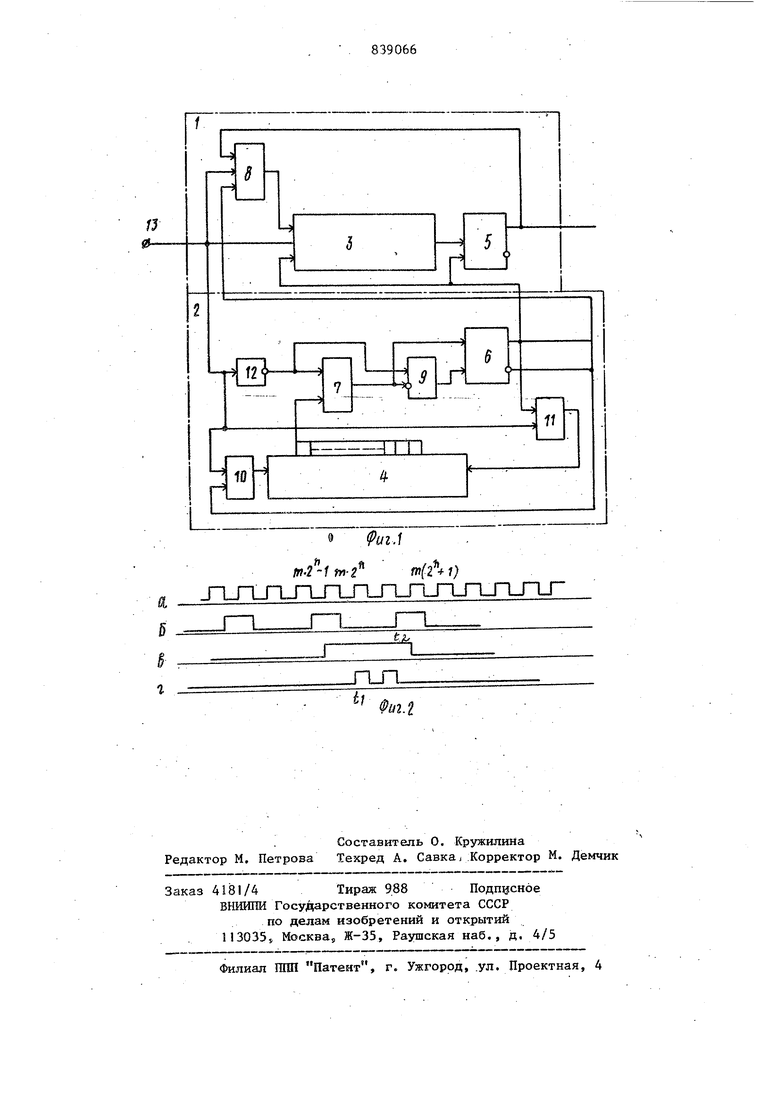

Поставленная цепь достигается тем, что в делитель частоты следования импульсов, содержащий делитель частоты на 2 + 1,- включающий в себя счетчик импульсов, элемент совпадения и триггер, введен делитель частоты на m , включающий в себя дополнител ный триггер, дополнительные элемен ты совпадения дешифратор, инвертор и дополнительный счетчик импульсов разрядные выходы которого соединены с группой входов дешифратора, устан вочный вход - с выходом первого до полнительного элемента совпадения, счетный вход - с выходом второго дополнительного элемента совпадения первый вход которого соединен с пер вым входом элемента совпадения, входной шиной, счетным входом счетч ка, первым входом первого дополните ного элемента совпадения и входом инвертора, выход которого соединен с управляющим входом дешифратора и первым входом третьего дополнительного элемента совпадения, второй вход которого подключен к выходу дешифратора и первому входу дополнительного триггера, второй вход которого соединен с выходом третьего дополнительного элемента совпадения, а прямой выход - со вторым входом первого дополнительного элемента совпадения, с управляющим входом счетчика импульсов и первым входом триггера, второй вход которого подключен к выходу счетчика импульсов, а вьпсод.- ко второму входу элемента совпадения, при этом инверсный выход дополнительного триггера соединен со вторым входом второго дополнительного элемента совпадения и третьим входом элемента совпадения, выход которого подключен к установочному счетчика импульсов. На фиг.1 представлена структурна схема устройства; на 4мг.2 - времен ные диаграммы,поясняющие его работу Устройство содержит делитель 1 частоты на . 2 + 1, делитель .2 часто на т, счетчики 3 и 4 импульсов, триггеры 5 и 6, дешифратор 7, элементы 8-11 совпадения, инвертор 12 входную шину 13. Устройство работает следующим об разом. На входную шину 13 подается непрерывная последовательность импул сов (фиг.2а). Счетчик 3 и триггер 5 могут изменять свое состояние по сигналам, подаваеглм на входную ши 13 только при наличии высокого пот циала на управляющем входе счетчик 3. Исходное состояние делителя час гы характеризуется наличием низких потенциалов на выходах счетчиков 3 и 4, а также на выходах триггеров 5 и 6. Дешифратор 7 должен быть настроен на число т-1. На счетный вход счетчика 4 через элемент 10, открытый сигналом с инверсного выхода триггера 6, поступает входная последовательность импульсов. Счетчик 4 изменяет свое прихода (m-l) импульсостояние до са, когда дешифратор 7 оказывается подготовленным к срабатыванию. Сигнал на его выходе, появляющийся по заднему фронту (m-l)-го входного импульса, устанавливает триггер 6 в состояние, характеризующееся наличием высокого потенциала на его прямом выходе. Таким образом, к приходу т-го импульса входной последовательности элемент 10 закрыт, а элемент 11 открыт. Тогда m входной импульс, проходя через элемент 11, устанавливает счетчик 4 в нулевое состояние. Сигнал с выхода дешифратора 7 прекращается и триггер 6 устанавливается в исходное состояние по заднему фронту т-го импульса. Сигнал на выходе триггера 6 характеризуется частотой в m раз меньшей частоты сигнала на входной щине 13. Длительность сигнала с выхода триггера 6 равна одному периоду входной частоты. Состояние счетчика 3 при прохождении (m-l) входных импульсов не изменяется вследствие наличия на управляющем входе счетчика 3 низкого потенциала. Однако каждый m входной импульс изменяет его состояние одновременно с обнулением счетчика 4. Если считать, что счетчик 3 имеет п разрядов, то работа делителя частоты продолжается согласно описанному до прихода m 2 входного импульса Момент приходат2 входного импульса соответствует высокому потенциалу на прямом выходе триггера 6, т.е. изменению состояния счетчика 3. Так как счетчик 3 к этому моменту находится в состоянии (2 -1),то т«2 импульс соответствует установке в нулевое состояние счетчика 3 и соответственно установке в единичное состояние триггера 5. На первом входе элемента 8 устанавливается высокий потенциал с выхода триггера 5, но на его выходе сигнал отсутствует, так как на третьем входе стоит низкий потенци ал с инверсного выхода триггера 6. По заднему фронту входного импульса на инверсном выходе триггера 6 и соответственно на третьем входе элемента 8 устанавливается высокий потенциал. По т(2 + 1) входному импульсу на выходе элемента 8 появляется сигнал, устанавливающий счетчик 3 по его счетному входу (t на фиг.2 в состояние (2 - 1), что соответст ет высоким потенциалам на выходах всех его п разрядов. Сигнал с входной шины 13 через элемент 8 проходит на счетный вход счетчика 3 (фиг.2г) до момента взв да триггера 6, т.е. до появления заднего фронта т(2 + 1)-1-го са (trj на фиг.2б). По следую1це 1у т(2 + 1)-му входному импульсу счет чик 3 и триггер 5 устанавливаются в нулевое состояние,а так как этот импульс является очередным m импульсом для делителя частоты на т то и счетчик 4 в этот же момент устанавливается в кулевое состояние по сигналу -с выхода элемента 11. По заднему фронту этого же импул са происходит сброс триггера 6 и, таким образом, делитель частоты приходит в исходное состояние. Дал цикл работы делителя частоты повторяется. Предлагаемый делитель позволяет получать на своих выходах частоты .в m (2 + l) меньше входной. Формула изобретения Делитель частоты следования импульсов, содержащий делитель частот на 1, включающий в себя счетчик импульсов, элемент совпадения и триггер, отличающийся гем, что, с целью повьшения быстро66действия при одновременном расширеши функциональных возможностей, в него введен делитель частоты на т, включающий в себя дополнительные элементы совпадения, дополнительный триггер, дешифратор, инвертор и дополнительный счетчик импульсов, раз-. рядные выходы которого соединены с группойовходов дешифратора, установочный вход - с выходом первого дополнительного элемента совпадения, счетный вход - с выходом второго дополнительного элемента совпадения первый вход которого соединен с первым входом элемента совпадения, входной шиной . счетным входом счетчика первым входом первого дополнительного элемента совпадения и входом инвертора выход которого соединен с управляющим входом дешифратора и первым входом третьего дополнительного элемента совпадения, второй вход которого подключен к выходу дешифратора и первому входу дополнительного триггера, второй вход которого соединен с выходом третьего дополнительного элемента совпадения, а прямой выход - со вторым входом первого дополнительного элемента совпадения, с управляющим входом счетчика импульсов и первым входом триггера, второй вход которого подключен к. выходу счетчика импульсов, а выход ко второму входу элемента совпадения, при этом инверсный выход дополнительного триггера соединен со вторым входом второго дополнительного элемента совпадения и третьим входом элемента совпадения, выход которого подключен к установочному входу счетчика импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 624371, кл. Н 03 К 23/00, 06.12.76. 2.Авторское свидетельство СССР № 455494, кл. Н 03 К 23/00,13.10.73.

9 (1)игЛ m.2 -1fn-2 fn{2 -H)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Устройство для измерения интервалов между центрами импульсов | 1980 |

|

SU938249A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU786010A1 |

| Измеритель временных интервалов | 1988 |

|

SU1672411A1 |

| Формирователь задержанных импульсов | 1980 |

|

SU924839A1 |

| Устройство для коррекции числа импульсов по входному параметру | 1984 |

|

SU1187146A2 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты | 1980 |

|

SU921095A1 |

| Цифровой фильтр | 1978 |

|

SU748803A1 |

Фиг.2

Авторы

Даты

1981-06-15—Публикация

1979-09-24—Подача