(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Делитель частоты следования импульсов | 1984 |

|

SU1181134A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1265996A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Делитель частоты импульсов | 1983 |

|

SU1162037A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Перестраиваемый делитель частоты | 1982 |

|

SU1023662A1 |

| Делитель частоты импульсов | 1977 |

|

SU675603A1 |

1

Изобретение относится к импульсной технике и может быть применено в устройствах вычислительной техники, синтезаторах частоты, в устройствах автоматики и телемеханики.

Известен делитель частоты следования импул сов, два дешифратора, триггер, блок управления и инвертор 1.

Недостаток устройства - невысокая надеж- : ность работы.

Наиболее близким по технической сущности к изобретению является делитель частоты следования импульсов, содержащий счетчик импульсов, счетный вход которого соединен с вход: ной пшяой, разрядные выходы которого соединены с первыми группами вход(Ж деОшфратора кода управления и деотфратора скважности, вторые группы входов которых соединены с разрядными выходами блока управления, элемент И-НЕ, триггер, первый вход которого со единен с выходом дешифратора кода управления, дополнительный дешифратор и инверторы 21/

Недостаток устройства - невысокая надежность работы.

Цель изобретения - повышение надежности работы.

Для достижения цели в делитель частоты следования импульсов, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, разрядные выходы которого , соединены с первыми группами входов дешифратора кода управления и дешифратора скважности, вторые группы входов которых соединены с разрядными выходами блока управлеtoния, элемент И-НЕ и триггер, первый вход которого соединен с выходом дешифратора кода управления, введены элемент запрета и элемент И, выход которого соединен с вторым входом триггера, первый вход - с выходом

ts дешифратора скважности, а второй вход - с выходом элемента И-НЕ, первый вход которого соединен с выходом младшего разряда блока управления, второй вход - со счетным входом счетчика импульсов и запрещающим

20 входом элемента запрета, управляющий вход которого соединен с первым входом триггера, а выход - с обнуляющим входом счетчика импульсов.

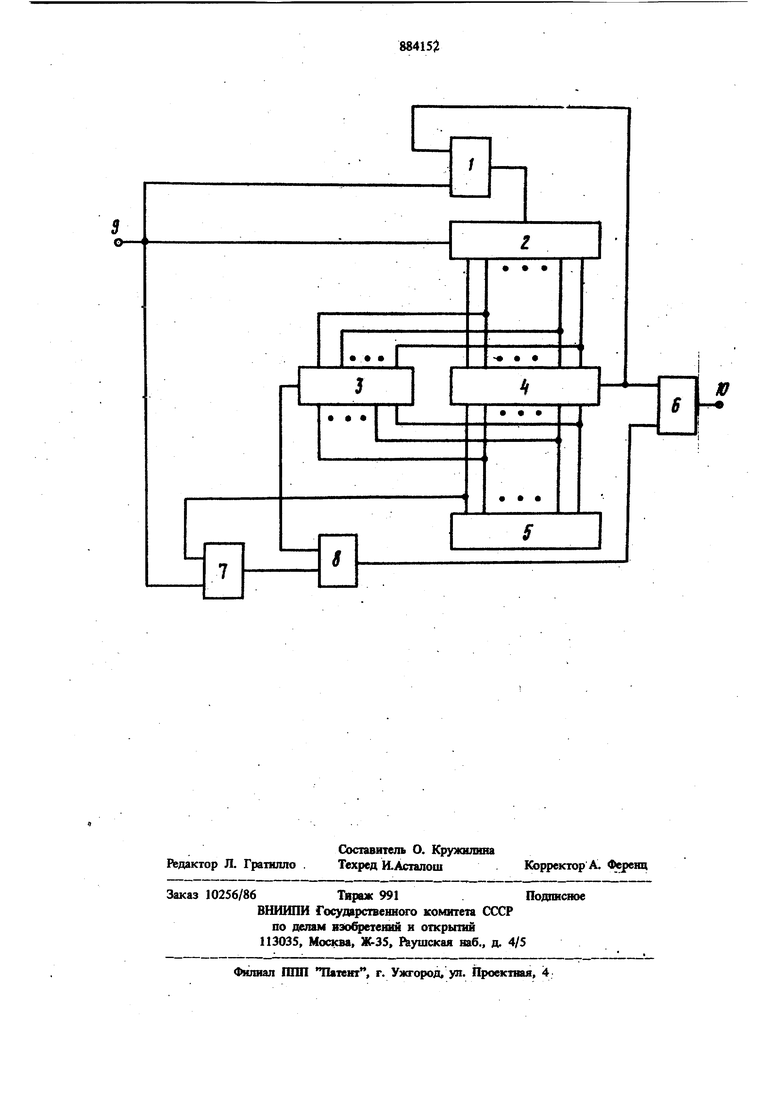

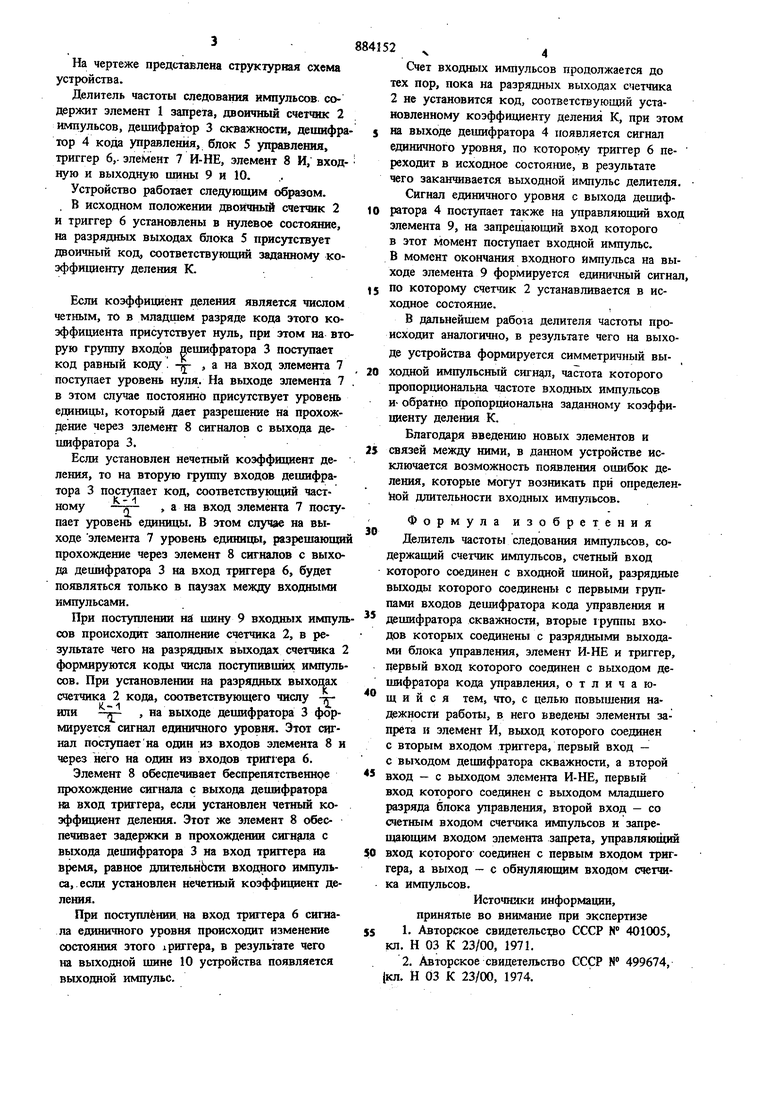

На чертеже представлена струк1урная схема устройства.

Делитель частоты следования импульсов содержит элемент 1 запрета, двоичный счетчик 2 импульсов, дешифратор 3 скважности, дешифратор 4 кода управления, блок 5 управления, триггер 6,- элемент 7 И-НЕ, элемент 8 И, входную и выходную шины 9 и 10.

Устройство работает следующим образом. , В исходном положении двоичный счетчик 2 и триггер 6 установлены в нулевое состояние, на разрядных выходах блока 5 присутствует двоичный код, соответствующий заданному коэффициенту деления К.

Если коэффициент деления является числом четным, то в младшем разряде кода этого коэффициента присутствует нуль, при этом на вторую группу входов дешифратора 3 поступает код равный коду . - , а на вход элемента 7 поступает зфовень нуля. На выходе элемента 7 в этом случае постоянно присутствует уровень единицы, который дает разрешение на прохождение через элемент 8 сигналов с выхода дешифратора 3.

Если установлен нечетный коэффициент деления, то на вторую группу входов дешифратора 3 поступает код, соответствующий частному п , а на вход элемента 7 поступает уровень еданицы, В этом случае на выходе элемента 7 уровень единицы, разрешающи прохождение через элемент 8 сигналов с выхода дешифратора 3 на вход триггера 6, будет появляться только в паузах между входными импульсами.

При поступления ни шину 9 входных импулсов происходит заполнение счетчика 2, в результате чего на разрядных выходах счетчика 2 формируются коды числа поступивш1ос импульсов. При установлении на разрядных выходах счетчика 2 кода, соответствующего числу , на выходе дешифратора 3

форили пт . на выходе дешифратора

Этот cjp-мируется сигнал единичного уровня, нал поступает на один из входов элемента 8 и через него на один из входов триг1ера 6.

Элемент 8 обеспечивает беспрепятственное прохождение сигнала с выхода дешифратора ш вход триггера, если установлен четный коэффициент деления. Этот же элемент 8 обеспечивает задержки в прохождении сигнала с выхода дешифратора 3 на вход триггера на время, равное длительнЬсти входного импульса, если установлен нечетный коэффициент деления.

При поступлении на вход триггера 6 сигнала единичного уровня происходит изменение состояния этого григгера, в результате чего на выходной шине 10 устройства появляется выходной импульс.

Счет входных импульсов продолжается до тех пор, пока на разрядных выходах счетчика 2 не установится код, соответствующий установленному коэффициенту деления К, при этом

на выходе дешифратора 4 появляется сигнал единичного уровня, по которому триггер 6 переходит в исходное состоя1ше, в результате чего заканчивается выходной импульс делителя. Сигнал единичного уровня с выхода дешифратора 4 поступает также на управляющнй вход элемента 9, на запрешающий вход которого в этот момент поступает входной импульс. В момент окончания входного импульса на выходе элемента 9 формируется единичный сигнал,

5 по которому счетчик 2 устанавливается в исходное состояние.,

В дальнейшем работа делителя частоты происходит аналогично, в результате чего на выходе устройства формируется симметричный вы0 ходной импульсный сигнал, частота которого пропорциональна частоте входных импульсов и- обратно пропорциональна заданному коэффициенту деления К.

Благодаря введению новых элементов и

связей между ними, в данном устройстве исключается возможность появления ошибок деления, которые могут возникать при определен1ной длительности входных импульсов.

Формула изобретения Делитель частоты следования импульсов, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, разрядные выходы которого соединены с первыми группами входов дешифратора кода управления и дешифратора скважности, вторые 1руппы входов которых соединены с разрядными выходами блока управления, элемент И-НЕ и триггер, первый вход которого соединен с выходом дешифратора кода управления, отличающийся тем, что, с целью повышения надежности работы, в него введены элементы запрета и элемент И, выход которого соединен с вторым входом триггера, первый вход - с выходом дешифратора скважности, а второй вход - с выходом элемента И-НЕ, первый вход которого соединен с выходом младшего разряда блока управления, второй вход - со счетным входом счетчика импульсов и запрещающим входом элемента запрета, управляюиош

0 вход которого соединен с первым входом триггера, а выход - с обнуляющим входом счетчика импульсов.

Источники информации, принятые во внимание при экспертизе

5 1. Авторское свидетельс-цво СССР № 401005, ют. Н 03 К 23/00, 1971.

-

ю

Авторы

Даты

1981-11-23—Публикация

1980-03-31—Подача