1

Изобретение относится к области вычислительной техники и может быть использовано для решения задач статистического моделирования.

Известны датчики аналогичного назначения, содержащие сдвиговый регистр с линейной обратной СВЯЗЬЮ, тактовый генератор, логические схемы и блок рандомизации (в виде генератора случайных временных задержек или управляемого генератора обобщенного телеграфного сигнала).

Недостатком известных датчиков является то, что ВЫХОД из строя одного разряда сдвигового регистра выводит из строя все устройство.

Целью изобретения является повыщение надежности датчика.

Поставленная цель достигается тем, что датчик содержит М каскадов, каждый из которых содержит 2™ счетных ячеек (т - номер каскада), а каждая ячейка содержит два элемента задержки, триггер, входы которого подключены к выходам элементов задержки соответственно, четыре элемента «И, первые ВХОДЫ которых соединены с выходом тактового генератора, вторые - с выходами триггера соответственно, а третьи - с выходами триггера предыдущего каскада соответственно. Выходы двух элементов «ИЛИ подключены ко входам элементов задержки соседнего каскада соответственно. Входы первого элемента «ИЛИ подсоединены к выходам первого и второго элементов «И, третьи входы элементов «И первого каскада соединены с выходами рандомизирующего триггера соответственно.

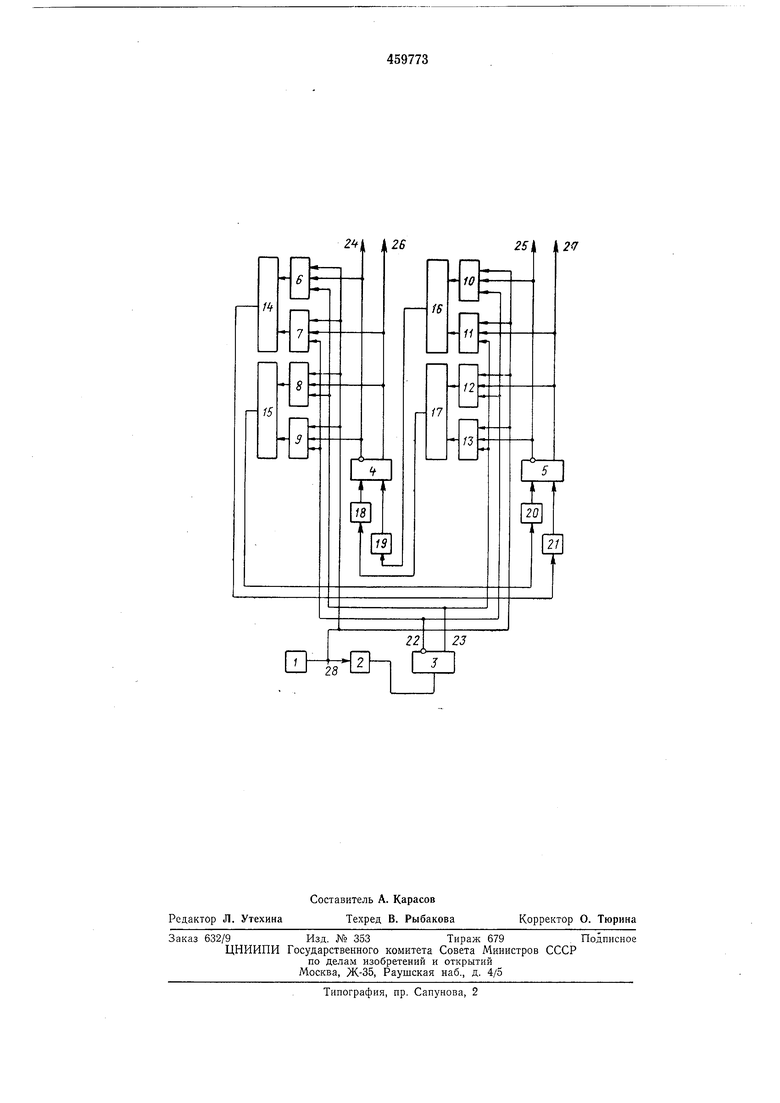

Схема двухуровнего варианта устройства изображена на чертеже.

Генератор 1 тактирует работу всех узлов

датчика случайных кодов. Блок рандомизации представляет собой последовательно соединенные датчик случайной тактированной последовательности импульсов 2 и задающий триггер 3. Узлы 2 и 3 являются первым уровнем пирамидальной структуры и предназначены для генерации случайных двоичных цифр. Прямой и инверсный выходы триггера 3, ВЫХОД тактового генератора 1 и прямые и инверсные ВЫХОДЫ триггеров 4 и 5 подключены

к элементам «И 6-13, которые че|рез элементы «ИЛИ 14-17 и линии задержки 18-21 соединены с единичными и нулевыми входами триггеров 4 и 5 двухразрядного кольцевого СДВИГОВОГО регистра второго уровня. Межразрядная логика регистра второго уровня синтезирована так, что при единичном состоянии триггера 3 информация триггера 5 копируется В триггер 4 и информация триггера 4 передается в триггер 5 с инверсией, а при

нулевом состоянии триггера 3 наоборот: информация триггера 5 передается в триггер 4 с инверсией и информация триггера 4 копируется в триггер 5 без изменений.

Триггеры 4 и 5 выполняют роль рандомизатороБ для регистров следующего, третьего уровня аналогично тому, как триггер 3 выполняет роль рандомизатора по отношению к узлам второго уровня (т. е. пара сигналов 22- 23 аналогична функционально парам 24-25 и 26-27).

Датчик работает следующим образом.

По сигналу 28 с выхода генератора 1 опрашивается датчик 2, на выходе которого формируется тактированная случайная последовательность импульсов, поступающая на счетный вход триггера 3.

Предположим, что триггеры 4, 5, 3 - в нулевом состоянии, а по сигналу 28 узел 2 не выдал импульса переброса. В такой ситуации по сигналу 28 в триггер 4 через элемент «И 10, элемент «ИЛИ 16 и линию задержки 19 записывается единица, а в триггер 5 через элемент «И 9, элемент «ИЛИ 15 и линию задержки 20 копируется нуль. Таким образом, из комбинации 00 получилась комбинация 10.

Пусть по-прежнему с приходом следующего по очереди сигнала 28 триггер 3 сохраняет нулевое состояние. Комбинация 10 в триггерах

4и 5 трансформируется в комбинацию 11 (через узлы 10, 16, 19 в триггер 4 записывается единица, а через узлы 7, 14 и 21 в триггер

5копируется единица из триггера 4). Нетрудно убедиться, что при нулевом состоянии триггера 3 на шинах 25-27 и 26-24 по сигналам 28 генерируется периодическая последовательность двухразрядных двоичных чисел 00, 10, 11, 01, 00... щ их инверсий, а при единичном состоянии триггера 3 периодическая последовательность 00, 01, 11, 10, 00... и их инверсий. Естественно, блок рандомизации (узлы 2 и 3) превращает описанные последовательности в апериодические случайные.

Двухуровневый вариант пирамидальной структуры датчика случайных кодов позволяет генерировать числа разрядностью до трех (триггеры 4, 5, 3), трехуровневый вариант - разрядностью до семи, четырехуровневый вариант - разрядностью до пятнадцати и т. д.

Выход из строя одного из разрядов регистра любого уровня в пирамидальной структуре вызывает искажение статистических свойств генерируемых кодов всего лишь в одном разряде (если вышедший из строя разряд используется как выходной элемент всего устройства).

В самом деле, если в трехуровневом варианте датчика вышел из строя узел 19 (т. е. триггер 4 всегда в нулевом состоянии), то в левых двух разрядах третьего уровня генерируется псевдослучайная периодическая последовательность 00, 10, 11, 01, 00, ..., рандомизируемая двумя правыми разрядами третьего уровня (пара шин 24-26 подключена к левым двум разрядам третьего уровня, а пара 25-27 - к правым двум). В описываемой пирамидальной структуре датчика случайных

кодов предлагается смешанное подключение второго уровня к третьему, третьего к четвертому и т. д., т. е. прямые выходы триггеров предшествующего уровня подключаются к одним (одному) регистрам следующего уровня,

а инверсные выходы - к другим (другому). В описанном случае (вышел из строя узел 19) все четыре разряда третьего уровня рандомизируются триггером 5.

Предмет изобретения

Датчик случайных кодов, содержаший тактовый генератор, генератор, генератор случайных сигналов, вход которого подключен к выходу тактового генератора, задающий триггер,

счетный вход которого соединен с выходом генератора случайных сигналов, отличающийся тем, что, с целью повышения надежности датчик содержит М каскадов, каждый из которых содержит 2 счетных ячеек (т-

номер каскада), а каждая ячейка содержит два элемента задержки, триггер, входы которого подключены к выходам элементов задержки соответственно, четыре элемента «И, первые входы которых соединены с выходом

тактового генератора, вторые - с выходами триггера соответственно, а третьи - с выходами триггера предыдущего каскада соответственно, два элемента «ИЛИ, выходы которых подключены ко входам элементов задержки соседнего каскада соответственно, входы первого элемента «ИЛИ соединены с выходами первого и второго элементов «И, входы второго элемента «ИЛИ соединены с выходами третьего и четвертого элементов

«И, третьи входы элементов «И первого каскада соединены с выходами задающего триггера соответственно.

ггич

I-I 28

.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Цифровой оптический уровнемер | 1988 |

|

SU1624262A1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| Устройство для контроля генератора случайных чисел | 1983 |

|

SU1088011A1 |

| Имитатор многомерных случайных величин | 1979 |

|

SU857978A1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| Преобразователь моментов времени в код | 1986 |

|

SU1370644A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ | 2021 |

|

RU2780985C1 |

| Устройство для сопряжения с двухпроводной линией связи трактов приема и передачи | 1987 |

|

SU1462390A1 |

| Генератор случайной последовательности | 1981 |

|

SU962933A1 |

Авторы

Даты

1975-02-05—Публикация

1973-05-03—Подача