(54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ДИСКРЕТНОГО ..РАДИОКАНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Генератор квазирегулярных последовательностей импульсов | 1981 |

|

SU991589A2 |

| Генератор квазирегулярных последовательностей импульсов | 1979 |

|

SU866717A1 |

| Генератор псевдослучайной последовательности импульсов | 1979 |

|

SU866716A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

1

Изобретение относится к аппаратурным средствам электронного модепирования дискретных радиоканалов связи и может быть использовано для решения задач исследования помехоустойчивости и повышения достоварности приема дискретной информации, а также при лабораторных испытаниях каналообразующей аппаратуры в условиях, приближающихся к реальным.

Известен имитатор искажений двоим- Q .ных сигналов, содержащий источник двоич ных сигналов, приемный сдвиговый регистр, синхронизатор, схему управления формированием пакета, схему управления регис:тром уровня искажений, счетчик-ре- , гистр длины пакета, коммутатор, регистр уровня искажений, логические схемы, датчик случайных чисел, приемник двоичных сигналов, схему формирования потока ис кажений ij.20

Данное устрьйство позволяет имитировать поток ошибок при приеме двоичного сигнала путем наложения на исходный сигнал импульсов с формирователя потока

искажений, управгоемого датчиком случайных чисел. Использование в данном имитаторе дискретных элементов позволяет достигать хорошую воспроизводимость результатов статических испытаний и независимость их от внешних условий. Однако функции данного имитатора ограничены, так как он не позволяет модели- ровать такие вторичные характеристики дискретных сигналов на приемном конце как временные искажения фронтов эпементарных посыпок.

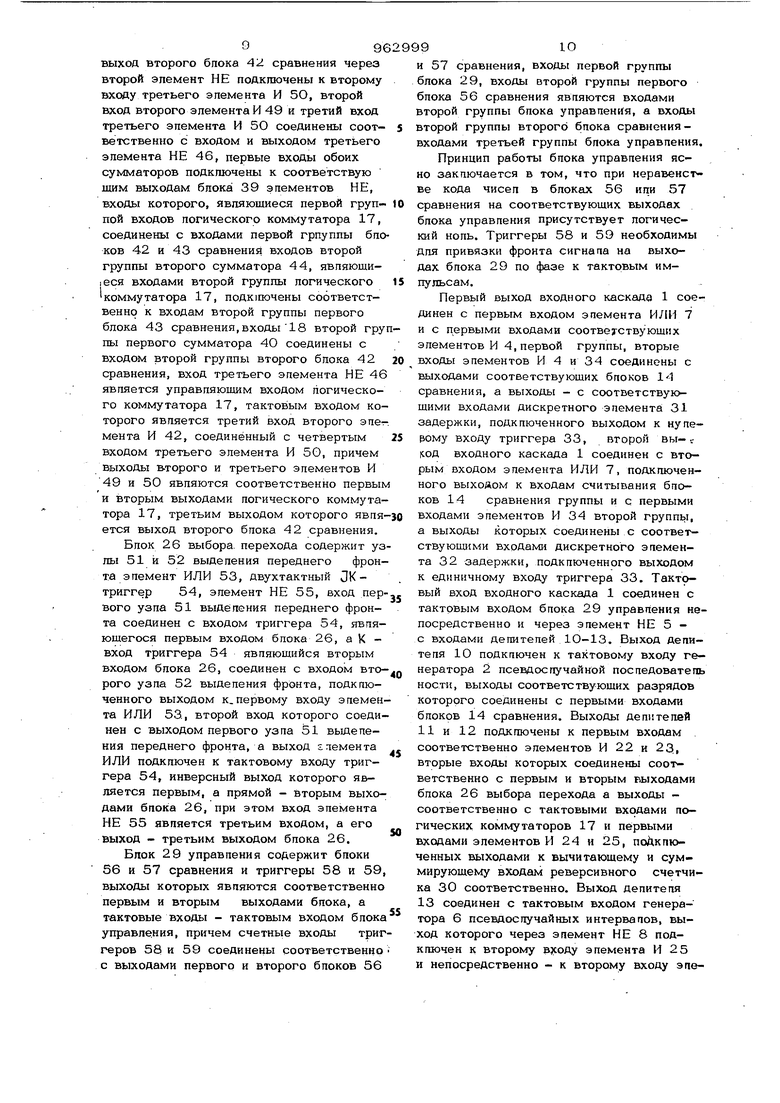

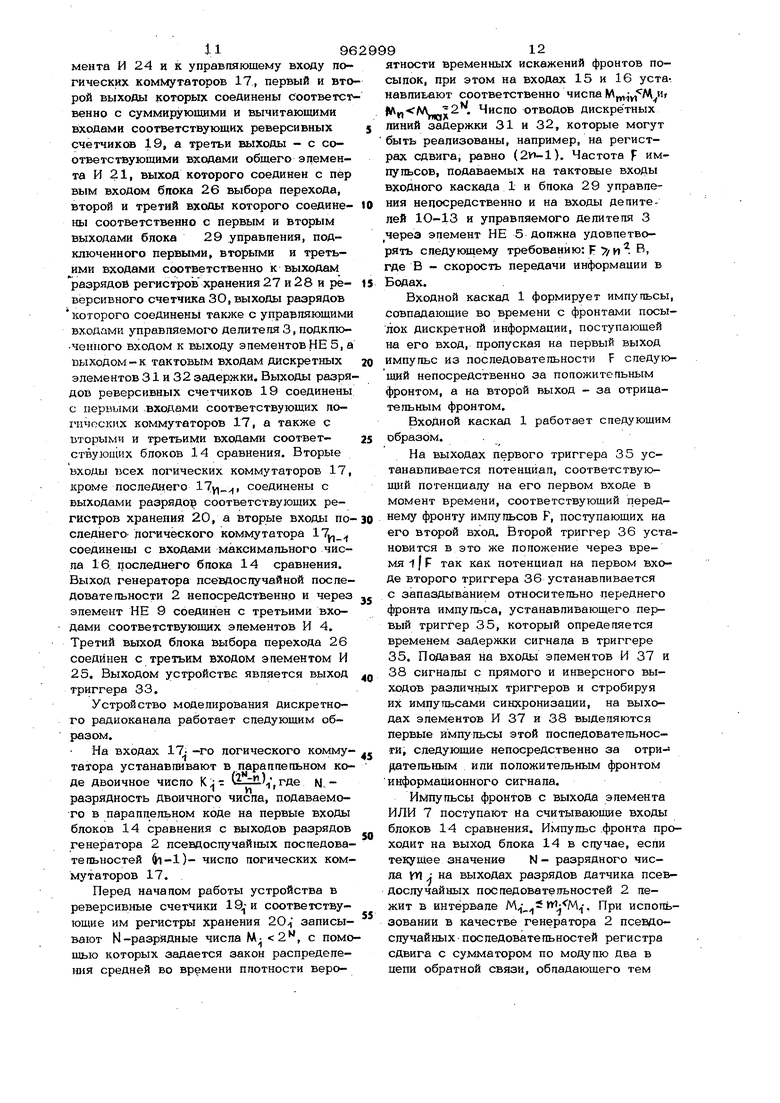

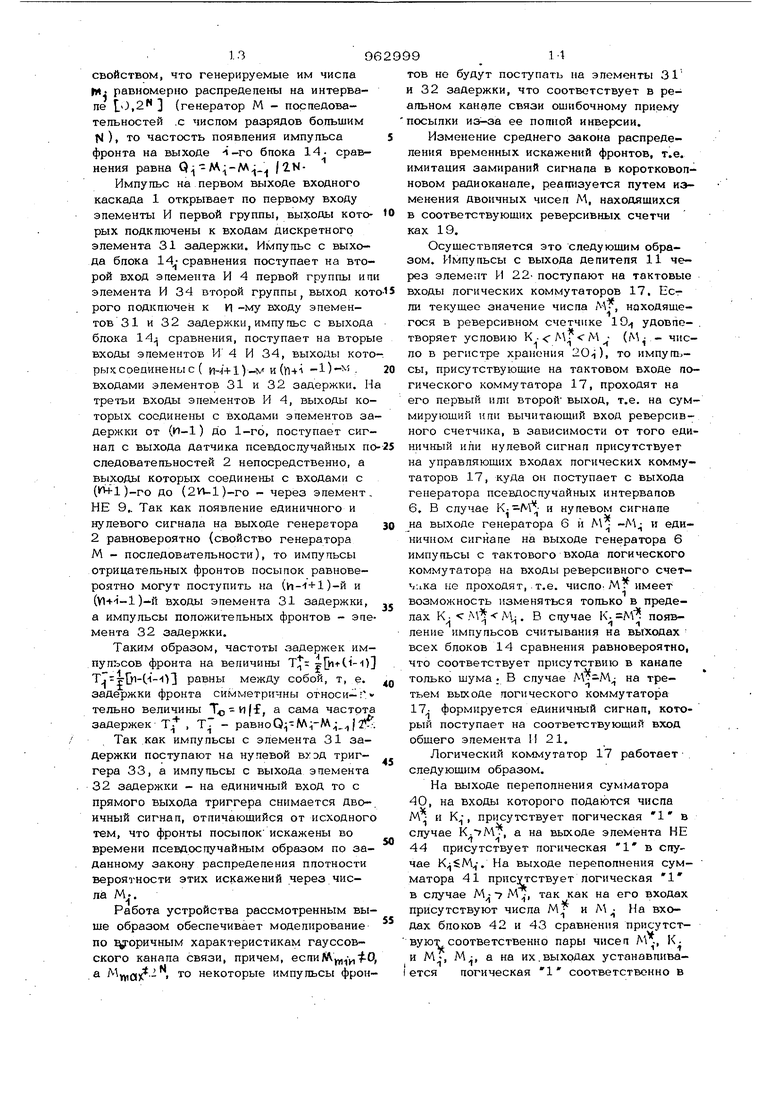

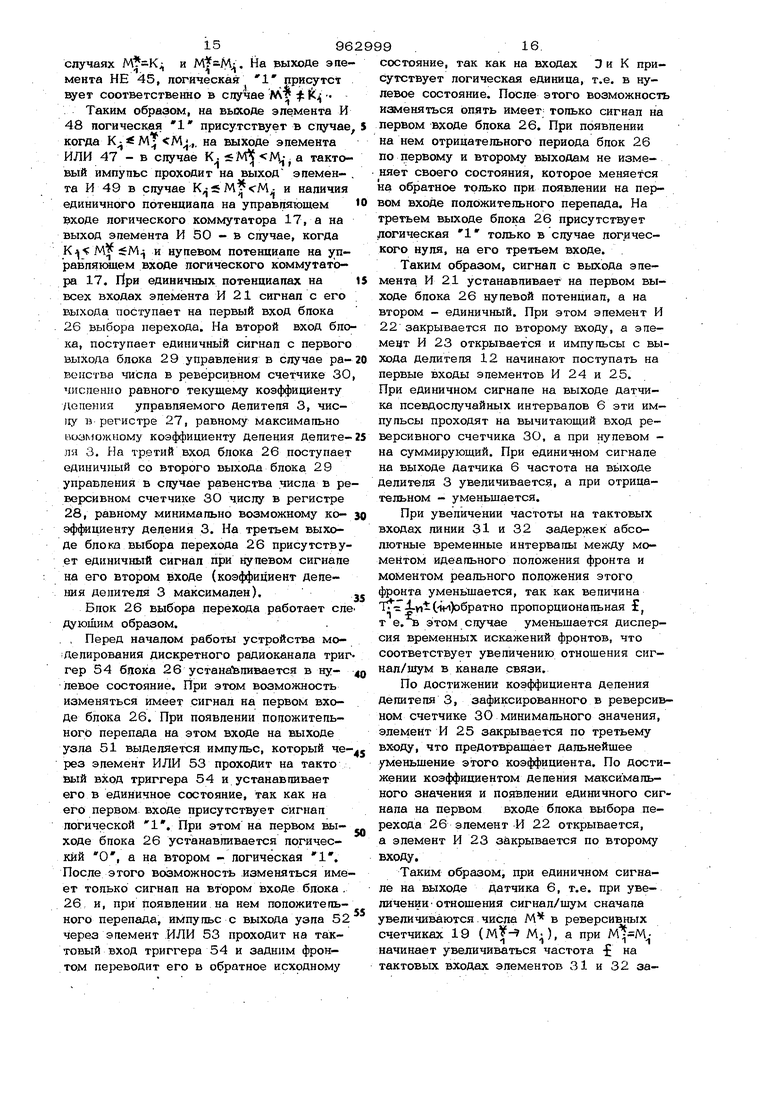

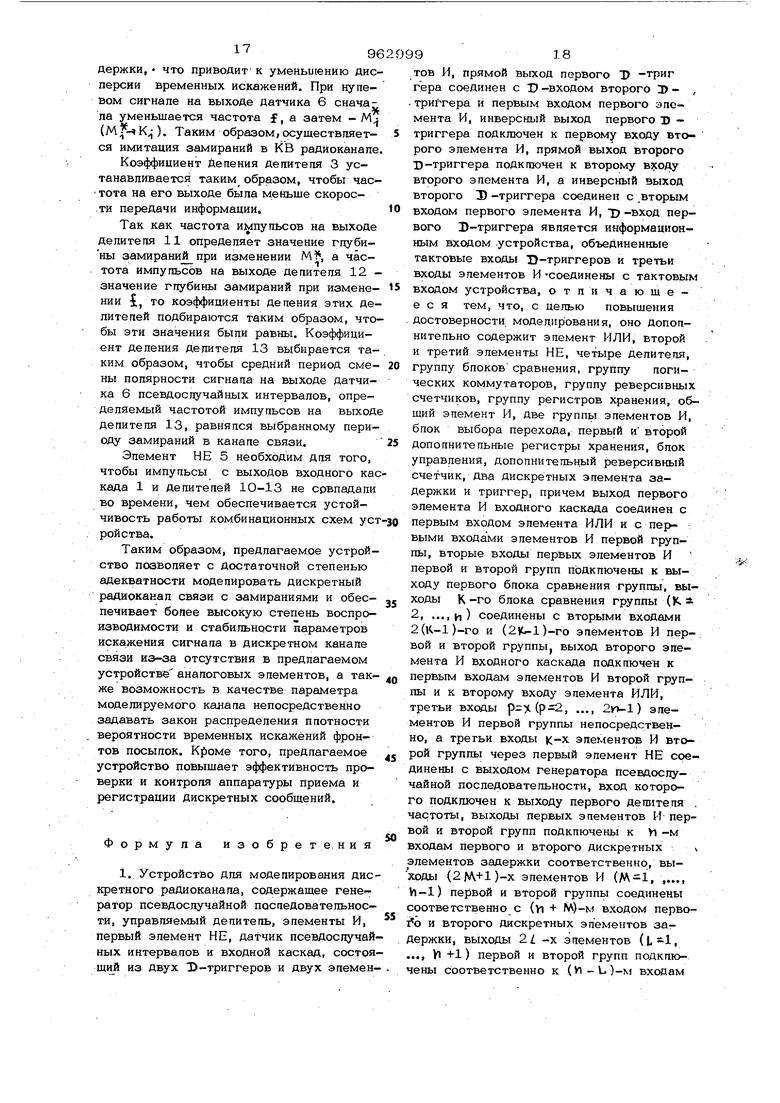

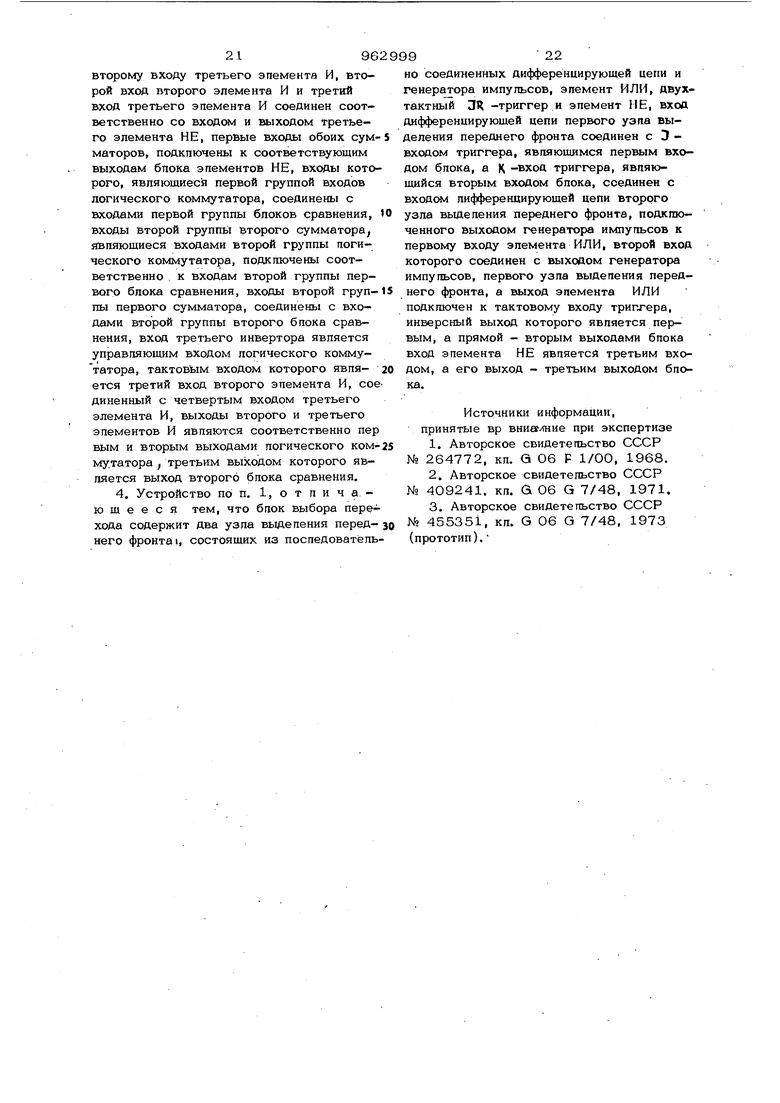

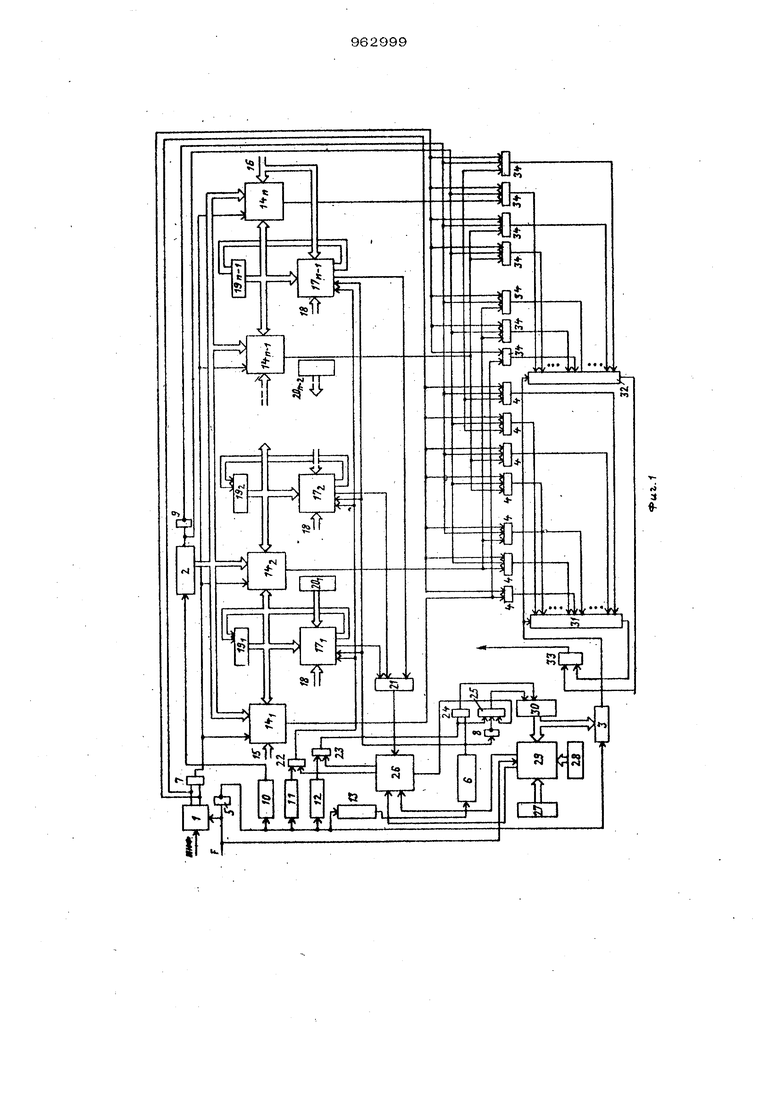

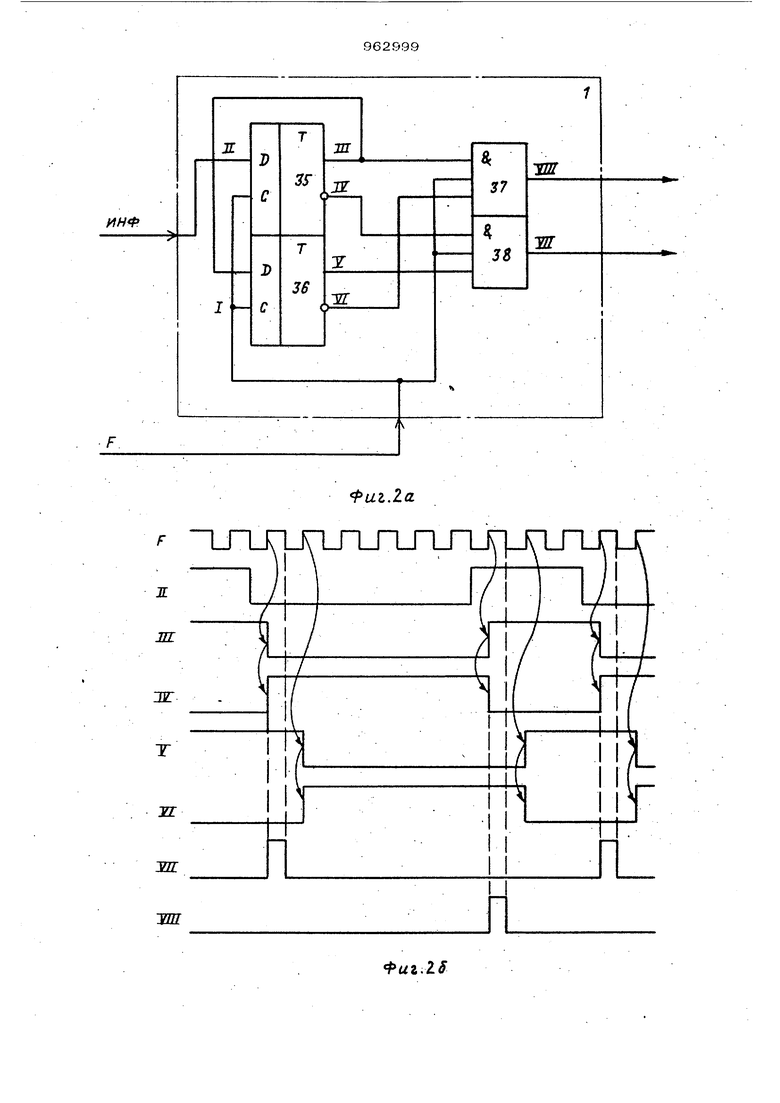

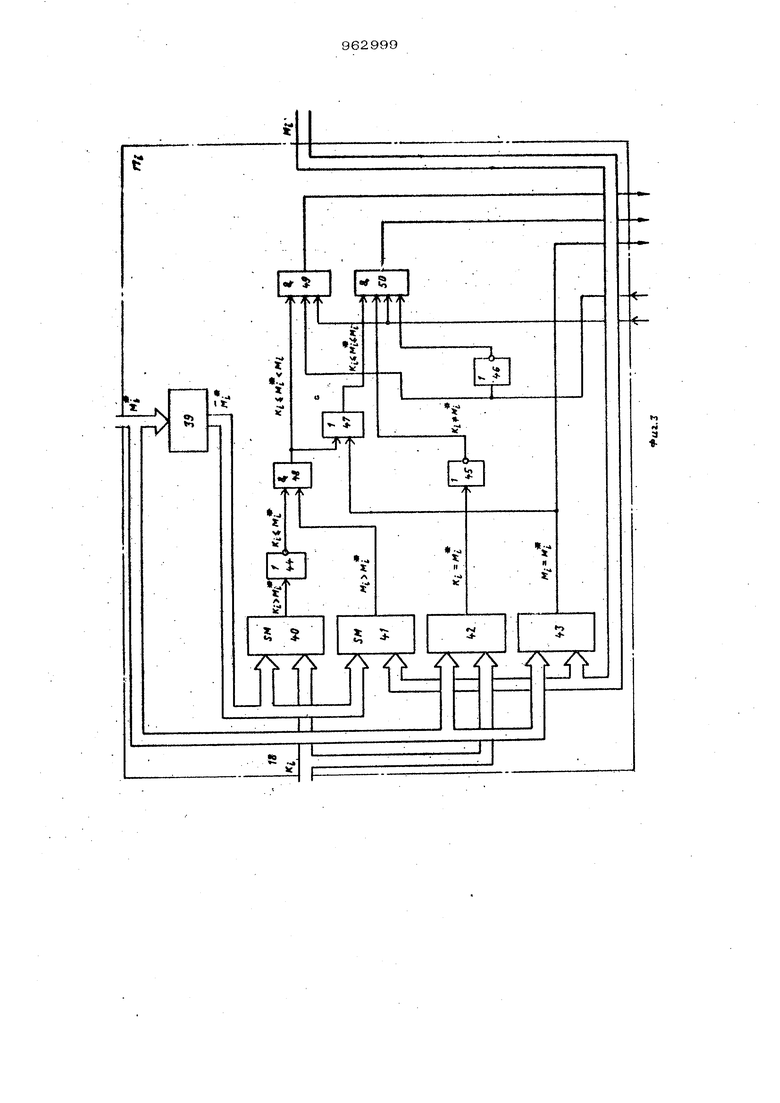

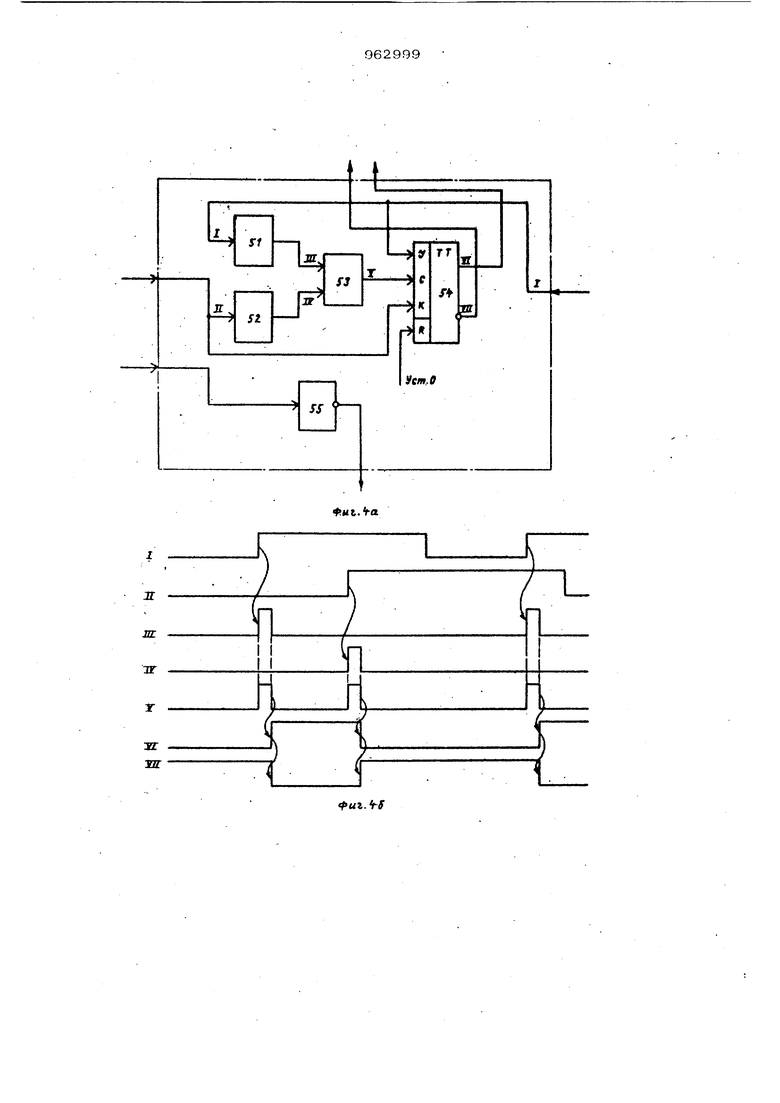

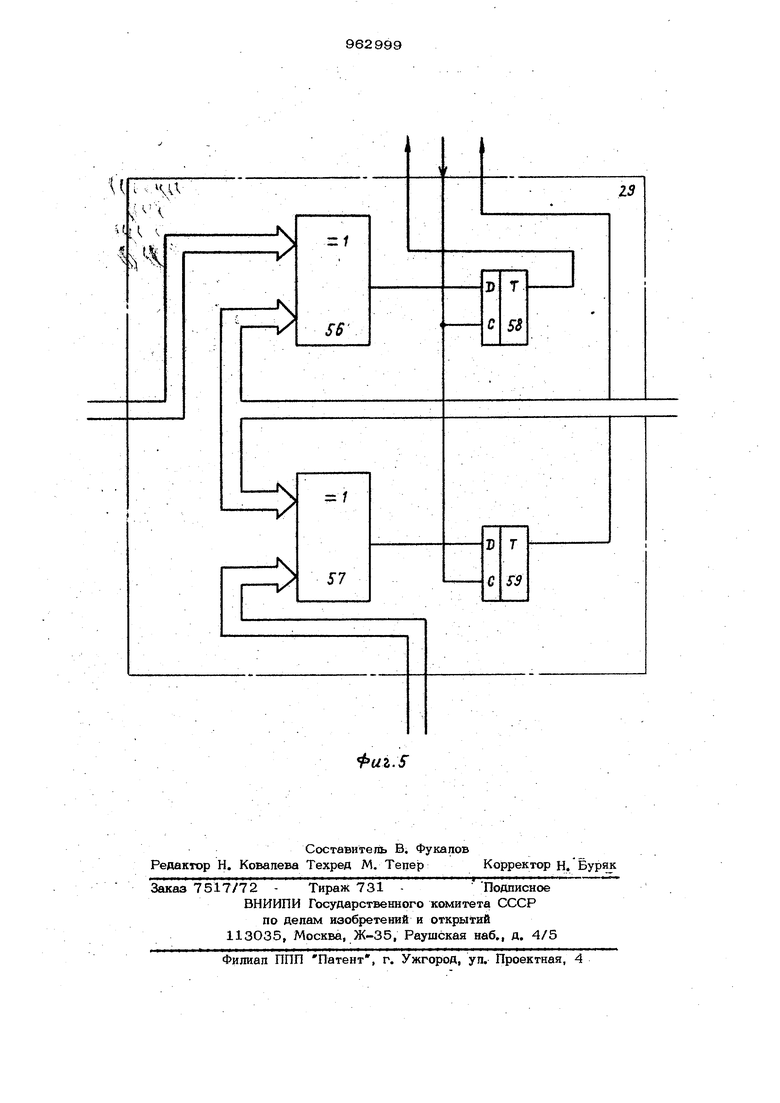

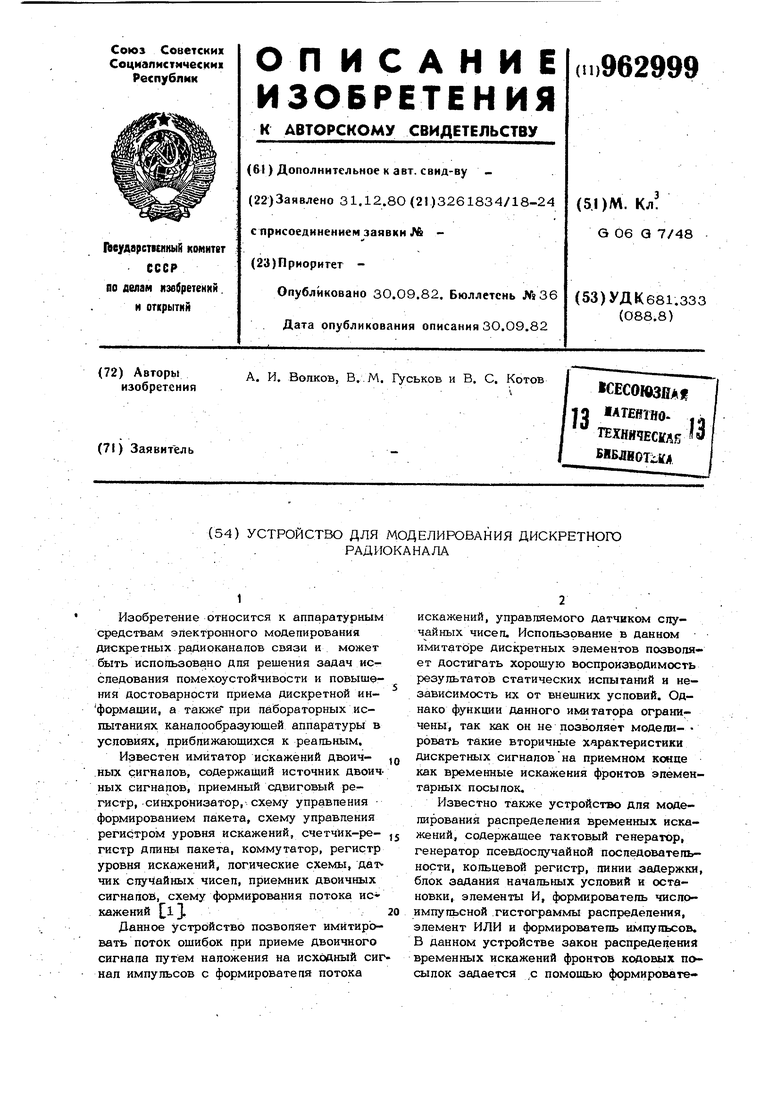

Известно также устройство для моделирования распределения временных искажений, содержащее тактовый генератор, генератор псевдослучайной последовательности, кольцевой регистр, линии задержки, блок задания начальных условий и остановки, элементы И, формирователь числоимпульсной .гистограммы распределения, элемент ИЛИ и формирователь импульсов. В данном устройстве закон распределения временных искажений фронтов кодовых посылок задается с помощью формировате3.96 ля чисво-импупъсной гистограммы, сигна пы с выхода которого через элементы И, ИЛИ и линии задержки объединяются с пседюсдучайной последовательностью импупьсов, из которых затем формируются выходные импульсы. Таким образом, псев дослучайное временное искажение фронта кодовой посылки в текущий момент времени формируется путем задержки этого фронта на величину, задаваемую с помощью датчика JIceвдослучайных последовательностей. Однако данное устройство позволяет моделировать временные искажения фронтов не произвольного дискретного сигнала, а только стандарнтых импупьсов с длительностью равной длительностн элементарной посылки. Кроме того отсутствует возможность изменения закона распределения временных искажений фронтов в процессе моделирования, т.е. ими тащ1и замираний в радиоканале 11, Наиболее близким к предлагаемому яв ляе1х;я устройство для моделирования тракта передачи цифровых сигналов, содержащее генератор псевдослучайных последоватепьностей, блоки формирования щумовых напряжений, блок фазоимпульс- ной модуляции, входной каскад, схему сч тывания, буферный накопитель, блок добавления-исключения импульсов, эпементы И, блок формирования скорости подстройки, генератор сетки частот, элемент НЕ, датчик псевдослучайных интерваловЕз Йзвестное устройство формирует Дискретный сигнал, в котором помимо искажений переднего и заднего фронтов присутствует характерное для радиоканалов качания групп фронтов посылок,, имеющие место из-за изменения времени распространения сигнала в канале связи-замирании.. Однако в известном устройстве те кущее значение .искажения фронтов задается с помощью блоков щумовых напряжений, формирующих аналоговый сигнал. что снижает стабильность моделируемых статистических параметров и, как следст вие( воспроизводимость результатов мо делирования. Кроме того, в известном устройстве отсутствует возможность непосредственного задания плотности вероятности распределения временных искаже ний фронтов, что сужает класс задач, рещаемых с помощью данного устройства. Цель изобретения - повыщение достоверности моделирования. Поставленная цель достигается тем, что в устройство для моделирования дискретного радиоканала, содержащее генератор псевдослучайной последовательнос94ти, . управляемый делитель, элементы И, элемент НЕ, датчик псевдослучайных интервалов и входной каскад, состоящий из двух 1)-триггеров, двух элементов И,прямой выход первого Р-триггера соединен с Т)-входом второго . D-триггера и первым входом первого элемента И, инверсиый выход первого р-триггера подключен к первому входу второго элемента И, прямой выход второго D -триггера подключен к втopo Iy входу второго элемента И, а инверсный выход второго U триггера соединен с вторым входом первого элемента И, вход первого D-триг Р является информационным входом устройства, объединенные тактовые входы D-триггеров и третьи входы элементов И соединены с тактовым входом устройства, дополнительно введены элемент « третий элементы, НЕ , Делителя, группу блоков сравнения, группу логических коммутаторов, группу реверсивных счетчиков, группу регистров хранения, общий элемент И, две группы элементов И, блок выбора перехода, первый и второй дополнительные регистры хранения, блок управления, дополнительный реверсивный счетчик, два дискретных элемента задержки и триггер, причем выход первого элемента И входного каскада соединен с первым входом элемента илИ и с первыми входами элементов И первой группы, вторые входы первых элементов И первой и второй группы подкпючены к выходу первого блока сравнения группы выходы К -го блока сравнения группы (К.-2,..., VI ) соединены с вторыми входами 2(К-1)-го и (2К-1)-го элементов И первой и второй, групп, выход второго элемента И входного каска- да подключен к первым входам элементов И второй группы и к второму входу элемента ИЛИ, третьи входы р -х (у-2, ..., 2у1г1) элементов И первой группы непосредственно, а третьи входы к -х элементов И второй группы 1ерез первый элемент ЙЕ соединенны с выходом генератора псевдослучайной последовательности, вход которого подключен к выходу первого делителя частоты, выходы первых элементов И первой и второй групп подключены к И-м.входам первого и второго дискретных элементов задержки соответственно, выходы (2М+1) элементов И , ..., и-1) первой и второй группы . . соединены соответственно с (И+М)-м вхсдом первого и второго дискретных элементов задержки, выходы 21-к элементов И (, ..., VI 1) первой и второй групп подключены соответсвенно к ()-м Входам первого и второго чискретных эле ментов задержки, тактовые входы которы соединены с выходом управляемого делите пя часюты, выходы первого и второго дискретных элементов задержки подключены к нулевому и единичному входам триггера, единичный выход которого является выходом устройства, выход элемента ИЛИ соединен с входами считывания блоков сравнения группы, входы первой группы входов которых подкшочены к разрядным выходам генератора псевдослучайной последовательности, входы второй группы входов первого и последнего блоков сравнения группы соединены с входами минимального и максимального чиспа первого и последнего логических коммутаторов группы соответственно, груп па выходов j-ro реверсивного счетчика группы (j 1, ..., И+1) подключена к входам второй группы j -го блока сравнения группы, к входам первой группы (j+l)-ro блока сравнения группы и к вхо дам первой группы входов логических ком мутаторов группы, входы второй группы i -X логических коммутаторов группы (i 1, ,.,, и-2) соединены с выходами соот ветствующего регистра хранения группы, входы третьей группы логических коммутаторов группы подкшочены соответственно к входам констант устройства,: тактовые входы логических коммутаторов группы соединены с выходом первого элемента И, первый вход которого подключен к выходу второго делителя частоты, а второй вход - к первому выходу блока выбора перехода, управляющие входы логических коммутаторов группы соединены с выходом датчика псевдослучайных интервалов, первым входом второго элемента И, входом Второго элемента НЕ, первый выход логических коммутаторов группы соединен с суммирующим входом соответствующего реверсивного счетчика группы, а второй выход - с его вычитающим входом, третьи выходы логических коммутаторов подключены соответственно к входам общего элемента И, выход которого соединен с первым входом блока выбора перехода,второй и третий входы которого под ключены соответственно к первому и второму выходам блока управления, тактовый вход которого соединен с тактовым входом устройства непосредственно, а через второй элемент НЕ - с входами четы рех Делителей частоты и входом управляемого делителя частоты, группа управляющих входов которого подключена к разрядным выходам реверсивного счетчика и К входам первой группы входов блока управления, входы второй группы которого соединены с разрядными выходами первого Дополнительного регистра хранения, а входы третьей группы блока управления подключены соответственно к разрядным выходам второго дополнительного регистра хранения, выход первого Дего1теая частоты соединен с входом генератора псевдослучайной последовательности, выход третьего делителя частоты подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом блока выбора переключения, а выход - с вторым входом второго элемента И и с первым входом четвертого элемента И, второй вход которого подключен к выходу третьего элемента НЕ, третий вход четвертого элемента И соединен с третьим выходом блока выбора перехода, -суммирующий вход дополнительного реверсивного счетчика подключен к выходу второго элемента И, а вычитающий вход - к выходу четвертого элемента И, выход четвертого делителя частоты соединен с входом датчика псевдослучайных интервалов. Причем блок управления содержит два блока сравнения и два триггера, выходы которых являются соответственно первым и вторым выходами блока, а тактовые входы - тактовым входом блока управления, причем счетные входы триггеров соединены соответственно с выходами первого н второго блоков сравнения,входы первой группы которых являются вххз- дамп первой группы блока управления, а входы второй группы первого блока сравнения являются входами второй группьт блока управления, входы второй группы второго блока сравнения - входа1 1и третьей группы блока управления. Кроме того, логический коммутатор содержит блок элементов НЕ, два сумматора, два блока сравнения, три элемента НЕ, элемент ИЛИ, три элемента И, выход переполнения первого сумматора через первый элемент НЕ, а выход переполнения второго сумматора непосредственно соединены соответственно с первым и вторым входами первого элемента И, выход которого подключен к первым входам второго элемента И и элемента ИЛИ, второй вход которого соединен с Выходом первого блока сравнения, а выход - с первым входом третьего элемента И, выход второго блока сравнения через второй элемент НЕ подключен к второму входу третьего элемента И, второй вход второго эпемента И и третий вход третьего элемента И соединены соответственно с входом и выходом третьего элемента НЕ, первые входы обоих сумматоров . подключены к соответствующим выходам блока элементов НЕ, входы которого являющиеся первой группой входов логического коммутатора, соединены с входа ми первой группы блоков сравнения, входы второй группы второго сумматора, яв дающиеся входами второй группы логического коммутатора подключены соот; ветственно к входам второй группы первого сумматора, соединены с . входами второй группы второго блока сравнения, вход третьего элемента НЕ является управгюющим входом логического коммутатора, тактовым входом которого является третий вход второго элемента И, соединенный с четвертым входом третьего элемента И, выходы второго и третьего элементов И являются соответственно первым и вторым выходами логического коммутатора, третьим выходом которого является вы Ход второго блока сравнения. Блок выбора перехода содержит два узла выделения переднего фронта, состоящих из последовательно соединенных дифференцирующей цепи и генератора импуль сов, элемент ИЛИ, двухтактный DR -тр гер и элемент НЕ, вход дифференцирующей цепи первого узла выделения переднего фронта соединен с 3 -входом триггера, являющимся первым входом блока, а R -вход триггера, являющийся вторым входом блока, соединёнс входом дифференцирующей цепи второго узла выделения переднего фронта, подключенного вы-i ходом генератора импульсов к первому входу элемента ИЛИ, второй вход которого соединен с выходом генератора импуль сов первого узла выделения переднего фронта, а выход элемента ИЛИ подкшочен к тактовому входу триггера, инверсный выход которого является первым, а прямой - вторым выходами блока, вход элемента НЕ является третьим входом, а его выход - третьим выходом блока. I На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2,а функциональная схема входного каскада; на фиг. 2,6 - временные диаграммы, иллюстрирующие его работу; на фиг. 3 функциональная схема логического коммутатора; на фиг, 4,а - функциональная схема блокавыбора перехода; на фиг.4,6временные диаграммы его работы; на фиг. 5 - функциональная схема блока управления. Устройство содержит входной каскад 1, генератор 2 псевдослучайной последовательности, управляемый делитель 3, первую группу элементов И 4, первый элемент НЕ 5, датчик 6 псевдослучайных интервалов, элемент ИЛИ 7, второй и третий элементы НЕ 8 и 9, четыре делителя 1О-13, группу блоков 14 сравнения, первый 14 и последний 14 из которых имеют соответственно входы минимального is и максимального 16 чисел, группу логических коммутаторов 17 с входами констант 18, группу реверсивных счетчиков 19, группу регистров 2О хранения, общий эпемент И 21, четыре элемента И 22-25, блок 26 выбора перехода, первый и второй дополнительные регистры 27 и 28 хранения, блок 29 управления, реверсивный счетчик 30, дискретные элементы 31 и 32 задержки, триггер 33 и вторую группу элементов И 34. Входной каскад 1 содержит два D триггера 35 и 36 и два элемента И 37 и 38, причем прямой выход первого триггера 35 соединен с D-входом второго триггера 36 и первым входом первого элемента И 37, инверсный выход триггера 35 соединен с первым входом второго элемента И 38, прямой выход второго триггера 36 подключен к второму входу второго элемента И 38, а инверсный выход второго триггера 36.соединен с вторым входом первого элемента И 37, Т)-вход первого триггера 35 является информационным входом входного каскада 1, соединенные между собой тактовые входы триггеров 35 и 36 и третьи входы элементов И 36 и 38 являются тактовым входом входного каскада 1, а его выходами являются выходы элементов И. Логический коммутатор 17 содержит блок 39 элементов НЕ, сумматоры 4О и 41, блоки 42 и 43 сравнения, элементы НЕ 44-46, элемент ИЛИ 47, элементы И 48-50, выход переполнения первого сумматора 40 через первый элемент НЕ 44, а выход переполнения второго сумматора 41 непосредственно соединены соответственно с первым и вторым входами первого элемента И 48, выход которого подключен к первым входам второго элемента И 49 и .элемента ИЛИ 47, второй вход которого соединен с вь1ходом первого блока: 43 сравнения, а выход с первым входом третьего элемента И 5О выход второго блока 42 сравнения через второй элемент НЕ подключены к второму входу третьего элемента И 5О, второй вход второго элементам 49 и третий вход третьего элемента И 50 соединены соот- ветственно с входом и выходом третьего элемента НЕ 46, первые входы обоих сумматоров подключены к соответствую щим выходам блока 39 элементов НЕ, входы которого, являющиеся первой группой входов логического коммутатора 17, соединены с входами первой грпуппы бло ков 42 и 43 сравнения входов второй группы второго сумматора 44, явпяюши1еся входами второй группы логического коммутатора 17, подкюочены соответственно к входам второй группы первого блока 43 сравнения, входы18 второй гру пы первого сумматора 4О соединены с входом второй группы второго блока 42 сравнения, вход третьего элемента НЕ 46 является управляющим входом логического коммутатора 17, тактовым входом которого является третий вход второго эле-г мента И 42, соединённый с четвертым входом третьего элемента И 50, причем выходы второго и третьего элементов И 49 и 50 являются соответственно первым и вторым выходами логического коммутатора 17, третьим выходом которого явля ется выход второго блока 42 сравнения. Блок 26 выбора, перехода содержит уз лы 51 и 52 выделения переднего фронта элемент ИЛИ 53, двухтактный ЛКтриггер 54, элемент НЕ 55, вход пер вого узла 51 выделения переднего фронта соединен с входом триггера 54, являющегося первым входом блока 26, а К - вход триггера 54 являющийся вторым входом блока 26, соединен с входом второго узла 52 выделения фронта, подключенного выходом к.первому входу элемен та ИЛИ 53., второй вход которого соединен с выходом первого узла 51 вьщеления переднего фронта, а выход гпемента ИЛИ подключен к тактовому входу триггера 54, инверсный выход которого яв- .ляется первым, а прямой - вторым выходами блока 26, при этом вход элемента НЕ 55 является третьим входом, а его выход - третьим выходом блока 26. Блок 29 управления содержит блоки 56 и 57 сравнения и триггеры 58 и 59 выходы которых являются соответственно первым и вторым выходами блока, а тактовые входы - тактовым входом блока управления, причем счетные входы триг геров 58 и 59 соединены соответственно с выходами первого и второго блоков 56 и 57 сравнения, входы первой группы блока 29, входы второй группы первого блока 56 сравнения являются входами второй группы блока управления, а входы второй группы второго блока сравнениявходами третьей группы блока управления. Принцип работы блока управления ясно заключается в том, что при неравенстве кода чисел в блоках 56 или 57 сравнения на соответствующих выходах блока управления присутствует логический ноль. Триггеры 58 и 59 необходимы для привязки фронта сигнала на выходах блока 29 по фазе к тактовым импупьсам. Первый выход входного каскада 1 соединен с первым входом элемента ИЛИ 7 и с первыми входами соответствующих элементов И 4, первой группы, вторые входы элементов И 4 и 34 соединены с выходами соответствующих блоков 14 сравнения, а выходы - с соответствующими входами дискретного элемента 31 задержки, подключенного выходом к нулерому входу триггера 33, второй вы-.. (СОД входного каскада 1 соединен с вторым входом элемента ИЛИ 7, подключенного выходом к входам считывания блоков 14 сравнения группы и с первыми входами элементов И 34 второй группы, а выходы которых соединены с соответствующими входами дискретного элемента 32 задержки, подключенного выходом к единичному входу триггера 33. Такт(- вый вход входного каскада 1 соединен с тактовым входом блока 29 управления непосредственно и через элемент НЕ 5 с входами Делителей 10-13. Выход Делителя 10 подключен к тактовому входу генератора 2 псевдослучайной последователь ности, выходы соответствующих разрядов которого соединены с первыми входами блоков 14 сравнения. Выходы делителей 11 и 12 подключены к первым входам соответственно элементов И 22 и 23, вторые входы которых соединены соот ветственно с первым и вторым выходами блока 26 выбора перехода а выходы соответственно с тактовыми входами логических коммутаторов 17 и первыми входами элементов И 24 и 25, подключенных выходами к вычитающему и суммирующему входам реверсивного счетчика 30 соответственно. Выход делителя 13 соединен с тактовым входом генератора 6 псевдослучайных интервалов, выход которого через элемент НЕ 8 подключен к второму входу элемента И 25 и непосредственно - к второму входу эпемента И 24 и к управпяюшему входу логических коммутаторов 17, первый и вто рой выходы которых соединены соответст венно с суммирующими и вычитающими входами соответствующих реверсивных счетчиксш 19, а третьи выходы - с соответствующими входами общего элемента И 21| выход которого соединен с пёр вым входом блока 26 выбора перехода, второй и третий входы которого соединены соответственно с первым и вторым выходами блока 29 управления, подключенного первыми, вторыми и третьими входами соответственно к выходам разрядов регистров хранения 27 и 28 и реверсивного счетчика 30, вы ходы разрядов которого соединены таюке с управляющими входами управляемого делитегш 3, подключенного входом к выходу элементов НЕ 5, а выходом-к тактовым входам дискретных элементов 31 и 32 задержки. Выходы разря дов реверсивных счетчиков 19 соединены с первыми .входами соответствующих логачоских коммутаторов 17, а также с вторыми и третьими входами соответспзующих блоков 14 сравнения. Вторые входы всех логических коммутаторов 17, дфоме последнего 17yi, соединены с выходами разрядов соответствующих регистров хранения 20, а вторые входы посаеднегО логического коммутатора 17. соединены с входами максимального числа 16. 1 1оспеднего блока 14 сравнения. Выход генератора ослу чай ной последовательности 2 непосредственно и через элемент НЕ 9 соединен с третьими входами соответствующих элементов И 4. Третий выход блока выбора перехода 26 соединен с третьим входом элементом И 25. Выходом устройстве является выход триггера 33. Устройство моделирования дискретного радиоканала работает следующим образом. На входах 17- -го логического коммутатора устанавливают в параллельном коде двоичное число с U м разрядность двоичного числа, подаваемого в параллельном коде на первые входы блоков 14 сравнения с выходов разрядов генератора 2 псевдослучайных последовательностей Oi-1)- число логических коммутаторов 17. Перед началом работы устройства в реверсивные счетчики 19,-и соответствующие им регистры хранения 20 записывают N-разрядные числа М- 2, с помо щью которых задается закон распределения средней во времени плотности вероятности временных искажений фронтов посылок, при этом на входах 15 и 16 устанавливают соответственно числа М,у, . Число отводов дискретных линий задержки 31 и 32, которые могут быть реализованы, например, на регистрах сдвига, равно (2vi-l). Частота F импульсов, подаваемых на тактовые входы входного каскада 1 и блока 29 управления непосредственно и на входы делителей 1О-13 и управляемого Делителя 3 череэ элемент НЕ 5 должна удовлетворять следующему требованию: . R. где В - скорость передачи информации в Бодах. Входной каскад 1 формирует импульсы, совпадающие во времени с фронтами посыjioK дискретной информации, поступающей на его вход, пропуская на первый выход импульс Из последовательности F спедующий непосредственно за положительным фронтом, а на второй выход - за отрицательным фронтом. Входной каскад 1 работает следующим образом. На выходах первого триггера 35 устанавливается потенциал, соответствующий потенциалу на его первом входе в момент времени, соответствующий переднему фронту импульсов F, поступающих на его второй вход. Второй триггер 36 установится в это же положение через время 11 F так как потенциал на первом входе второго триггера 36 устанавливается с запаздыванием относительно переднего фронта импульса, устанавливающего первый триггер 35, который определяется временем задержки сигнала в триггере 35. Подавая на входы элементов И 37 и 38 сигналы с прямого и инверсного выходов различных триггеров и стробируя их импульсами синхронизации, на выходах элементов И 37 и 38 выделяются первые импульсы этой последовательности, следующие непосредственно за отри штельным или положительным фронтом информационного сигнала. Импульсы фронтов с выхода элемента ИЛИ 7 поступают на считывающие входы блоков 14 сравнения. Импульс .фронта проходит на выход блока 14 в случае, если текущее значение N- разрядного числа уп на выходах разрядов датчика псевдослучайных последовательностей 2 лежит в интервале . При использовании в качестве генератора 2 псевдослучайных последовательностей регистра сдвига с сумматором по модулю два в цепи обратной связи, обладающего тем 1.39 свойством, что генерируемые им числа |Л. равномерно распределены на интервале 1.0,2 3 (генератор М - последовательностей .с числом разрядов большим М), то частость появления импульса фронта на выходе -t-ro блока 14. сравнения равна Q -Мд-М - |2NИмпульс на первом выходе входного каскада 1 открывает по первому входу элементы И первой группы, выходы которых подключены к входам дискретного элемента 31 задержки. Импульс с выхода блока 14|- сравнения поступает на второй вход элемента И 4 первой группы ип элемента И 34 второй группы, выход кот рого подключен к v -му входу эпементов 31 и 32 задерл ки, импу пьс с выхода блока 14 сравнения, поступает на вторы входы элементов И 4 И 34, выходы кото рыхсоединенЕ ю ( и-)+1)-м и (У14Л -1)-м , входами элементов 31 и 32 задержки. Н тре7ъи входы элементов И 4, выходы которых соединены с входами элементов за держки от (и-1) до 1-го, поступает сигнал с выхода датчика псевдослучайных по следовательностей 2 непосредственно, а выходы которых соединены с входами с (10+1 )РО до (2W-l)-ro - через элемент, НЕ 9,. Так как появление единичного и нулевого сигнала на выходе генератора 2 равновероятно (свойство генератора М - последовательности), то импульсы отрицательных фронтов посыпок равновероятно могут поступить на (ц-1+1)-й и (Vl-i-i-l)-n входы элемента 31 задержки, а импульсы положительных фронтов - эле мента 32 задержки. Таким образом, частоты задержек импульсов фронта на величины |rl}n-ti-i) Tj-F&i-Ci-ill равны между собой, т, е. задержки фронта симметричны относи-Г « тельно величины , а сама частота задержек Т , Т - равноО -М -М -)2v Так как импульсы с элемента 31 задержки поступают на нулевой вхэд триггера 33, а импульсы с выхода элемента . 32 задержки - на единичный вход то с прямого выхода триггера снимается двоичный сигнал, отличающийся от исходного тем, что фронты посылок искажены во времени псевдослучайным образом по заданному закону распределения плотности вероятности этих искажений через чис- ла М . Работа устройства рассмотренным выше образом обеспечивает моделирование по оричным характеристикам гауссовского канала связи, причем, ecmiff y t-0 а ,с()(-- то некоторые импульсы фрон9тов не будут поступать на элементы 31 и 32 задержки, что соответствует в реальном канале связи ошибочному приему посылки из-за ее полной инверсии. Изменение среднего закона распределения временных искажений фронтов, т.е. имитация замираний сигнала в коротковолновом радиоканале, реаггазуется путем кэ- менения двоичных чисел М, находящихся в соответствующих реверсивных счетчи ках 19. Осуществляется это следующим образом. Импульсы с выхода делителя 11 через элемент И 22- поступают на тактовые входы логических коммутаторов 17, Если текущее значение числа ДА-, находящегося в реверсивном счетчике 10 удовле- . творяет условию К - А (М - число в регистре хранения 20), то импул сы, присутствующие на тактовом входе логического коммутатора 17, проходят на его первый или второй выход, т.е. на суммирующий или вычитающий вход реверсивного счетчика, в зависимости от того единичный игги нулевой сигнал присутствует на управляющих входах логических коммутаторов 17, куда он поступает с выхода генератора псевдослучайных интервалов 6. В случае К--М - и нулевом сигнале на выходе генератора 6 и А -М и единичном сигнале на выходе генератора 6 импульсы с тактового входа логического коммутатора на входы реверсивного счет- не проходят, т.е. числОМ. имеет возможность изменяться только в предеjvJлах К.. В случае . появЯ т1ление импульсов считывания на выходах всех блоков 14 сравнения равновероятно, что соответствует присутствию в канапе только шума . В случае М --М на третьем выходе логического коммутатора 17- формируется единичный сигнал, который поступает на соответствующий вход общего элемента 11 21. Логический коммутатор 17 работает следующим образом. На выходе переполнения сумматора 40, на входы которого подаются чнспа М и , присутствует логическая в случае К-гМ-, а на выходе элемента НЕ 44 присутствует логическая в спучае . На выходе переполнения сумматора 41 присутствует логическая в случае , так как на его входах присутствуют числа М и М На входах блоков 42 и 43 сравнения присутствуют соответственно пары чисел , Ки М-, АА, а на их,выходах устанавливается логическая соответственно в 1596 случаях и , На выходе эпемента НЕ 45, погическая црисутот вует соответственно в случае АЛ :|Ь Таким образом, на выходе элемента И 48 погическая присутствует в случае когда ,,. на выходе элемента ИЛИ 47 - в случае К. а тактовый импульс проходит на выход элемента И 49 в случае К 5 М Mjj и наличия единичного потенциала на управляющем входе логического коммутатора 17, а на выход элемента И 50 - в случае, когда и нулевом потенциале на jrnравлякяцем входе логического коммутатора 17. 11ри единичных потенциалах на всех входах элемента И 21. сигнал с его выхода поступает на первый вход блока 26 выбора перехода. На второй вход бло ка, поступает единичный сигнал с первого выхода блока 29 управления в случае равенства числа в реверсивном счетчике 30 чиспенио равного текущему коэффициенту депения управляемого Делителя 3, чисiiy в регистре 27, равному максимально возможному коэффициенту деления Делителя 3. На третий вход блока 26 поступает единичный со второго выхода блока 29 управления в случае равенства числа в ре версивном счетчике 30 числу в регистре 28, равному минимально возможному коэф(}мциенту деления 3. На третьем выходе блока выбора перехода 26 присутствует единичный сигнал при нулевом сигнале на его втором входе (коэффициент деления делителя 3 максимален). Блок 26 выбора перехода работает еле дующим образом.. . , Перед началом работы устройства мо- ;Делирования дискретного радиоканала триГ гер 54 блока 26 устана ливается в нулевое состояние. При этом возможность изменяться имеет сигнал на первом входе блока 26. При появлении положитепьного перепада на этом входе на выходе узла 51 выделяется импульс, который через элемент ИЛИ 53 проходит на такто вый вход триггера 54 и устанавливает его в единичное состояние, так как на его первом входе присутствует сигнал логической I. При этом на первом выходе блока 26 устанавливается логический О, а на втором - погическая . После этого возможность .изменяться имеет только сигнал на втором входе блока . 26 и, при появлении на нем положительного перепада, импульс с выхода узла 52 через элемент ИЛИ 53 проходит на тактовый вход триггера 54 и задним фронтом пе1 еводит его в обратное исходному 9.16, состояние, так как на входах Зи К присутствует логическая единица, т.е. в нулевое состояние. После этого возможность изменяться опять имеет только сигнал на первом входе блока 26. При появлении на нем отрицательного периода блок 26 по первому и второму выходам не изменяет своего состояния, которое меняется на обратное только при появлении на первом входе положительного перепада. На третьем выходе блока 26 присутствует догическая 1 только в случае логического нуля, на его третьем входе. Таким образом, сигнал с выхода элемента И 21 устанавливает на первом выходе блока 26 нулевой потенциал, а на втором - единичный. При этом элемент И 22 закрывается по второму входу, а эпемецт И 23 открывается и импульсы с выхода делителя 12 начинают поступать на первые входы элементов И 24 и 25. При единичном сигнале на выходе датчика псевдослучайных интервалов 6 эти импульсы проходят на вычитающий вход реверсивного счетчика ЗО, а при нулевом на суммирующий. При единичном сигнале на выходе датчика 6 частота на делителя 3 увеличивается, а при отрицательном - уменьшается. При увеличении частоты на тактовых входах линии 31 и 32 задержек абсолютные временные интервалы между моментом идеального положения фронта и моментом реального положения этого фронта уменьшается, так как величина -КГ1.м±С-цл)обратно пропорциональная , эратно 1 т е. в этом случае уменьшается дисп случае уменьшается дисперсия временных искажений фронтов, что соответствует увеличению отношения сигнал/шум в канале связи. По достижении коэффициента деления делителя 3, зафиксированного в реверсивном счетчике 30 минимального значения, элемент И 25 закрывается по третьему входу, что предотвращает дальнейшее уменьшение этого коэффициента. По достижении коэффициентом деления мат симального значения и появлении единичного сигнала на первом входе блока выбора перехода 26 элемент И 22 открывается, а элемент И 23 закрывается по второму входу. Таким образом, при единичном сигнале на выходе датчика 6, т.е. при увеличении отнощения сигнал/шум сначала увеличиваются. числа М в реверсивных счетчиках 19 ( М), а при М М начинает увеличиваться частота на тактовых входах элементов 31 и 32 заДержки, что приводит к уменьшению дисперсии временных искажений. При нупевом сигнале на выходе датчика 6 сначала уменьшается частота f, а затем -Mi WI (М -ч ). Таким образом, осуществляется имитация замираний в KB радиоканапе Коэффициент деления делителя 3 устанавливается таким образом, чтобы частота на его выходе была меньше скорос.ти передачи информации. Так как частота импульсов на выходе делителя 11 определяет значение гпубины замираний при изменении М, а частота импульсов на выходе делителя 12 значение глубины замираний при измене- НИИ i, то коэффициенты деления этих делителей подбираются таким образом, чтобы эти значения были равны. Коэффициент деления делителя 13 выбирается таКИМ образом, чтобы средний период смены полярности сигнала на выходе датчика 6 псевдослучайных интервалов, определяемый частотой импульсов на выходе делителя 13, равнялся выбранному периоду замираний в канале связи. Элемент НЕ 5 необходим для того, чтобы импульсы с выходов входного кас када 1 и делителей 10-13 не срвпадали во времени, чем обеспечивается устойчивость работы комбинационных схем уст ройства. Таким образом, предлагаемое устройство позволяет с достаточной степенью адекватности моделировать дискретный радиоканал связи с замираниями и обеспечивает бопее высокую степень воспроизводимости и стабильности параметров искажения сигнала в дискретном канале связи из-за отсутствия в предлагаемом устройстве аналоговых элементов, а также возможность в качестве параметра моделируемого канала непосредственно задавать закон распределения плотности вероятности временных искажений фронтов посылок. Кроме того, предлагаемое устройство повышает эффективность проверки и контроля аппаратуры приема и регистрации дискретных сообщений. Формула изобрете. ния 1. Устройство для моделирования дис кретного радиоканала, содержащее генератор псевдослучайной последовательности, управляемый делитель, элементы И, первый элемент НЕ, датчик псевдослучай ных интервалов и входной каскад, состоя щий из двух CD-триггеров и двух эпемен тов и, прямой выход первого D -триг гера соединен с D -входом второго ID - , триггера и первым входом первого элемента И, инверсный выход первого D триггера подключен к первому входу второго элемента И, прямой выход второго D-триггера подк точен к второму второго элемента И, а инверсный выход второго 3)-триггера соединен с вторым входом первого элемента И, U -вход первого D-триггера является информационным входом .устройства, объединенные тактовые входы D-триггеров и третьи входы элементов И -соединены с тактовым входом устройства, отличающееся тем, что, с целью повышения достоверности моделирования, оно дополнительно содержит элемент ИЛИ, второй и третий элементы НЕ, четыре делителя, группу блоков сравнения, группу логических коммутаторов, группу реверсивных счетчиков, группу регистров хранения, общий элемент И, две группы элементов И, бпок выбора перехода, первый и второй дополнительные регистры хранения, блок управления, дополнительный реверсивный счетчик, два дискретных элемента задержки и триггер, причем выход первого элемента И входного каскада соединен с первым входом элемента ИЛИ и с первыми входами элементов И первой группы, вторые входы первых элементов И первой и второй групп подключены к выходу первого блока сравнения группы, выходы К-го блока сравнения группы (Ц. 2) соединены с вторыми входами 2(К-1)-го и ()-го элементов И первой и второй группыJ выход второго элемента И входного каскада подключен к первым входам элементов И второй группы и к второму входу элемента ИЛИ, третьи входы -у.(., ..., ) элементов И первой группы непосредственно, а третьи входы к-х элементов И вто рой группы через первый элемент НЕ соединены с выходом генератора псевдослучайной последовательности, вход которого подкшочен к выходу первого делителя . частоты, выходы первых элементов И первой и второй групп подключены к V -м входам первого и второго дискретных ч элементов задержки соответственно, выходы (2fA+l)-x элементов И (, ,..., VI-1) первой и второй группы соединены соответственно с (yi + АЛ)-м входом первог1 о и второго дискретных элементов задержки, выходы 21 -X элементов (t-l, ..., V +1) первой и второй групп подключены соответственно к (И-Ь)-м входам i996 первого и второго дискретных элементов задержки, тактовые входы которых соедииены с выходом управляемого делите- пя частоты, выходы первого и второго дискретных эпементов задержки подкпючены к нулевому и единичному входам триггера, единичный выход которого является выходом устройства, выход элемента ИЛИ соединен с входами считывания блоков сравнения группы, входы первой группы входов которых подключены к разрядным выходам генератора псевдослучайной последовательности, входы второй группы входов первого и последнего блоков сравнени.. группы соединены с входами минимапьного и максимального первого и поспедиого погических коммутаторов групГ1Ы соответственно, группа выходов -j-ro роверснвного счетчика группы (-5 -1,..., И-1) подкпючена к входам второй группы J го блока сравнения группы, к входам первой группы входов (j+l)-ro блока сравнения и к входам первой группы логических коммутаторов группы, входы второй группы 1 -X погических коммутаторов группы ()1,,..,) соединены с выходами соответствующего регистра хранения группы, входы третьей группы погических коммутаторов группы подключены соответственно к вхбдам констант устройства, тактовые входы логических коммутаторов группы соединены с выходом первого элемента И, первый вход которого подключен к выходу второго делителя частоты, а второй вход - к первому выходу блока выбора перехода, управляющие входы логических коммутаторов группы соединены с выходом датчика псевдослучайных интервалов, первым входом второго элемента И, входом второго элемента НЕ , первый выход логических коммутаторов группы соединен с суммирующим входом соответствующего реверсивного счетчика группы, а второй выход с его вычитающим входом, третьи выходы логических коммутаторов подключены соответственно к входам общего элемента И, выход которого соединен с первым входом блока выбора перехода, второй и третий входы которого подключены соответственно к первому и второму выходам блока управления, тактовый вход которого соединен с тактовым входом устройства непосредственно, а через второй элемент НЕ - с входами четырех делителей частоты и входом управляемого делителя частоты, группа управляющих входов которого подключена к разрядным выходам реверсивного счетчика и к входам первой 920 группы блока управпения, входы второй группы которого соединены с разрядными выходами первого дополнительного регистра хранения, а входы третьей группы бло- ка управпения подключены соответственно к разрядным выходам второго дополнительного регистра хранения, выход первого делителя частоты соединен с входом генератора псевдослучайной последовательности, выход третьего делителя частоты подключен к первому входу третьего элемента И, второй вход которого соединен с в.торым выходом блока выбора переключения, а выход - с вторым входом второго элемента И и с первым входом четвертого элемента И, второй вход которого подключен к выходу третьего эле.мента ME, третий вход четвертого элемента И соединен с третьим выходом блока выбора перехода, суммирующий вход дополнительного реверсивного счетчика подключен к выходу второго элемента И, а вычитающий вход - к выходу четвертого элемента И, выход четвертого делителя частоты соединен с входом датчика псевдослучайных интервалов, 2. Устройство по п. 1,отличают, е е с я тем, что блок управпения содержит два блока сравнения и два триг- гера, выходы которых являются соответственно первым и вторым выходами бло- . тактовые входы - тактовым входом блока управления, причем счетные входы триггеров соединены соответственно с выходами Первого и второго блоков сравнения, входы первой группы которых являются входами первой группы блока управления, а входы второй группы первого блока сравнения являются входами второй группы блока управления, входы второй группы Второго блока сравнения - входами третьей группы блока управления, 3, Устройство по п. 1, о т л и ч а ю ш е е с я тем, что логический коммутатор содержит блок элементов НЕ, два сумматора, два блока сравнения, три элемента НЕ элемент ИЛИ, три элемента И, выход переполнения первого сумматора через первый элемент 1Е, а выход переполнения второго сумматора непосредственно соединены соответственно с первым и вторым входами первого элемента И, выход которого подключен к первым входам второго элемента И и элемента ИЛИ, второй вход которого соединен с выходом первого блока сравнения, а выход - с первым входом третьего элемента И, выход второго блока сравнения через второй элемент НЕ подключен к

второму входу третьего эпемента И, второй вход второго элемента И и третий вход третьего эпемента И соединен соответственно со входом и выходом третьего элемента НЕ, первые входы обоих сум-S маторов, подключены к соответствующим выходам блока элементов НЕ, входы которого, являющиес Я первой группой входов логического коммутатора, соединены с входами первой группы блоков сравнения, 10 входы второй группы второго сумматора, являющиеся входами второй группы логического коммутатора, подключены соответственно . к входам второй группы первого блока сравнения, входы второй груп-15 пы первого сумматора, соединены с входами второй группы второго блока сравнения, вход третьего инвертора является управляющим входом логического коммутатора, тактовым входом которого явля- 20 ется третий вход второго элемента И, сое диненный с четвертым входом третьего элемента И, выходы второго и третьего элементов И являются соответственно пер вым и вторым выходами логического ком-зз му.татора третьим выходом которого является выход второго блока сравнения.

Источники информации, принятые вр при экспертизе

r

:t f

ui.la.

Ж

лг

Ж

ж

ШЕ

иш

uz.2.5

тг

/f

т

55 г

.ut.a

Л

Ж

sr иг

«i.v

Ует.О

1

iuz.S

Авторы

Даты

1982-09-30—Публикация

1980-12-31—Подача