(54) ТРИГГЕР S-ТИПА

| название | год | авторы | номер документа |

|---|---|---|---|

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| Интерфейс передачи данных | 2018 |

|

RU2682435C1 |

| СХЕМА ВОЗБУЖДЕНИЯ ДИСПЛЕЯ, ДИСПЛЕЙНАЯ ПАНЕЛЬ И УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2487424C1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ | 2002 |

|

RU2229158C1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| Устройство для программного управления | 1989 |

|

SU1700537A1 |

| Многофункциональный тактируемый триггер с управлением по срезу тактового сигнала | 1986 |

|

SU1359885A1 |

| @ -Триггер | 1984 |

|

SU1234951A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1372326A1 |

1

Изобретение относится к автоматике.

Данный RST-триггер Master-Slave может быть использован в качестве как входного накопителя, так и накопителя обработки информации в цифровых устройствах вычислительных машин.

Известен триггер S-типа, выполненный по способу Master-Slave на основе известного триггера D-типа.

Цель изобретения - создание универсального триггера.

Предлагаемый триггер отличается тем, что вентили «И - НЕ, управляющие единичным и нулевым плечами асинхронного RS-триггера Master, имеют дополнительные входы, S и К соответственно. При подключении выхода Q триггера Slave ко входу S триггер S-типа выполняет функции триггера 1К-типа; при подключении входа ко входу R триггер выполняет функции триггера DV-типа.

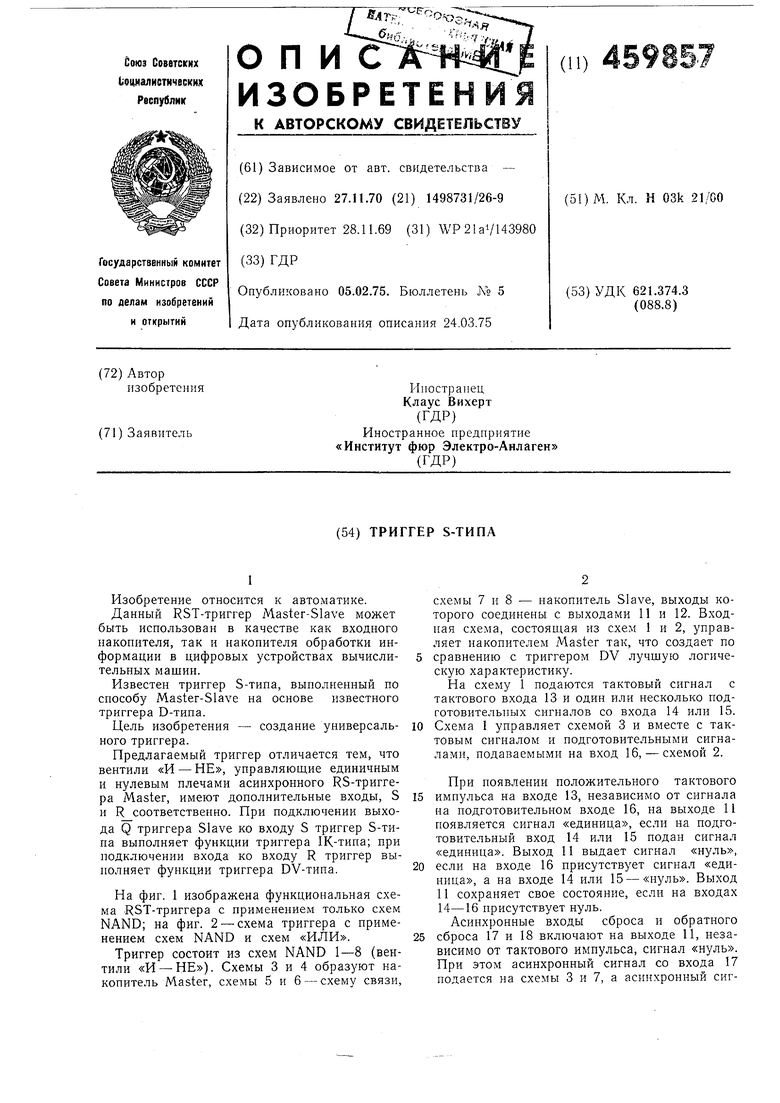

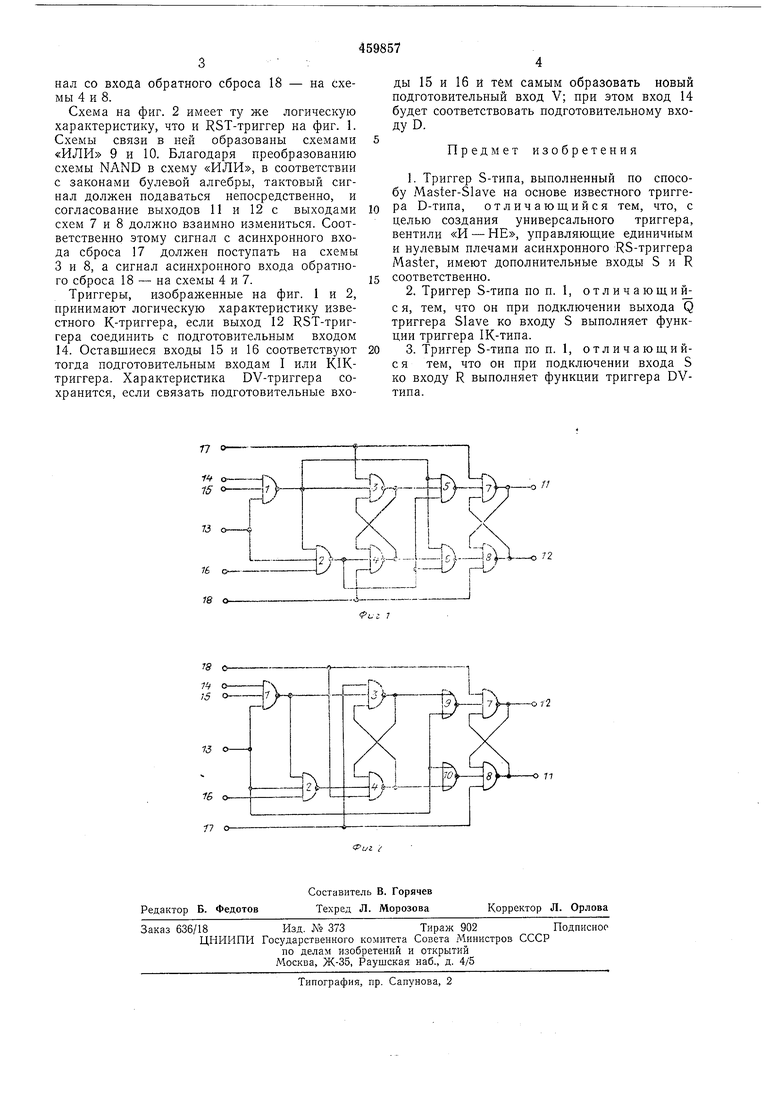

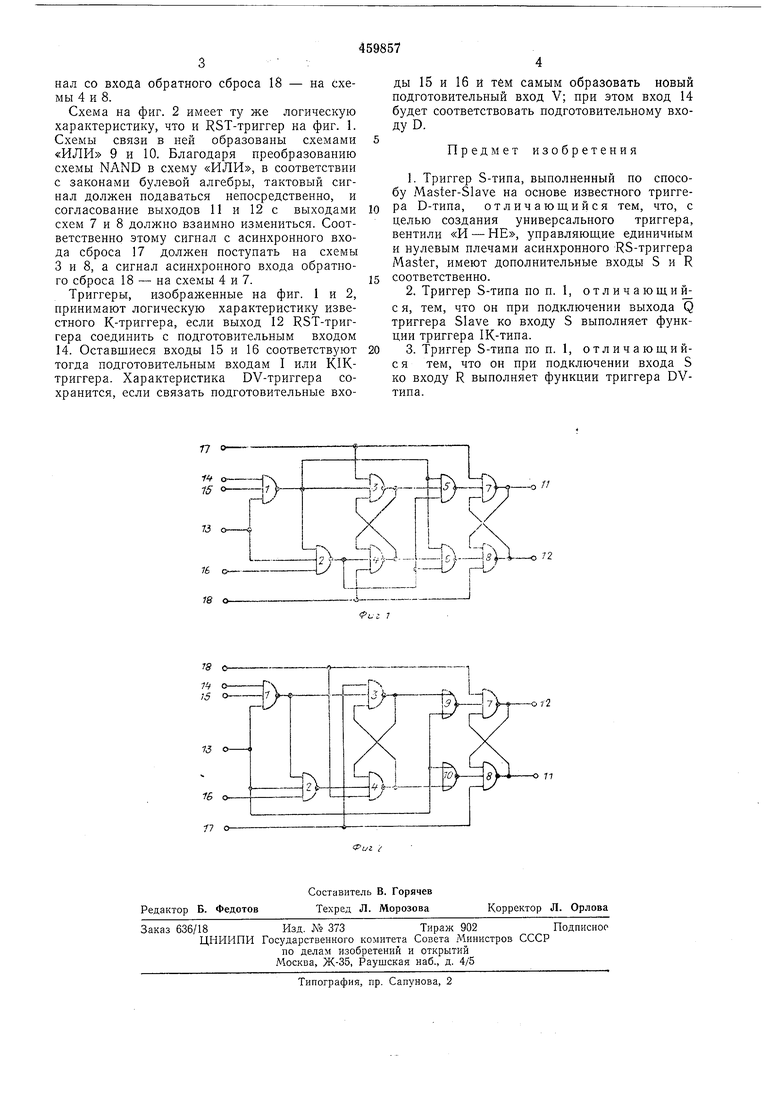

На фиг. 1 изображена функциональная схема .RST-триггера с применением только схем NAND; на фиг. 2 - схема триггера с применением схем NAND и схем «ИЛИ.

Триггер состоит из схем NAND 1-8 (вентили «И - НЕ). Схемы 3 и 4 образуют накопитель Master, схемы 5 и 6 - схему связи.

схемы 7 и 8 - накопитель Slave, выходы которого соединены с выходами 11 и 12. Входная схема, состоящая из схем 1 и 2, управляет накопителем Master так, что создает по

сравнению с триггером DV лучшую логическую характеристику.

На схему 1 подаются тактовый сигнал с тактового входа 13 и один или несколько подготовительных сигналов со входа 14 или 15.

Схема 1 управляет схемой 3 и вместе с тактовым сигналом и подготовительными сигналами, подаваемыми на вход 16, - схемой 2.

При появлении положительного тактового импульса на входе 13, независимо от сигнала на подготовительном входе 16, на выходе 11 появляется сигнал «единица, если на подготовительный вход 14 или 15 подан сигнал «единица. Выход 11 выдает сигнал «нуль, если на входе 16 присутствует сигнал «единица, а на входе 14 или 15 - «нуль. Выход 11 сохраняет свое состояние, если на входах 14-16 присутствует нуль.

Асинхронные входы сброса и обратного сброса 17 и 18 включают на выходе 11, независимо от тактового импульса, сигнал «нуль. При этом асинхронный сигнал со входа 17 подается на схемы 3 и 7, а асинхронный сиг

Авторы

Даты

1975-02-05—Публикация

1970-11-27—Подача