памяти, дешифратор 9 устройств вводавывода, шинный формирователь 10 ввода-вывода, шесть элементов ИЛИ 11-16, два элемента И 17 и 18, три триггера , шинный формирователь 22, регистр 23, схему 2k сравнения, приоритетный шифратор 25J мультиплексор 26, элемент 27 задержки Цель достигается за счет реализации режима логического прерывания. Новыми в системе являются три элемента ИЛИ 1A-16 два триггера 20 и 21, приоритетный шифратор 25, мультиплексор 26, элемент 27 задержки. 2 табл., k ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

Изобретение относится к системам программного управления и может быть использовано в автоматизированных системах для управления технологическим оборудованием. Цель изобретения - повышение быстродействия и расширение области применения КС. Устройство для программного управления технологическим оборудованием 'содержит микропроцессор 1, тактовый генератор 2, системный контроллер 3, буферные усилители 4, дешифратор 5 адреса, блок 6 постоянной памяти программ, блок 7 оперативной памяти данных. шинный формирователь 8 оперативнойa,.LZ.2

Изобретение относится к устройствам программного управления и может быть использовано в автоматизирован- ных системах для управления технолог гическим оборудованием, например, в системах числового программного упраjieHMfl производственных комплексов, роботов, манипуляторов и т.д.

Известно устройство программного управления, содержащее датчики.состоний, генератор импульсов, триггеры,

дешифраторы, счетчики единиц и десятков, блок набора программ, элемент; И, ИЛИ, НЕ„ Его недостатком является низкая произаодительность, НаиСюлее близким к предлагаемому является устройство для программного управления технологическими процессами, состоящее из микропроцессора, тактового генератора; системного контроллера, дешифратора адреса памяти, оперативной памяти, постоянной памяти; шинного формирователя памяти дешифратора адресов ввода-вывода, шинных формирователей ввода-вывода, Tijiex шинных формирователей триггера, регистра, схемы сравнения, четырех схем И, трех схем ИЛИ.

Недостатком его является низкое быстродействие и узкая область применения. Это обусловлено следующими обстоятельствами.

Технические средства прототипа обеспечивают многоальтернативное ветвление по значению логических условий, поступающих от датчиков, в строго определенные моменты времени, при подключении соответствующей подпрограммы основной программой. При этом заранее неизвестен факт изменения логических условий, т.е. если они не изменились, то многоальтернативное ветвление будет проведено вхолостую - сформируется управляюа1ий сигнал такой же, как и в предыдущем 8efвлeнии. Если логические условия уже изменились, а время их опроса

еще не подошло, то это приводит к снижению времени реакции, .понижающему быстродействие при многоальтернативном ветвлении относительно скоросг ти изменения логических условий; к i невозможности использования известно го устройства в тех задачах реального времени, которые требуют максимальной реакции, например в аварийных ситуациях технологического оборудования, с которых сигнализирует не один датчик, а несколько (причем в ряде случаев необходим учет и предистории процесса).

Все это снижает быстродействие известного устройства и снижает область его применения.

Цель изобретения - повышение быстродействия и расширение области применения .

Сущность изобретения заключается в повышении быстродействия и расширении области применения устройства для программного управления -технологическим оборудованием путем введения дисциплины логического прерывания - прерывания с формированием автоматных отображений, старшего по приоритету обычных прерываний; в программной записи в регистр исходного состояния входов логических условий; в программном разрешении логического прерывания путем вывода логической единицы в первый триггер; в формировании обычных прерываний, а также прерываний при изменении состояния входов логических условий, старших по приоритету, чем обычные прерывания; в смещении адресов постоянной памяти для адресации программ реакции на логическое прерывание,которая для микропроцессора расположена по тем же адресам, что и адреса подпрограмм (векторов) обычных прерываний; в программном формировании автоматных отображений для обработки изменения состояния входов логических условий ь (реализация последовательностного или комбинационного автомата) с выд чей управляющих воздействий на информационные выходы; в программном снятии смещения адресов постоянной памяти после считывания микропроцес сором команды возврата из логическо го прерывания в основную программу, а также записи в регистр нового состо яния логических условий. Введение второго триггера и соответствующих ему связей позволяет сме щать адресное пространство блока постоянной памяти программ, переключит мультиплексор по сигналу подтверждения прерывания, если значения логических условий изменились, а также записывать в регистр измененное значение логических условий при реализации новой дисциплины - логического прерывания - с формированием авто-, Матнь1х отображений. Введение третьего триггера и соот ветствующих ему связей позволяет формировать запрос прерывания как пр обычном прерывании, так и при логическом прерывании - с формированием автоматных отображений. Введение приоритетного шифратора и - соответствующих ему связей позволя ет формировать код запроса, старшего по приоритету,и сигнал наличия запро са при обычных прерываниях, младших по приоритету логического прерывания с формированием автоматных отображений . Введение мультиплексора и соответ ствующих ему связей позволяет формировать вектор прерывания, как при обычных прерываниях, так и при логическом прерывании с формированием автоматных отображений. Введение элемента задержки и соот ветствующих ему связей позволяет обнулять второй триггер после считывания микропроцессором команды возврата из логического прерывания с целью устранения смещения блока постояиной памяти программ вторым триг гером. Введение четвертого элемента ИЛИ и соответствующих ему связей позволя ет обнулять второй триггер при начальном сбросе и по сигналу элемента задержки - по окончанию логического прерывания. Введение пятого элемента ИЛИ и соответствующих ему связей позволяет l устанавливать третий триггер для формирования запроса на прерывание как при обычном прерывании, так и при логическом прерывании. Введение шестого элемента ИЛИ и соответствующих ему связей позволяет обнулять третий триггер после перехода микропроцессора в цикл обработки прерывания. При использовании предлагаемого изобретения может быть получен положительный эффект, состоящий в повышении быстродействия и расширении области применения. На фиг,1 изображена функциональная схема системы для программного управления; на фиг.2 - фрагмент временной диаграммы реакции системы на обычное прерывание; на фиг.З то же, реакции на логическое прерывание с формированием автоматных отображений; на фиг. - граф последовательного автомата из примера конкретного выполнения системы. Устройство для программного управления технологическим оборудованием содержит микропроцессор 1, содержащий выходы 1.1 адреса, группу входов-выходов 1.2 данных,выходы 1.3 управления записью иприемом данных, тактовые входы первой I. и второй 1.5 фаз, входы сброса 1.6, готовности 1.7, выход 1,8 синхронизации, вход 1.9 запроса прерываний, выход 1.10 разрешения прерывания, тактовый генератор 2, содержащий входы 2.1 и 2.2 подключения кварцевого резонатора, вход 2.3 синхронизации, тактовые выходы первой 2.4 и второй 2.5 фаз, выход 2.6 сброса, выход 2.7 готовности, выход 2.8 синхронизации, системный контроллер 3 содержащий первую группу информационных входоввыходов, вторую группу информационных выходов-входов 3.1 данных, являющуюся шиной данных устройства, выходы 32 управления чтением памяти, аписью в память, управления вводом устройстве ввода, выводом в устройстве вывода, подтверждения прерывания, являющиеся шиной управления устройства, буферные усилители А, содегзгжащие выходы .1, являющиеся шиной адреса устройства, дешифратор 5, адреса памяти, содержащий выход 5.1 подключения блока 6 постоянной памяти программ, блок 7 оперативной памяти данных, шинный формирователь 8 оперативной памяти, дешифратор 9 уст ройств ввода-вывода, содержащий груп пу выходов 9И подключения устройств ввода-вывода, выходы 9-2 и 93 шинные формирователи 10 устройств ввода-вывода, шесть элементов ИЛИ 11-16 два элемента И 17 и 18; три триггера , шинный формирователь 22, регистр 23, схему сравнения и приоритетньм шифратор 25, имеющий информационные выходы 25о1 и выход 25.2 управления, мультиплексор 26, элемент 27 задержки, вход 28 сброса, вход 29 готовности, вход 30 захвата, и выход 319 информационные входы 32, информационные выходы 33, входы З логических условий, входы 35 запросов на прерывание. Третий и четвертый входы тактовог генератора 2 являются входами сброса 28 л готовности 29 устройства соответственно. Первый 2Д и второй 2, тактовые выходы тактового генератора 2 подключены к первому 1. и второму 1,5 тактовым входам микропроцес сора 1 соответственно. Третий 2,6 и четвертый 2,7 выходы тактового гене,ратора 2 подключены к входам сброса 1«6 и готовности 1.7 микропроцес сора 1 соответственно. Пятый выход 2.8 тактового генератора 2 подключен к входу синхронизации системного контроллера 3. Адресные выходы 1.1 микропроцес7 сора 1 подключены к входам буферных усилителей k. Группа входов-выходов 1с2 данных и выходы 1.3 управления записью и приемом данных микропроцес сора 1 подключены к первой группе информационных входов-выходов и входам управления записью и приемом дан ных системного контроллера 3 соответственно. Вход захвата микропроцес сора 1 является входом 30 захвата си стемы. Выход ожидания микропроцессо;ра 1 является выходом 31 ожидания системы. Выход управления приемом да ных микропроцессора 1 подключен к :управляю1цим входам блока 6 постоянно памяти программ, шинного формирователя 8 оперативной памяти и к перво;му входу первого элемента И 17. Объединенные инверсные выходы раз решения буферных усилителей k подключены к отрицательной шине источни ка питания выходы которых являются шиной Ал адреса устройства. Вторая группа информационных входов-выходов системного контроллера 3 является шиной 3.1 данных устройства. Выходы управления чтением памяти, записью в память, вводом, выводом, подтверждения прерывания системного контроллера 3 являются шиной 3.2 управления устройства. Группа информационных входов дешифратора 5 адреса памяти, выходы дешифратора 9 устройств ввода-вывода, адресные входы блока 7 оперативной памяти данных, блока.6 постоянной памяти программ подключены к шине .1 адреса устройства. Вход разрешения дешифратора 5 адреса подключен к выходу первого элемента ИЛИ 11, первый и второй входы которого подключены к выходам управления чтения памяти и записи в память шины 3.2 управ ления соответственно. Первый выход 5.1 дешифратора 5 адреса подключен к первому входу разрешения блока 6 постоянной памяти программ. -Второй выход 5.2 дешифратора 5 адреса подключен к входу разрешения шинного формирователя 8 оперативной памяти и к входу разрешения блока 7 оперативной памяти данных. Информационные входы блока 7 оперативной памяти данных подключен к второй группе информационных входоввыходов шинного формирователя 8 оперативной памяти. Информационные выходы блока 7 оперативной памяти данных подключены к третьей группе информационных входов-выходов шинного формирователя В оперативной памяти. I Вход разрешения дешифратора 9 устройств ввода-вывода подключен к выходам управления вводом из устроиств ввода и выводом в устройства вывода системного контроллера 3 через элемент ИЛИ 12 соответственно. Группа выходов 9.1 дешифратора 9 устройств ввода-вывода подключена соответственно к группе входов разрешения шинного формирователя 10 устройств ввода-вывода, вход разрешения которого подключен к выходу управления вводом из устройства ввода системного контроллера 3. Входы шинного формирователя 10 устройств ввода-вывода являются информационными входами 32 системы, а выходы - информационными выходами 33 устройстве. Выход первого элемента И 17 подключен к входу разрешения шинного формирователя 22. Входы сброса регистра 23 и перво го триггера 19 подключены к выходу 2.6 сброса тактового генератора 2. Выходы регистра 23 подключены к первой группе Ёходов схемы 2 сравнения выход которой подключен к первому входу второго элемента И 18, второй вход которого подключен к выходу пер вого триггера 19, информационный вход которого подключен к разряду ши ны 3.2 данных системы. Вход синхрони зации регистра 23 подключен к выходу третьего элемента ИЛИ 13, первый вход которого подключен к третьему выходу 9.3 дешифратора 9 устройства вводаг вывода, а второй вход подключен к выходу второго триггера 20,подключенному к адресному входу муль типлексора 2б, старшему адресному входу блока 6 постоянной памяти программ и дополнительному информацион ному входу дешифратора 5 адреса. Третий выход 5.3 дешифратора 5 адреса подключен к входу элемента 27 задержки, выход которого подключен к первому входу четвертого элемента ИЛИ I. Второй инверсный вход четвертого элемента ИЛИ 1 k подключен к выходу первого триггера 19.Третий вход четвертого элемента ИЛИ I подключен к входу сброса первого триггера 19-Выход четвертого элемента ИЛИ 1 подключен к входу сброса второго триггера 20, информационный вход которого подключен к выходу схемы 2k сравнения, а выход синхронизации которого подключен к выходу подтверждения прерывания системного контроллера 3 Вход синхронизации первого триггера 19 подключен к второму выходу 9.2 дешиф ратора 9 устройств ввода-вывода Информационные входы регистра 23, вторая группа входов схемы 2k сравне ния и вторая группа входов мультипле сора 26 являются входами 3 логимесКИХ условий системы. Второй вход первого элемента И 17 подключен к выходу подтверждения прерывания системного контроллера 3. Третий вход второго элемента И 18 подключен к выходу 1.8 синхронизации микропроцессора 1, а его четвертый вход подкгвочен к выходу 1.10 разрешения прерывания микропроцессора 1. ;Выход второго элвмента И 18 подключен к первому входу пятого элемента ИЛИ 15, второй вход которого подключен к выходу 25.2 управления приоритетного шифратора 25. Входы приоритетного шифратора 25 являются входам 35 запросов на прерывание системы. Информационные выходы 25.1 приоритетного шифратора 25 подключены к первой группе входов мультиплексора 26, выходы которого подключены к первой группе информационных входов шинного формирователя 22, к второй группе информационных входов которого подключены выходы блока формирователя Команды векторного перехода, выполненного путем подключения соответствующих разрядов шинного формирователя через ограничительный резистор к положительному полюсу источника питания. Выход пятого элемента ИЛИ 15 подключен к входу данных третьего три|- гера 21, вход сброса которого подключен к выходу шестого элемента ИЛИ 1б. Первый инверсный вход шестого элемента Или 1б подключен к выходу 1.10 разрешения прерывания микропроцессора 1 , а второй его вход подключен к выходу 2.6 сброса тактового генератора 2. Выход третьего триггера 21 подключен к выходу 1.9 запроса прерывания микропроцессора 1. Вход синхронизации третьего триггера 21 подключен к тактовому выходу 2.4 первой фазы тактового генератора 2. Микропроцессор 1 предназначен для выполнения программы, т.е последовательности команд, используемой для реализации алгоритма управления и для управления системой с шинной органи™ зацией. Микропроцессор воспринимает внешние тактовые сигналы и внешние 30-33 сигналы управления и генерирует сигналы адреса (1.1) данных (1.2) а также сигналы управления (ЬЗ). Микропроцессор 1 может быть реализован, например, на стандартной интегральной микросхеме КР580ИК89А. Тактовый генератор 2 предназначен ля формирования двух высоковольтных (12В) неперекрывающихся последоваельностей тактовых импульсов (2.4, ,5), формирования управляющих сигнаов сброса (2.6) и готовности (2.7) о внешним сигналам системы (2.8, «9) и для формирования системного броса (2.8) по синхроимпульсу (2.9), оступающему с микропроцессора 1, и может быть реализован, например на стандартной интегральной микросхеме КР580ГФ24, (ножки 13,12 и 6 не задейст вуются). Системный контроллер 3 предназначен для увеличения нагрузочной способности шины 3.1 данных и организации двунаправленной передачи MBHHBIXS для фиксации слова управления микропроцессора 1, поступающего по шине данных в момент поступления системно го строба (2.8) с тактового генератора 2, и формирования в соответствии со словом управления и сигналами записи и приема данных (1.3) микропроцессора 1 шины 3.2 управления уст ройства для каждого машинного цикла. 11ииа управления устройства включает йигналы управления чтением памяти, записью в память, вводом в устройство ввода, выводом из устройств зыЕОда, подтверждения прерывания, Системнь Й контроллер 3 может быть оеепизован, например, на стандартноп интегральной микросхеме КРЬ80ВК28, Буферные усилители и шинные формирователи В и 10 предназначены для увеличения нагрузочной способности шины ЗИ данных системы и для органи зации двунапрааленной передачи данных по шине 3.1 данных (второй группы выходов-входов системного контроллера) к блокам памяти или из блоков памяти, к внешним устройствам или из внешних устройств в зависимости от управляющих сигналов Е1 и Е2, При отсутствии управляющих сигналов выходы шинных формирователей находятся в высокоимпедансном состоянии,. отключены от шины данных. Шинные фор мирователи могут, быть реализованы на стандартных интегральных микросхемах 589 лтб, Шинный формирователь 8 блока оперативной памяти данных, предназначен для увеличения нагрузочной способнос ти шинных данных 3.1, дяя под шючения выходов блока 7 оперативной па:мяти к шине 3.1 данных в режиме чте ния, для подключения входов данных блока 7 оперативной памяти к шине 3« данных в режиме записи. Шинные формирователи 10 вводавывода предназначены для увеличения ;нагрузочной способности шины ЗП да ных и для подключения к шине З.И Сданных информационных входов 32 в р жиме ввода из устройств ввода, для подключения шины 3.1 данных к информационным выходам 33 в режиме вывода в устройства вывода. Буферные усилители k предназначены для усиления нагрузочной способности шины А.1 адреса системы, а также для перевода своих выходов в высокоимпедансное состояние при активиро-: вании разряда Подтверждение захвата выходов 1.3 управления микропроцес- сора 1.i Дешифратор 5 адреса предназначен для дешифрации адреса, выставленного йа шине .1 адреса системы в том слуМае, если активирован выход элемента ИЛИ 11. Для подключения блока постоянной памяти программ возбуждается выход 5о1 дешифратора 5, для подключения блока 7 оперативной памяти данных и шинного формирователя 8 оперативной памяти - выход 5.2. Кроме того, дешифратор 5 адреса учитывает информацию на выходе триггера 20 и дешифрирует адреса команд возврата из программ обработки логического прерывания. При этом возбуждается выход 5.3. В обычном режиме работы дешифрация шины адреа производится с учетом нулевого состояния выхода триггера 20. Дешифратор адреса может быть реализован, например, на стандартных интегральных микросхемах 155ИДЗ. Дешифратор 9 устройств ввода-вывода предназначен для дешифрации информации на шине j.l адреса системы в том случае, если активирован выход элемента ИЛИ 12, для подключения шинных формирователей 10 вводы-вывода и инициализации системы на логическое прерывание. Для подключения шинных формирователей 10 ввода-вывода активируется один соответствующий разряд группы выходов 9.1 подключения внешних устройств. Для стробирования триггера 19, имеющего определенный адрес при выводе по этому адресу (ввод по этому адресу не используется) , активируется выход 9.2. Для стробирования триггера 23 через элемент ИЛИ 13 таким же образом возбуждается выход 9.3. Дешифратор 9 устройств ввода-вы- j вода может быть реализован, напримерj на стандартных интегральных микросхе-f мах 155 ИДЗ. Первый элемент ИЛИ 11 предназначе для формирования разрешающего сигнал Е1 дешифратора 5 адреса памяти, по на личию на шине 3.2 управления одного из управляющих сигналов чтения памяти или записи в память. Второй элемент ИЛИ 12 предназначе для формирования разрешающего сигнал для дешифратора 9 устройств ввода-вы вода при наличии на шине 3.2 управле ния одного из управляющих сигналов ввода из устройства ввода или вывода в устройство вывода. Третий элемент ИЛИ 13 предназначе для управления входом синхронизации регистра 23 как выходом 9.3 дешифратора 9, так и выходом второго триггера 20 для записи в регистр 23 или начальирго состояния логических условии входов 3, либо для записи измененного и уже обработанного значения логических условий входов З. Четвертый элемент ИЛИ k предназна чен для управления входом обнуления второго триггера 20 либо при начальном сбросе с выхода 2„6 генератора 2, либо сигналом с выхода элемента 27 задержки по окончанию логического прерывания - после считывания команды возврата микропроцессором 1, либо если отсутствует разрешение на логическое прерывание (обнулен первый триггер 19) Пятый элемент ИЛИ 15 предназначен для управления входом данных третьего триггера 21 для формирования запро са на прерывание либо сигналом с выхода 25.2 приоритетного шифратора 25 (обычное прерывание) либо сигналом с второго элемента (логическое прерывание). Шестой элемент ИЛИ 1б предназначен для управления входом сброса третьего триггера 21 либо при начальном сбросе - сигналом (2,6) тактового генератора 2, либо при обнулении выхода Т о 10 разрешения прерывания микропроцессора 1 о При активировании выхода элемента ИЛИ 16 триггер 21 обнулен независимо от информации на его выходе данных и синхронизации Первый элемент И 17 предназначен для управления входом разрешения шинHojo формирователя 22 для подключения его выходов к шине 3.1 данных . в том случае, еслина шине 3.2 управления имеется управляющий сигнал подтверждения прерывания, а на выходах 1.3 управления микропроцессора 1 сигнал приема данных, т„е. когда микропроцессор считывает вектор прерывания с шины З данных. Второй элемент И 18 предназначен для управления пятым элементом ИЛИ 15 при формировании запроса на логическое прерывание в том случае, если активирован выход схемы 2Ц сравнения (изменились логические условия), прерывания разрешены ( активирован выход 1.10 микропроцессора 1), поступил синхроимпульс с выхода 1„8 микропроцессора 1 и установлен первый триггер 19. Первый триггер 19 предназначен д/1я управления вторым элементом И 18 и четвертым элементом ИЛИ Н с целью разрешения дисциплины логического прерывания. Если таковы запрещены, то элемент И 18 заблокирован, а три|- гер 20 через элемент ИЛИ I удерживается в нулевом состоянии Первый триггер 19 устанавливается в нулевое состояние начальным сбросом по своему асинхронному входу об нуления, устанавливается и обнуляется разрядом шины Зо1 данных по переднему фронту сигнала на выходе дешифратора 9 Первый триггер 19 может быть реализован, например, на стандартной интегральной микросхеме 155ТМ2, Второй триггер 20 предназначен для управления старшим разрядом адреса блока 6 постоянной памяти npoi- раммы, входом адреса мультиплексора 2б и третьим элeмeнtoм ИЛИ 13 при реализации логического прерывания Второй триггер 20 устанавливается по переднему фронту управляющего сигнала подтверждения прерывания шины Зо2 управления, если активирован выход схемы 2k сравнения. Это необходимо для обеспечения приоритета изменений логических условий входов 3 по отношению к запросам на входах 35 Таким образом, даже если запрос на прерывание (1.9) вызван поступившим ранее запросом по входам 35, но логические условия уже изменились, либо апросы поступили одновременно, устаовится второй триггер 20 при формиовании подтверждения прерывания, ереключит мультиплексор 20, обеспеит смещение адресов постоянной паяти 6, т.ее. обеспечит реализацию огического прерывания. Если прерывания запрещены программно, триггер 20 никогда не установится, так как будет отсутствовать сигнал подтверждения прерывания, синхронизирующий его.

Второй триггер 20 обнуляется через элемент ИЛИ 1k либо начальным сброт, сом, либо по окончанию логического прерывания, либо удерживается в нулевом состоянии выходом первого триг гера 19.

Второй триггер 20 может быть реализован, например, на стандартно интегральной микросхеме 155ТИ2.

Третий триггер 21 предназначен для формирования запроса на прерывание на соответствующий вход 1.9 микропроцессора 1 при возбуждении его входа данных выходом пятого элемента ИЛИ 16 по синхроимпульсу на входе 1 .} микропроцессора i „ Триггер 21 обнуляется через глемент ИЛИ 16 на чальным способом, либо удерживается в нулевом состоянии при запрете на прерывание. При снятии этого запрета (при обнулении выхода ИЛИ 16), если поступили очередные запросы (активирован выход элемента ИЛИ 15), третий триггер 21 установится в состояние логической единицы по синхроимпульсу выхода 2, и сформирует очередной запрос прерывания,

Третий триггер 21 может быть реализован, например, на стандартных интегральных микросхемах 155ТМ2.

Шинный формирователь 22 предназначен дня выдачи на шину 31 данных кода команды вектора прерывания, име ющегося на выходе мультиплексора 26, при активировании его входа разрешения г ерзым элементом И Г/.

формирователь команды векторного перехода реализуется, путем подключения разрядов входов 7,6,0,1,2 шинного формирователя 22 к положительному полюсу источника питания через ограничительный резистор, как это указано на фиг.К Разряды подключены к выходам, мультиплексора 26. Шинный формирователь 22 может быть реализован, например, на стандартных интегральных микросхемах 585 АП16. Регистр 23 предназначен для записи и хранения кода логических уелоВИЙ входов 3 либо исходного кода, либо кода, об|эаботанного в последнем логическом прер лвании. Информация с входов 3 заносится в регистр 23 задним фронтом сигнала на выходе элемента ИЛИ 13. Регистр 23 обнуляется начальным стробом - выходом 2,6 генератора 2. Регистр 23 выдает хранимый код постоянно на схему 2k сравнения.

Регистр 23 может быть реализован, например , на стандартных интегральных микросхемах 155ИР13.

Схема 24 сравнения предназначена для сравнения текущего кода логических условий на входе 3 с исходным кодом, либо с последним обработанным кодом, хранимым в регистре 23. При несравнении возбуждается ее выход для управления элементом И 18 и триггером 20.

Схема 2 сравнения может быть реализована, например, на стандартных интегральных микросхемах 533СП1.

Приоритетный шифратор 25 предназначен для шифрации с приоритетом обычных запросов на пребывание по входам 35. и формирует на выходах 25.1 код номера устройства, старшего по приоритету из всех устройств, выставивших логические единицы на входах 35. При наличии хотя бы одного запроса на входах 35 возбуждается выход 25.2 приоритетного шифратора 25о Приоритетный шифратор 25 может быть реализован, например, на стандартных интегральных микросхемах 155ИВ1.

Мультиплексор 26 предназначен для подключения к шинному формирователю 22 либо кода устройства (старшего по приоритету) с выходов 25-.1 приоритетного шифратора 25 (обычное прерывание), либо собственно логических условий с входов З (логическое прерывание). Управление адресным входом осуществляется выходом триггера 20. Если он обнулен, то на выход мультиплексора передается информация с выходов 25.1 приоритетного шифратора 25, если установлен - с входов 3.

Мультиплексор 26 может быть реализован, например, на стандарных интегральных микросхемах 155КП1.

Элемент 27 задержки предназ.начен для .задержки сигнала, формируемого на выходе дешифратора 5 адреса памяти,с целью обнуления триггера 20 после надежного считывания микропроцессором 1 адреса возврата в основную программу из логического прерывания, так как эта команда записана в блоке 6 постоянной памяти программ по адресу с единицей в старшем разряде, активируемом выходом второго триггеpa 20, a основная программа располо жена по адресам с нулем в этом стар шем разряде. Когда микропроцессор 1 считает команду возврата (при этом на ее адресе возбуждается выход 5,3 дешифратора 5), начнет операцию по извлечению из стэка адреса возврата (внутренние операции без обращения к памяти), тогда импульс на выходе элемента 27 задержки через элемент ИЛИ И обнулит триггер 20 Элемент 27 задержки может быть реализован, например, на четном коли честве последовательно соединенных инверторов. Вход 28 сброса предназначен для приема сигнала начального сброса системы. Вход 29 готовности предназначен для приема внешнего сигнала готов нос ти (например, с медленных носителей информации при загрузке блока 7 оперативной памяти). Вход 30 захвАта предназначен для приема сигнала захвата, например, с внешних быстродействующих носителей информации для инициирования прямого доступа в память Выход 31 ожидания предназначен дл выдачи сигнала ожидания, если на входе 29 готовности - логический ноль о Информационные входы 32 предназна чены для приема информационных сигналов состояния оборудования, прозеряемых программно без использования прерываний. Информационные выходы 33 предназначены для выдачи управляющих сигналов на исполнительные органы, в том числе и сигналов, (формируемых в обыч ном и логическом прерывании. В обычном прерывании часть этих выходов обнуляет флажки устройств, вызвавших прерывание после их обслуживания. Входы 3 логических условий предназначены для приема логических условий, состояния дискретных датчиков технологического оборудования, изменения которых обрабатываются с исполь ованием логического прерывания о формированием автоматных отображений от этих сигналов. Информация н входах 3 изменяется не быстрее времени выполнения логического прерывания с учетом ожидания окончания обычного прерывания, если оно уже началось. Входы 35 запросов на прерывание предназначены для приема сигналов запроса на прерывание (флажков устройств типа дисплея, клавиатуры, пульта оператора и пр). Устройство выставляет на соответствующем разряде входов 35 логическую единицу триггером, принадлежащим техническим средствам этого устройства, который обнуляется в конце программы обслуживания данного устройства. Устройство для программного управления работает следующим образом Обычное прерывание. В этом режиме устройство программно разрешает прерывания. При этом на выходе 1,10 разрешения прерывания микропроцессора устанавливается логическая единица (фиг.1 и 2). При появлении на входах 35 хотя бы., од ной единицы, на выходе 25о2 приоритетного шифратора устанавливается логическая единица, которая, через элемент ИЛИ 15 устанавливает триггер 21 по синхровходу 2,4, выходной сигнал которого подает на вход 1.9 запроса прерывания микропроцессора 1 логическую единицу. Микропроцессор 1 в последнем такте последнего цикла текущей команды, обнаружив запрос прерывания, устанавливает свой внутренний триггер прерывания-и сбрасывает триггер разрешения прерывания и переходит в цикл обработки прерывания, В связи с этим, на выходе 1,10 устанавливается логический нуль, который по инверсному входу элемента ИЛИ 16 сбрасывает и блокирует триггер 21, запрещая ус тановку по синхровходу 2„4, Код уст-, ройства, сформировашего запрос, устаиовлен на выходе 25,1 приоритетного шифратора 25- После перехода микропроцессора 1 в цикл обработки прерывания в первом его цикле выдается слово состояния в системный контроллер 3 и возбуждается сигнал подтверждения прерывания (INTA на фиг,1 и 2) шины 3.2 управления. Затем возбуждается управляющий сигнал приема (DBIN на фиг.1 и 2) шины 3«2 управления и воз-, буждается выход элемента И 17 акти- . вирующий вход разрешения шинного формирователя 22. С выходов 25о1 через ультиплексор 26 и шинный формироваель 22 на шину 3.1 данных выдается од вектора прерывания (RST на фиг«2) помощью формирователя команды векорного перехода. Далее, микpoJ po1цессор организует запись ,в стек адре са возврата (содержимое счетчика команд: СК на фиг о2) в точку прерванной программы и переходит к выполнению программы по адресу, соответствующему введенному коду вектора прерывания (RST) и снимает сигнал подтверждения. Программа обработки прерывания может включать запись в стек с последующим извлечением информации всех регистров, обработку информации с устройства, вызвавшего его, обязательно - обнуление триггера запроса прерывания этого устройства (с выходов 33 этот триггер относится к внешнему оборудованию и не указан на фиг.1). Поэтому снимается логическая единица с входов 35« выходы 25,2 при оритетного шифратора 25. 3 заключение программно устанавливается внутренний триггер разрешения прерывания микропроцессора 1. поэтому на выходе 1,10 устанавливается логическая единица, и выполняется команда возврата к прерванной программе. Если другое устройство установит на входах 35 логическую единицу,то процесс прерываний повторится аналогично, только в соответствии с новым кодом на выходах 25.1 приоритетного шифратора будет обслужено устройство, вызвавшее прерывание. Если одновременно требуют обслуживания несколько устройств, то на выходе 25.1 приоритетного шифратора будет установлен код старшего по приоритету устройства (старшей единицы) . По окончанию программы обслуживания этого устройства последовательно будут обслужены прерывания от младших по приоритету устройств. Таким образом, обработка обычного прерывания, вызванного флажками внеш них устройств, требующих обслуживания, в предлагаемом устройстве аналогична известной дисциплине прерыва ний в системах програамного управления. Прерывание с формированием автоматных отображений (логическое прерывание). Если одновременно с поступлением запросов на входы 35 (до перехода выхода 1.10 в состояние логического . нуля, или в отсутствие таковых изменится информация на входах 3 логических условий, то на выходе схемы 2 сравнения установится логическая 20 единица по синхроимпульсу выхода 1,8 микропроцессора 1. Так как триггер 19 предварительно установлен (при инициализации) и прерывания разрешены, то по импульсу на выходе 1.8 микропроцессора 1 активируется выход элемента И 18, устанавливающий через элемент ИЛИ 15 триггер 21 по синхроимпульсу выхода 2,k (синхроимпульс выхода 1.8 перекрывает выход 2.4). Если триггер 21 уЛе установлен - чуть раньше поступил сигнал с выхода 25.2 приоритетного шифратора 25, но еще не обнулился выход 1.10 микропроцессора 1, то состояние триггера 21, сформировавшего уже запрос на обычное прерывание от входов 35, не изменится, но обслуживаться будет логическое прерывание. В том случае, если поступил запрос от входов 35, выход 1.10 обьулится и сигнал подтверждения прерывания уже сформировался, то логическое прерывание будет обслужено после обычного прерывания. На фиГоЗ показан вариант одновременного возбуждения элемента И 18 и выхода 25.2 приоритетного шифратора 25. Аналогично триггер 21 формирует запрос прерывания на вход 1,9 микропроцессора 1, далее снимается разрешение с выхода 1.10, триггер 21 обнуляется через элемент И 16 и удерживается в логическом нуле до появления логической единицы на входе 1.10. Далее микропроцессор 1 переходит в цикл обработки прерываний, формируется управляющий сигнал подтверждения прерывания на шине Зо2 управления (iNTA на фиг.З), по которому так как на выходе схемы 2k сравнения единица, устанавливает триггер 20. Триггер 20 переключает мультиплексор 26 и активирует старший разряд адресных входов блока 6 постоянной памяти, который не подключен к шине адреса, т.е. смещение адресного пространства блока 6. Через элемент ИЛИ 13 в регистр 23 записываются новые значения входов 3 логических условий и выход схемы 2k сравнения обнуляется после того, как обнулится триггер 20. Последний удерживается в нулевом состоянии через элемент ИЛИ 14 по его инверсному входу, если триггер 19 обнулен - т.е. логическое прерывание запрещено. Поэтому измененная информация с входов 34 через мультиплексор 26, шинный формирователь 22, вход разрешения которого активирован выходом злемент:а Й17 как описано,поступит на шину 3.1 данных, причем микропроцессор 1 воспринимает ее как вектор прерывания, но в действительности она имеет другой смысл: это не код устройства, старшего по приоритету, а состояние логических условий 36 - т.е, собственно состояние датчиков технологического оборудования. Информацию (измененная, очередное состояние) с датчиков необходимо обработать, т.е. сформировать автоматное отображение - в соответствие с некоторой системой булевых функций или таблицей истинности, которые описывают закон формирования управляющих воздействий на исполнительные органы технологического оборудования Микропроцессор 1 как и ранее, записывает в стек содержимое счетчика команд, адресует в соответствие с вектором прерывания (RST на фиг,3), который представляет собой код логических условий, первую ячейку памяти программы обработки прерывания и выполняет ее, формируя управляющие воздействия в соответствие с заданной системой булевых функций или таблицей истинности. По окончанию этой программы осуществляется вывод управляющего воздействия на выход 33 выполнение команды разрешения прерывания (при этом устанавливается выход 1о10) и возврата в основную программу. На адресах команд возврата (RET4 на фиг.З) в основную программу программ обработки прерываний по входам 3 возбуждается выход 5.3 дешифратора 5, поэтому через элемент 27 задержки, элемент ИЛИ I обнуляется триггер 20. Элемент 27 задержки обес печивает задержку на надежное считывание команды возврата по адресу, учитывающему возбужденный выход триг гера 20. Последний обнуляется и муль типлексор 26 переключается. Микропроцессор 1 выполняет прерванную про грамму. Если во время выполнения про граммы обработки прерываний от входов З поступят запросы на входы 35, это не приведен к повторной установке триггера 21, так как обнулен возбужденным входом асинхронного сброса выходом 1.10 через элемент ИЛИ 16 Эти запросы будут обслужены по окончании обработки сигнала с входов 3 7522 Iпосле перехода в основную программуj. Скорость изменения сигналов на входах 3 такова, что микропроцессор 1 успевает обрабатывать их изменение. Они изменяются не быстрее, чем обрабатывается очередное их изменение и прерывание с входов 35, если оно уже начато, т.е. после установки выхода 1.10 в логическую единицу вновь может быть установлен триггер 21 по синхроимпульсу выхода 2 и вновь начнется обработки простого или логического прерывания. Таким образом, новая введенная дисциплина логического прерывания с формированием,автоматных отображений позволяет ускорить обработку изменения логических условий в соответствие с заданной системой булевых функций или таблицей истинности по сравнению с известным изобретением, в котором логическая обработка (ветвление по значению логических условий) Осуществляется Только в заданной точке программы. В предлагаемой системе изменение значения логических условий сразу же вызывает прерывание, приоритет которого старше приоритетов других устройств (пульта оператора и т.д.) и формирование управляющего воздейстаия на исполнительные органы. При этом микропроцессор 1 формирует переходы по тем же адресам, что и обычном прерывании, а смещение адресного пространства блока 5 для формирования автоматных отображений осуществляется по его старшему разряду выходом мультиплексора 2.6. Если исходное положение входов 3 отлично от нулевого, то программно микропроцессор 1 возбуждает выход 9.3 дешифратора 9 (например, командой вывода по адресу, присвоенного регистру 23) и через элемент ИЛИ 13 с входов З в регистр 23 записывается исходное состояние датчиков. Затем так™ же возбуждается выход 9.2 дешифратора 9 и в триггер 19 с разряда шины 3.1 данных записывается единица, тем самым разрешается новая дисциплина огического прерывания - с формированием автоматных отображений. При необходимости запрета дисциплины анаогично в триггер 19 заносится логиеский ноль, тогда контроллер реагиру т только на обычные прерывания - по входам 35- 2317 Активирование выхода элемента И 18 производится по синхроимпульсу выхода 1.8 микропроцессора 1, т.е,, до анализа микропроцессором 1 наличия прерываний - возбужденного выхода 1.9 которое происходит в последнем такте последнего цикла текущей команды три (синхроимпульс формируется в первом такте). Установка триггера 21 происхо дит по переднему фронту синхроимпульса на выходе 2. тактового генерато ра 2, если не активирован его вход обнуления (в этом случае он удерживается в нуле). Синхроимпульс выхода 1.8, активирующий выход элемента 19 перекрывает тактовый импульс 2,|.

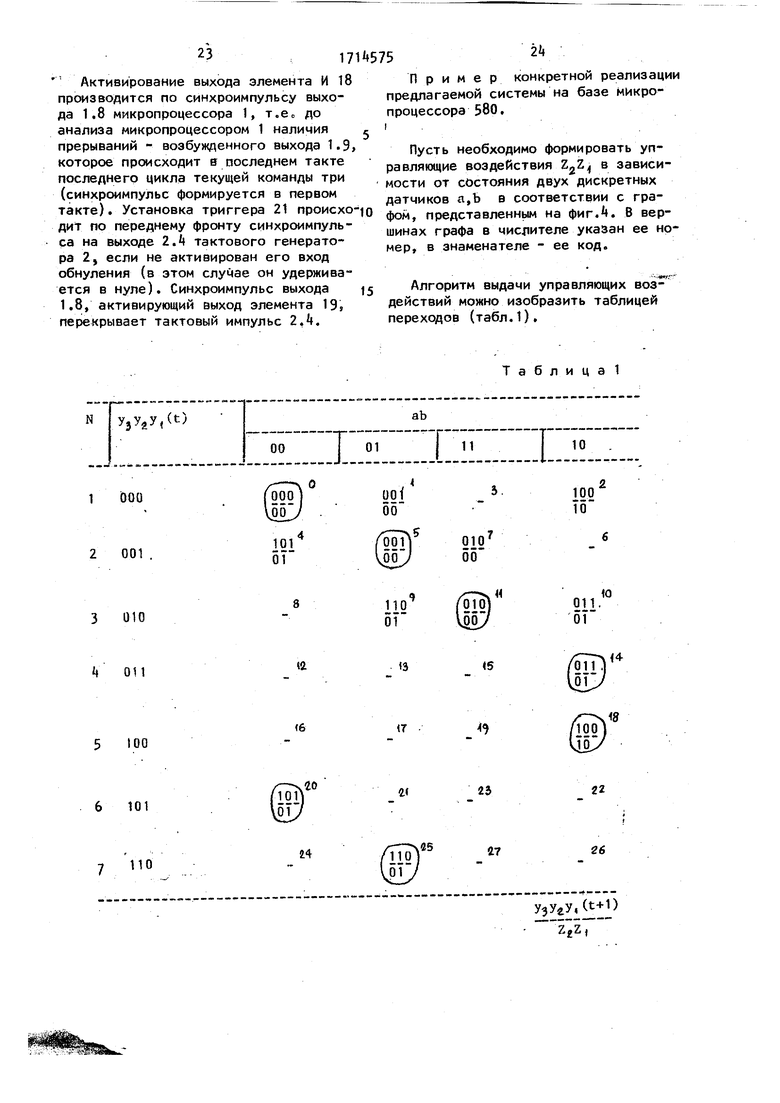

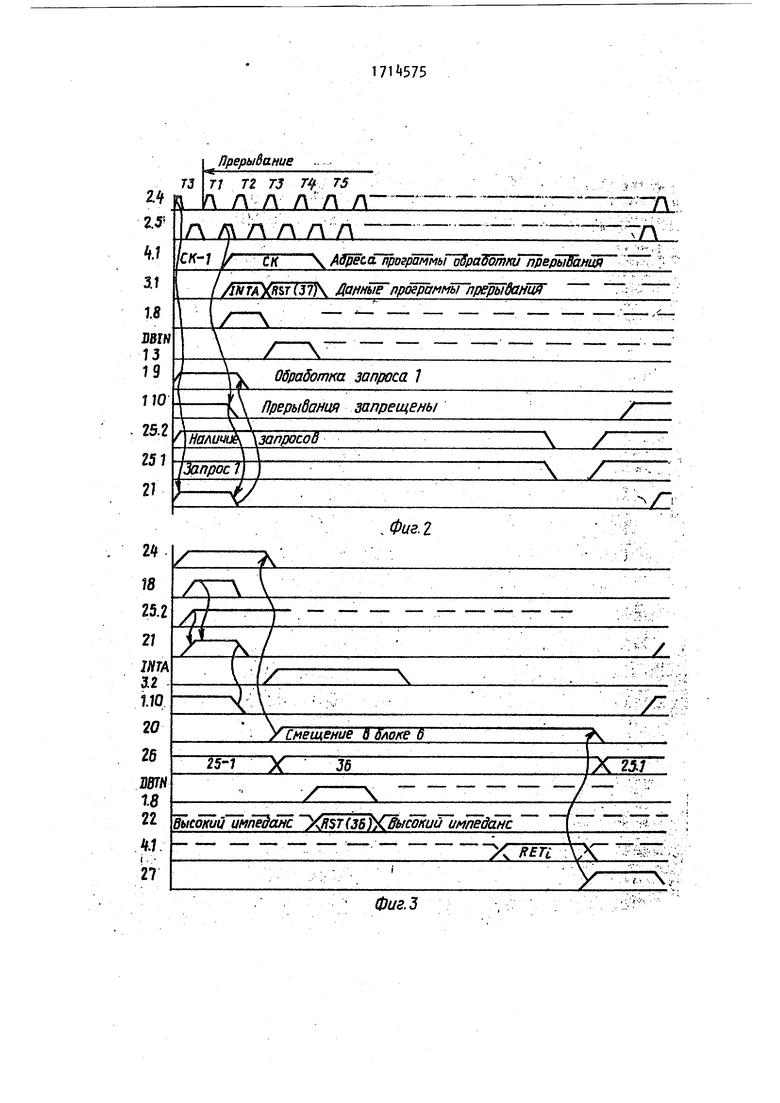

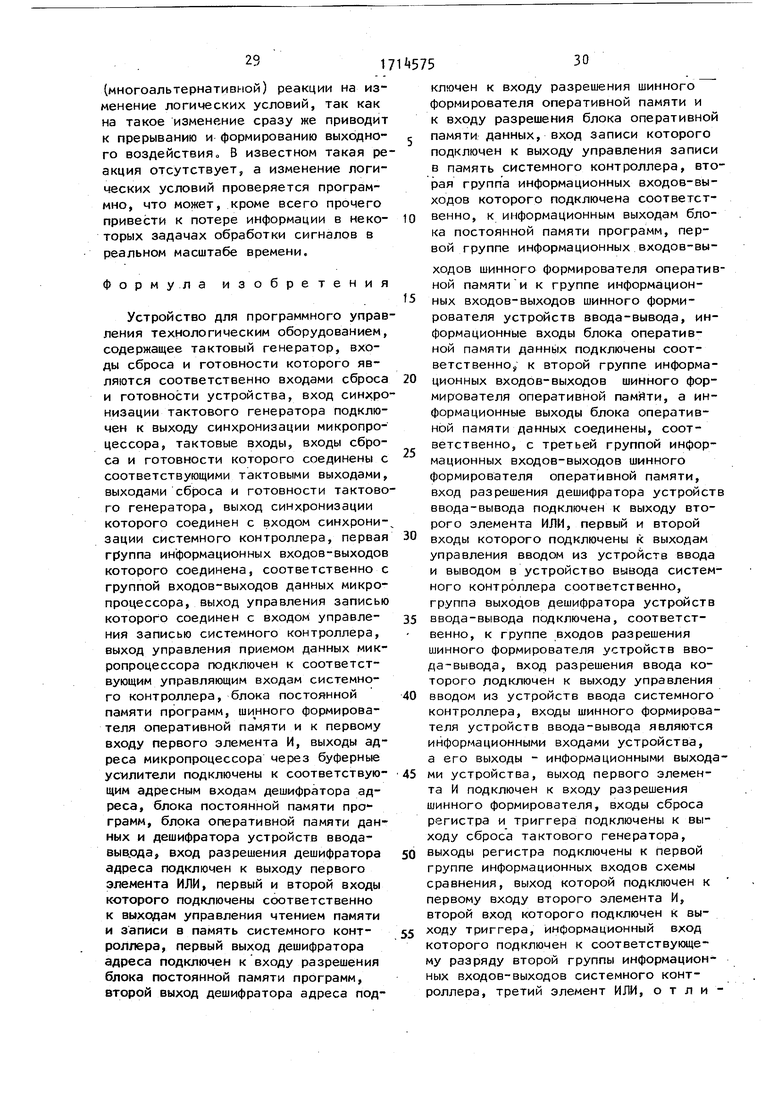

Таблица 1 5 Пример конкретной реализации предлагаемой системы на базе микропроцессора 580. Пусть необходимо формировать управлящие воздействия ZjZ в зависимости от состояния двух дискретных датчиков а,Ь в соответствии с графом, представленнь1м на фиг.. В вершинах графа в числителе указан ее номер, в знаменателе - ее код. -i, Алгоритм выдачи управляющих воздействий можно изобразить таблицей переходов (табл.1).

1 000

2 001

100

То

010

оо

3 010

«2

Ц on

(6

5 too

10

45

8

9

6 101

23

22

г(

г4

; 110

26

47

УзУгУ ;|;;

ZjZ, Здесь УзУгУ (t) текущий код (t+1) вершины ) последующий код вершины графа (фиг.). В исходном положении регистр 23 (фиг,1) об нулен по входу сброса. Если бы исхо ное состояние датчиков аЬ отличалос от нулевого, то этот исходный код в регистре 23 был бы занесен при прог раммном возбуждении выхода 9-3 дешифратора 9 (инициализации) через элемент ИЛИ 13 При этом также на у равляю1цие органы выводится соответствующий код 00 (клетка О табл.1). Табл.1 построена для допущения невозможности одновременного изменени состояния сразу двух датчиков аЬ Таблица 1 имеется в постоянной памяти блока 6 системы по адресам, им ющим самую старшую единицу (А1 блоj ка 6 на фиг.1), I Тогда при реакции системы на изме нение состояния датчиков аЬ 00- 01 управление будет передано командой :RST 11001111 (третий разряд кода djdgd, команды RST 11 111 подключен к минусовой шине счетчика питания (а остальные разряды 7,6,2, 1,0 - к плюсовой шине) - на входах 3 восьми ячейкам памяти с адресами (в восьмеричном коде), oiooiOg- 010173 Здесь самая левая единица означает возбуждение входа А1 блока 6 выходом триггера 20. В случае реакции на запросы по входам 35 на этом разряже будет 0. В указанных восьми ячейках записаны команды: BOOL 1: PUSH PSW; сохранение сло ва состояния MVI C,01Hj присвоение регистру С кода аЬ CALL UPR; вызов подпрограммы формировани ZgZ, (UPR) FOP PSW; возврат слова состояния RET; возврат к прерванной программе, Подпрограмма выдачи управляющих воздействий UPR представляет собой следующую последовательность команд: UPR: PUSH Н; сохранить H,L PUSH В; сохранить В,С LDA РАМ; чтение из ячейки РА кода УзУ2У1(ь) ORA С, ; конкатенация для полу чения адреса () MVI Н,57; присвоение регистру Н кода 57 1 5 MOV L,C ; пересылка L-«-C, в H,L - адрес клетки 1 таблицы 1 MOV А,М ; пересылать в аккумулятор (t+D/XZ Z,, находящиеся по адресу H,L MOV В,А ; временно хранить (t+1)//Z2 Z, в В MOV А,В ; переслать в А ANI MASK 1 ; выделить . OUT PORT 1;вывести Z2Z в порт 1 MOV А, В переслать , (t+1)// ANIMASK2 , в А, выделить УзУгУИ +) STA РАМ записать новое состояние в ячейку РАМ ; восстановить В, С ; восстановить H,L разрешение прерывания возврэт (к команде POP PSW) о Таким образом, подпрограмма UPR осуществляет автоматное отображение в соответствии с табл.1. Перед обращением к ней код датчиков аЬ (логических условий входа 3) записан в регистре С (микропроцессора 1), этот код контактенируется с кодом, хранящемся в ячейке РАМ (состояние ( табл.), по этому адресу УзУг.У«()аЬ извлекается информация (t+1) , (конкатенация числителя и знаменателя дроби (t+1) ,- , I, таОл.1). Часть этой информации - выходное воздействие выделяется маской MASK 1, содержащей единицы в разрядах и нули в ост . тальных разрядах, и выводится в порт 1 (выходы 33). Другая часть ,(t4-l) - последующее состояние вершины графа - выделяется маской MASK 2, содержащей единицы в разрядах (t+1) и нули в остальных разрядах и записывается в ячейку РАМ т.е. осуществляется переход во вторую вершину графа (фиГоА). При очередных измерениях состояия датчиков аЬ,например, 01-) Оо о« удет осуществляться продвижение по рафу в вершины 3 и 4. При этом буут формироваться команды RST, адреуемые ячейки с последовательностями; оманд, аналогичных BOOL 1,только рисвоение регистру С производится в оответствии с состоянием аЬ . 1,10... При переходе из состояния три в состояние четыре формируется управляющее воздействие 01. Обнуление триггера 20, осуществляющего смещение постоянной памяти блока 6 происходит по адресам команд RET (помечена звездочкой -tr в подпрограмме BOOL 1}, вызываемых командами RST 317, RST 327, RST 337. При этом возбуждается выход 5.3 дешифратора 5 и триггер 20 обнуляется через элемент 27 задержки;тогда, когда эти команды RET уже выполнены и произошел возврат в основную программу, прерванную прерыванием. Следует под черкнуть, что команда RST вынуждает микропроцессор 1 генерировать одни и те же адреса векторов прерываний как по входам 3, так и по входам 35 а разделение этих векторой происходит возбужденным выходом триггера 20 смещающим адреса постоянной памяти блока 6 (вход А1 блока 6 на фиг,1)с Снятие смещения произойдет после выполнения команды RET - возврата в ос новную программу - т се., после ее надежного считывания в микропроцессор 1 из блока 6 со смещением и даль нейшее считывание микропроцессором команд будет осуществляться при снятом смещении. Для реализации последовательностного автомата (фиГо) в известном изобретениинеобходима такая же программа UPR. Имеется также возможность реализации комбинационной логики более простым, чем описанная последовательность способом

Входы 3 контроллера подключены к фотоэлектрическим датчикам аЪс преоб1

ма по сравнению с известным обладает большим быстродействием векторной 5 разователя вал-код. Необходимо сформировать позиционный код ,, Для простоты считают, что код XjXjX просто выводится на некоторый выходной порт для дальнейшей обработки. Тогда после обнуления в регистре 23 - нулевой код. При поступлении кода аЬс 001 формируется прерывание командой RST 317. Адресуется ячейка памяти блока 6 с адресом, содержащим крайнюю левую единицу, как было описано выше:01001 Оg. В восьми ячейках 01 OOlOg-OIOOU записаны команды: GRAY 1: PUSH PSW сохранение слова состояния, MUI A,001; присвоение аккумулятору значения Х,Х2Х 001 OUT PORT 2; вывод возврат PSW POP PSW; разрешение прерывания, возврат В регистр 23 через элемент ИЛИ 13 записывается новое значение входного сигнала после обнуления триггера 20« После выдачи по сигналу аЬс 100 кодй x-jXj x 111 при поступлении сигнала аЬс 000, формируется команда RST 307 и выводится .код , 000, Предполагается, что внешними средствами, не указанными на фиго1 инициируется начальный запуск, старт микропроцессора с некоторого ненулевого 291 (многоальтернативиой) реакции на изменение логических условий, так как на такое изменение сразу же приводит к прерыванию и формированию выходного воздействия о В известном такая ре акция отсутствует, а изменение логических условий проверяется программно, что может, кроме всего прочего привести к потере информации в некоторых задачах обработки сигналов в реальном масштабе времени. формула изобретения Устройство для программного управ ления технологическим оборудованием, содержащее тактовый генератор, входы сброса и готовности которого являются соответственно входами сброса и готовности устройства, вход синхро низации тактового генератора подключен к выходу синхронизации микропроцессора, тактовые входы, входы сброса и готовности которого соединены с соответствующими тактовыми выходами, выходами сброса и готовности тактово го генератора, выход синхронизации которого соединен с входом синхронизации системного контроллера, первая группа информационных входов-выходов которого соединена, соответственно с группой входов-выходов данных микропроцессора, выход управления записью которого соединен с входом управления записью системного контроллера, выход управления приемом данных микропроцессора подключен к соответствующим управляющим входам системного контроллера, блока постоянной памяти программ, ши нного формирователя оперативной памяти и к первому входу первого элемента И, выходы адреса микропроцессора через буферные усмлители подключены к соответствующим адресным входам дешифратора адреса, блока постоянной памяти программ, блока оперативной памяти данных и дешифратора устройств вводавыврда, вход разрешения дешифратора адреса подключен к выходу первого элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам управления чтением памяти и записи в память системного контроллера, первый выход дешифратора адреса подключен к входу разрешения блока постоянной памяти программ, второй выход дешифратора адреса под5ключен к входу разрешения шинного формирователя оперативной памяти и к входу разрешения блока оперативной памяти данных, вход записи которого подключен к выходу управления записи в память системного контроллера, вторая группа информационных входов-выходов которого подключена соответственно, к информационным выходам блока постоянной памяти программ, первой группе информационных входов-выходов шинного формирователя оперативной памяти и к группе информационных входов-выходов шинного формирователя устройств ввода-вывода, информационные входы блока оперативной памяти данных подключены соответственно, к второй группе информационных входов-выходов шинного формирователя оперативной памйти, а информационные выходы блока оперативной памяти данных соединены, соответственно, с третьей группой информационных входов-выходов шинного формирователя оперативной памяти, вход разрешения дешифратора устройств ввода-вывода подключен к выходу второго элемента ИЛИ, первый и второй входы которого подключены к выходам управления вводом из устройств ввода и выводом в устройство вывода системного контроллера соответственно, группа выходов дешифратора устройств ввода-вывода подключена, соответственно, к группе входов разрешения шинного формирователя устройств ввода-вывода, вход разрешения ввода которого подключен к выходу управления вводом из устройств ввода системного контроллера, входы шинного формирователя устройств ввода-вывода являются информационными входами устройства, а его выходы - информационными выходами устройства, выход первого элемента И подключен к входу разрешения шинного формирователя, входы сброса регистра и триггера подключены к выходу сброса тактового генератора, выходы регистра подключены к первой группе информационных входов схемы равнения, выход которой подключен к ервому входу второго элемента И, второй вход которого подключен к выоду триггера, информационный вход оторого подключен к соответствующеу разряду второй группы информационых входов-выходов системного контоллера, третий элемент ИЛИ, о т л и чающееся тем, что, с целью повышения быстродействия и расширения области применения в устройство дополнительно введены три элемента ИЛИ, два триггера, приоритетный шифратор, мультиплексор и элемент задержки, причем вход синхронизации регистра подключен к выходу третьего эле-. мента ИЛИ, первый вход которого подключей к второму выходу дешифратора устройств ввода-вывода, а второй вход - к выходу jBTOporo триггера, к адресному входу мультиплексора,старшему адресному входу блока постоянной памяти программ и дополнительному информационному входу дешифратора памяти,третий выход дешифратора адреса подключен к входу элемента задержки, выход которого подключен к первому V входу четвертого элемента ИЛИ,второй инверсный вход четвертого элемента ИЛИ подключен к выходу первого триггера третий вход метвертого элемента ИЛИ подключен к входу сброса второго триггера, вьход четвертого элемента ИЛИ подключен к входу сброса второго триггера, информацио.нный вход которого подключен к выходу схемы сравнения, а вход синхронизации которого подключен к выходу подтверждения прерывания системного контроллера, вход синхронизации первого триггера подключен к третьему входу дешифратора устройств ввода-вывода, информационныё входы регистра подключены, соответственно, к второй группе информационных входов схемы сравнения и к второй группе входов мультиплексора и являются входами логических

условий устройства, второй вход первого элемента И подключен к выходу подтверждения прерывания системного контроллера, третий вход второго элемента И подключен к выходу синхронизации микропроцессора, а четвертый вход второго элемента И подключен к выходу разрешения прерывания микропроцессора, выход второго элемента И подключен к первому, входу пятого элемента ИЛИ, второй вход которого подключен к выходу управления приоритетного шифратора, входы приоритетного шифратора являются входами запросов на прерывание устройства, информационные выходы приоритетного шифратора подключены к первой группе входов мультиплексора, выходы которого подключены к первой группе информационных входов шинного формирователя, к второй группе информационных входов которого подключены выходы формирователя команды векторного перехода, выход пятого элемента ИЛИ подключен к входу данны третьего триггера, вход сброса кото рого подключен к выходу шестого элемента ИЛИ, первый, инверсный вход шетого элемента ИЛИ подключен к выходу разрешения прерывания микропроцессора, второй вход шестого элемента ИЛИ подключен к выходу сброса тактового генератора, выход третьего триггера подключен к входу запроса прерывания микропроцессора, вход синхронизации третьего триггера подключен к соответствующему тактовому выходу тактового генератора.

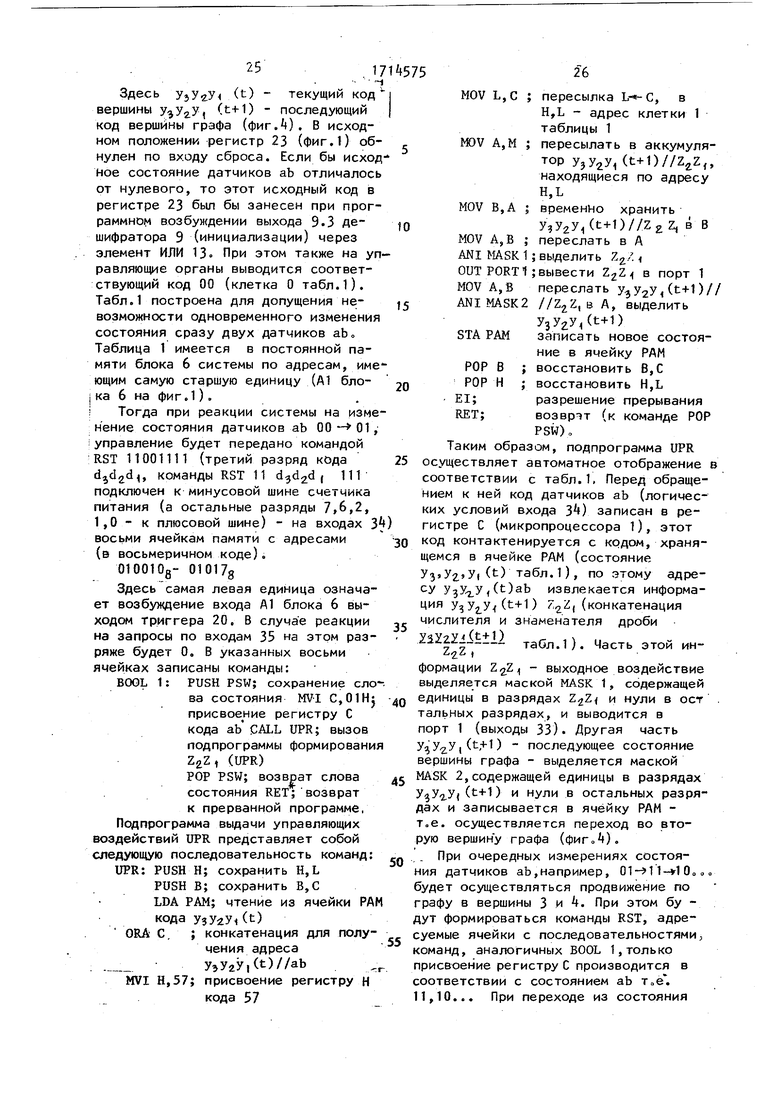

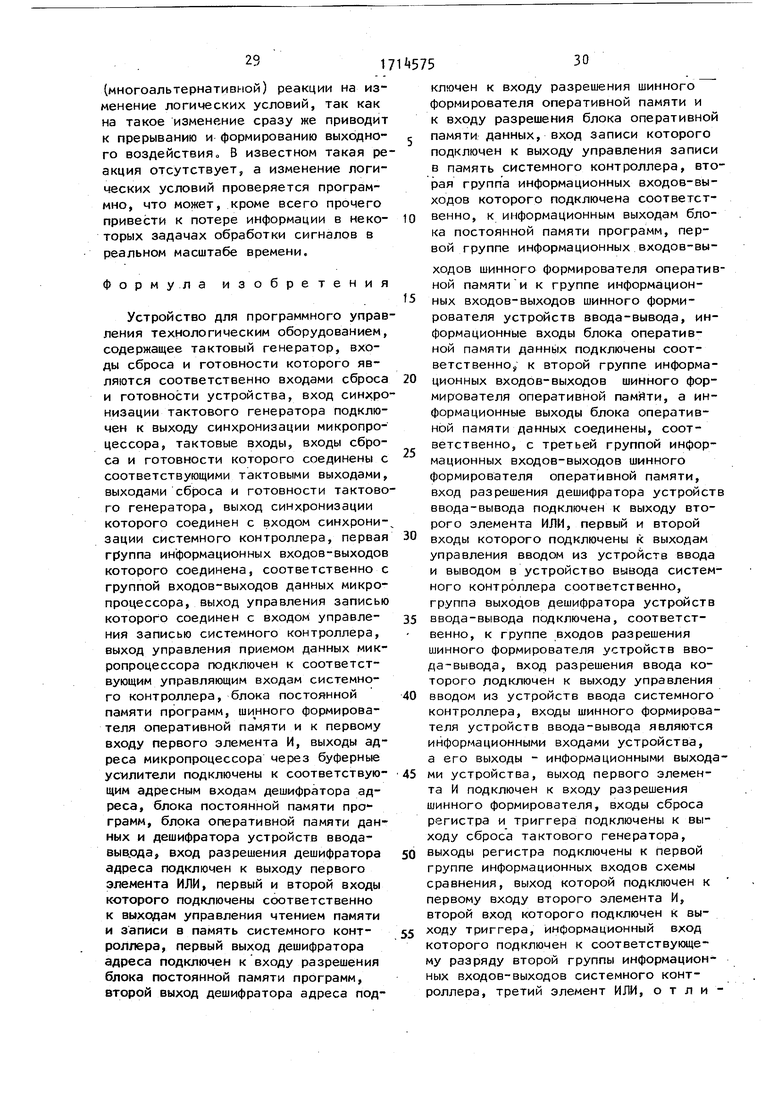

Прерывание it; TZ ТЗ 7J

гз

j -Yir ASpscir i03p прерыШмия

MaHfffiie-npoepa MbrnpepSi8affW

Обработка eanixica 1 Прерыбания Зипрещены запроса -, I -i

-.1.1--

II11 I -

-

.Фиг. г

фиг.З

Фав4

| Устройство программного управления | 1981 |

|

SU1012205A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| - М.: Радио и связь, 198^.Коффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| - М.: Мир, 1983. | |||

Авторы

Даты

1992-02-23—Публикация

1989-05-03—Подача