1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств дискретной автоматики и ЦВМ.

Известны прямоугольные дешифраторы, содержащие входные кодовые шины, логические схемы формирования выходных сигналов на транзисторных элементах «ИЛИ-НЕ и выходные шины. Питание подобных дешифраторов осуществляется от источника питания через общую шину.

Недостатком этих дешифраторов является относительно большая мощность рассеивания, вызванная тем, что при работе дешифратора выбирается только одна выходная шина и при этом у связанной с этой выходной шиной логической схемы фор.ми1рова«ия выходных сигналов ВСе элементы закрыты, а мощность рассеивается .на (rt-1) логических схе.мах формирования 1выходных сигналов, элементы которых в это время открыты. Надежность работы таких дешиф ратО|ров невысока, так как Именно открытые элементы «ИЛИ-НЕ наиболее подвержены отказам.

Целью изобретения являются уменьгиение рассеиваемой мощности и повышение надежности работы дешифраторов.

Эта цель достигается тем, что в дешифратор введены т схем «ИЛИ, каждая из которых соединена входами с ki выходами одной из групп логических схем формирования выходных сигналов, т триггеров, одни из входов которых связаны с выходами схем «ИЛИ, а

другие - с шиной сброса, т ключей коммутации питания, вход каждого из которых подключен к выходу соответствующего триггера, а выход - к шине питания логических схем формирования выходных сигналов той же

группы.

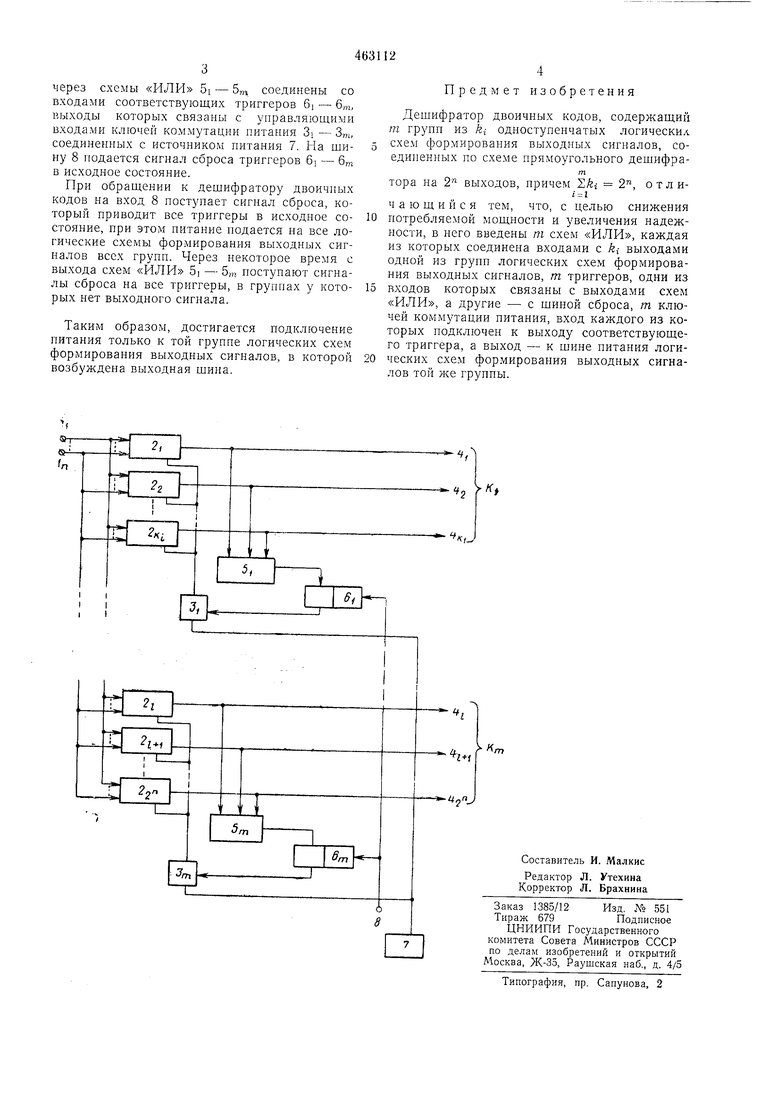

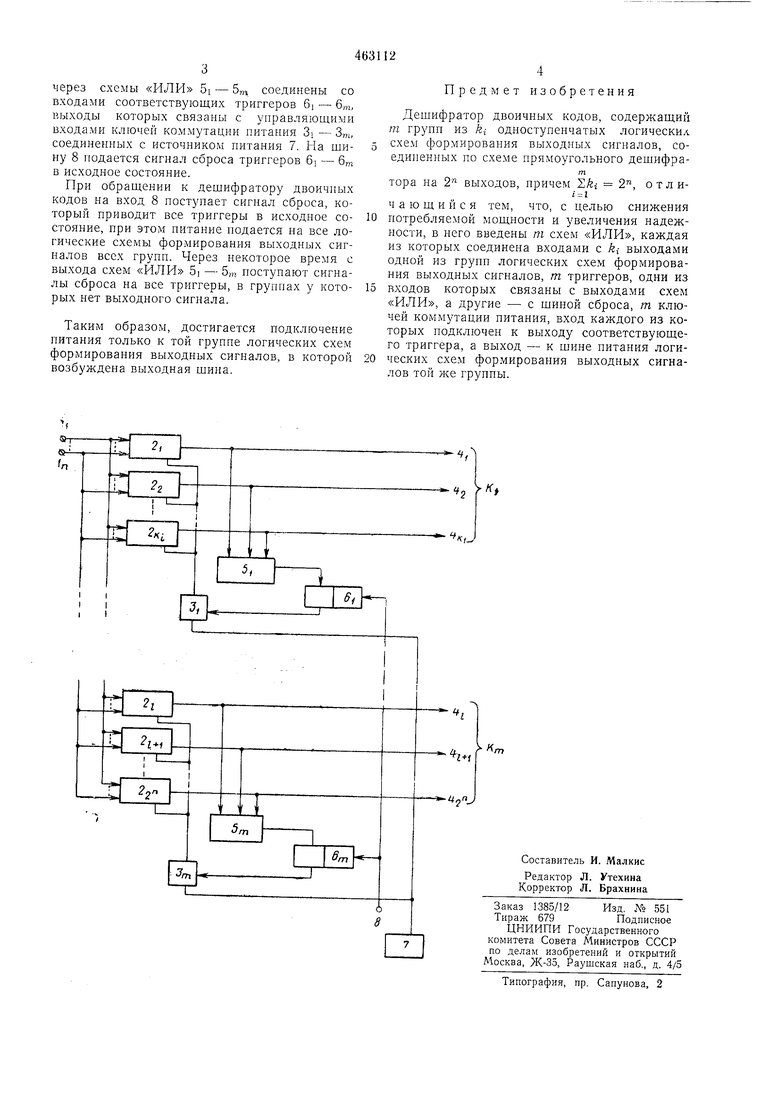

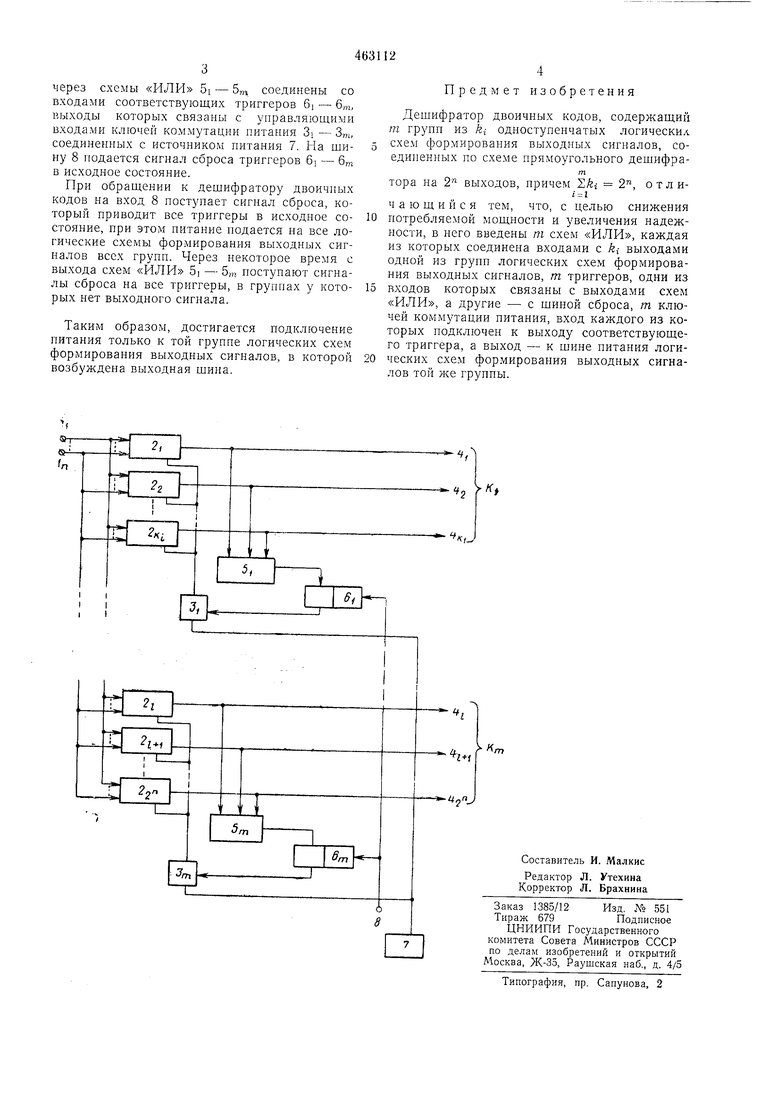

Структурная схема дешифратора двоичных кодов представлена на чертеже.

Входные кодовые шины соединены со входами логических схем формирования выходных сигналов 2i-2,. Эти схемы объединены в т групп по ki схем в каждой. Значение величины т и ki определяется требуемой экономией мощности, причем необходимо выт

иолнение соотношения Z/ej 2. В частном

Ь:1

случае, когда число логических схем формирования выходных сигналов во всех т группах равно, имеет место соотношение m-k 2.

Питание каждой группы логических схем формирования выходных сигналов осуществляется через ключи коммутации питания 3,-Зщ. Выходы логических схем формирования выходных сигиалов (4; - 4уг) в группе через схемы «ИЛИ 5i - 5m соединены со входами соответствующих триггеров 6i - 6m, выходы которых связаны с управляющими входами ключей коммутации питания 3i - 3т, соединенных с источником питания 7. На щину 8 подается сигнал сброса триггеров 6 - 6т в исходное состояние. При обращении к дещифратору двоичных кодов на вход 8 поступает сигнал сброса, который приводит все триггеры в исходное состояние, при этом нитание подается на все логические схемы формирования выходных сигналов всех грунп. Через некоторое время с выхода схем «ИЛИ 5i - 5,п поступают сигналы сброса на все триггеры, в группах у которых нет выходного сигнала. Таким образом, достигается подключение питания только к той группе логических схем формирования выходных сигналов, в которой возбуждена выходная шина. 4 Предмет изобретения Дещифратор двоичных кодов, содержащий т групп из k-i одноступенчатых логическил схем формирования выходных сигналов, соединенных по схеме прямоугольного дещифратора на 2 выходов, причем Ийг 2, отличающийся тем, что, с целью снижения потребляемой мощности и увеличения надежности, в него введены т схем «ИЛИ, каждая из которых соединена входами с ki выходами одной из групп логических схем формирования выходных сигналов, т. триггеров, одни из входов которых связаны с выходами схем «ИЛИ, а другие - с щиной сброса, т ключей коммутации нитання, вход каждого из которых подключен к выходу соответствующего триггера, а выход - к щине питания логических схем формирования выходных сигналов той же группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ШИРОТНО-ИМПУЛЬСНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1973 |

|

SU366540A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

| Устройство для индикации | 1985 |

|

SU1310886A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| Дискретное измерительное устройство ДИУ-256/1 с цифровым выходом | 1959 |

|

SU124650A1 |

| Генератор пачек импульсов | 1979 |

|

SU834847A1 |

| Устройство для индикации | 1977 |

|

SU811324A1 |

| Способ для циклического опроса рассредоточенных объектов | 1974 |

|

SU519753A1 |

Авторы

Даты

1975-03-05—Публикация

1971-09-21—Подача