1

Изобретение относится к вычислительной технике и может быть использовано в телекоммуникационных вычислительных системах.

Цель изобретения - повышение быстродействия путем сокращения времени передачи информации.

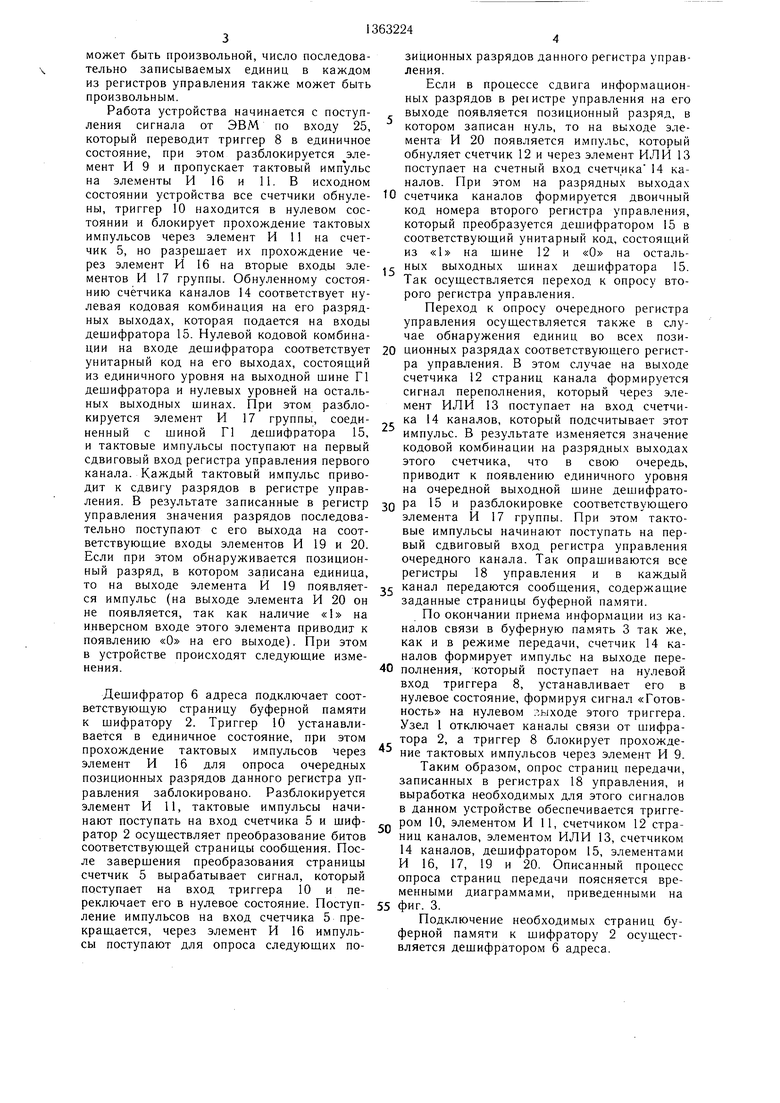

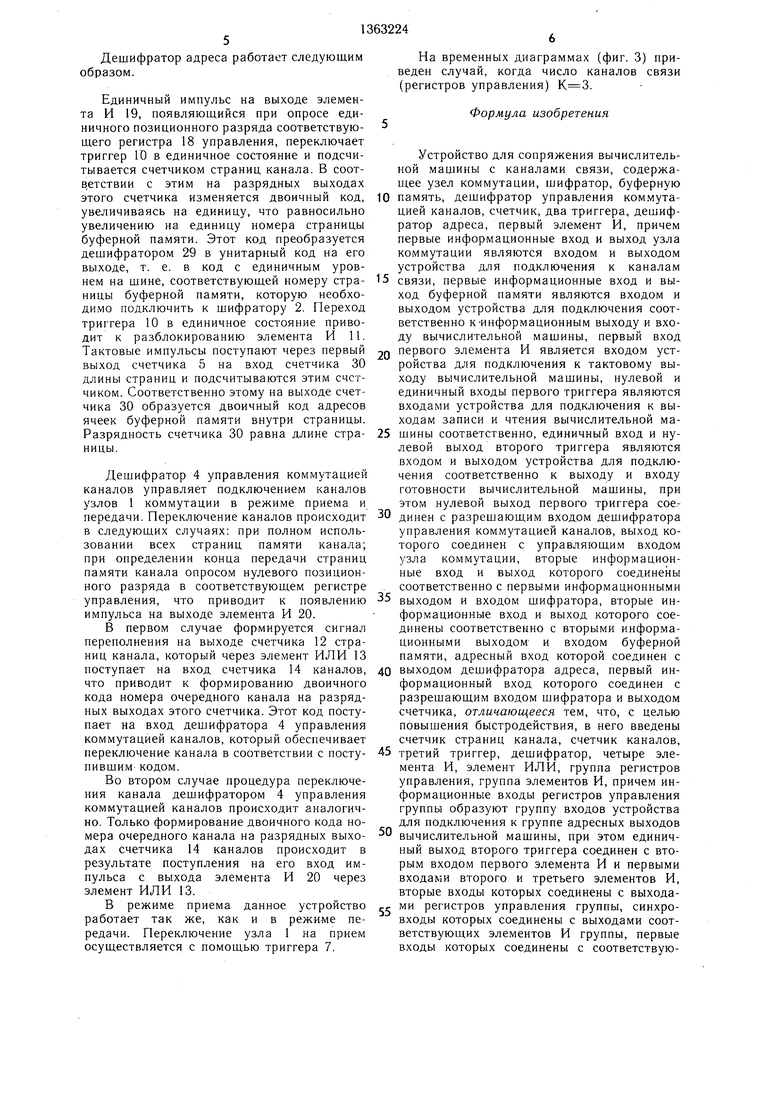

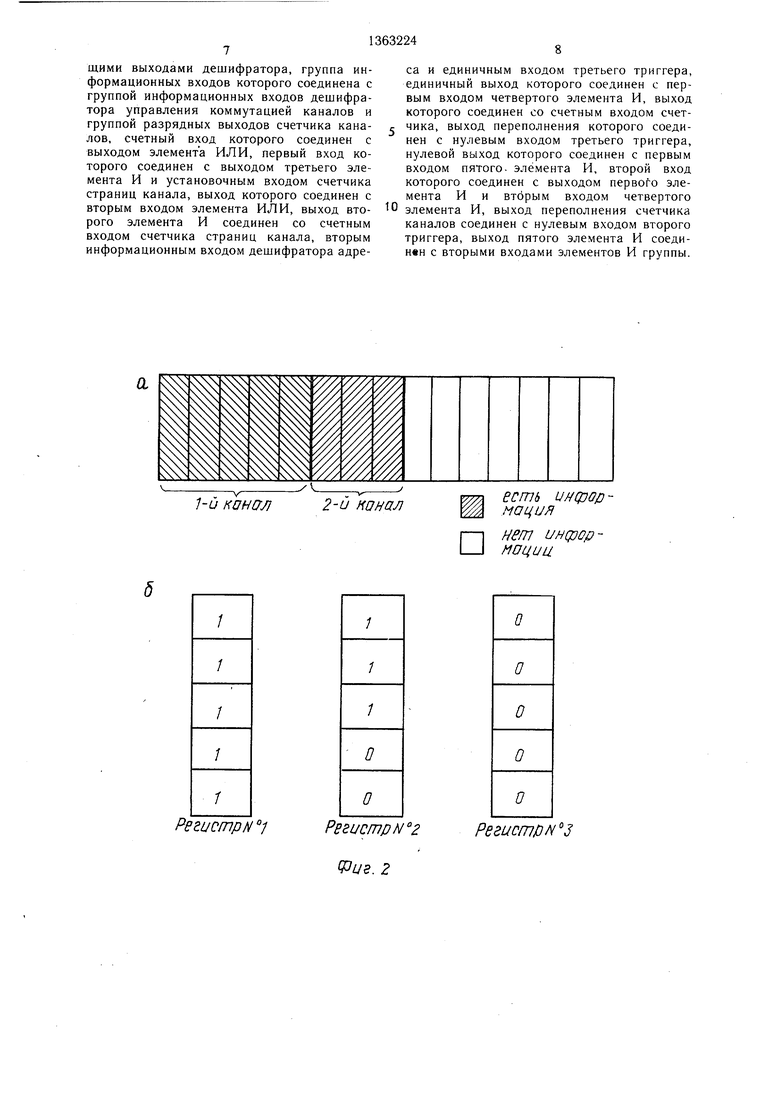

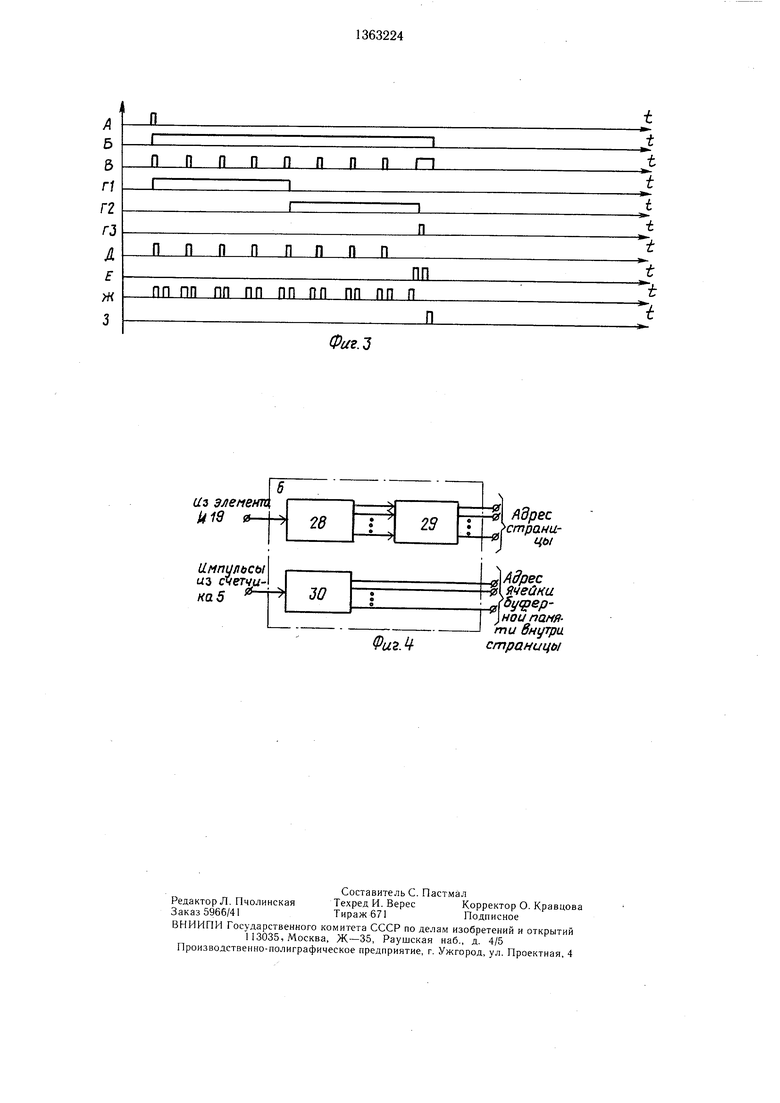

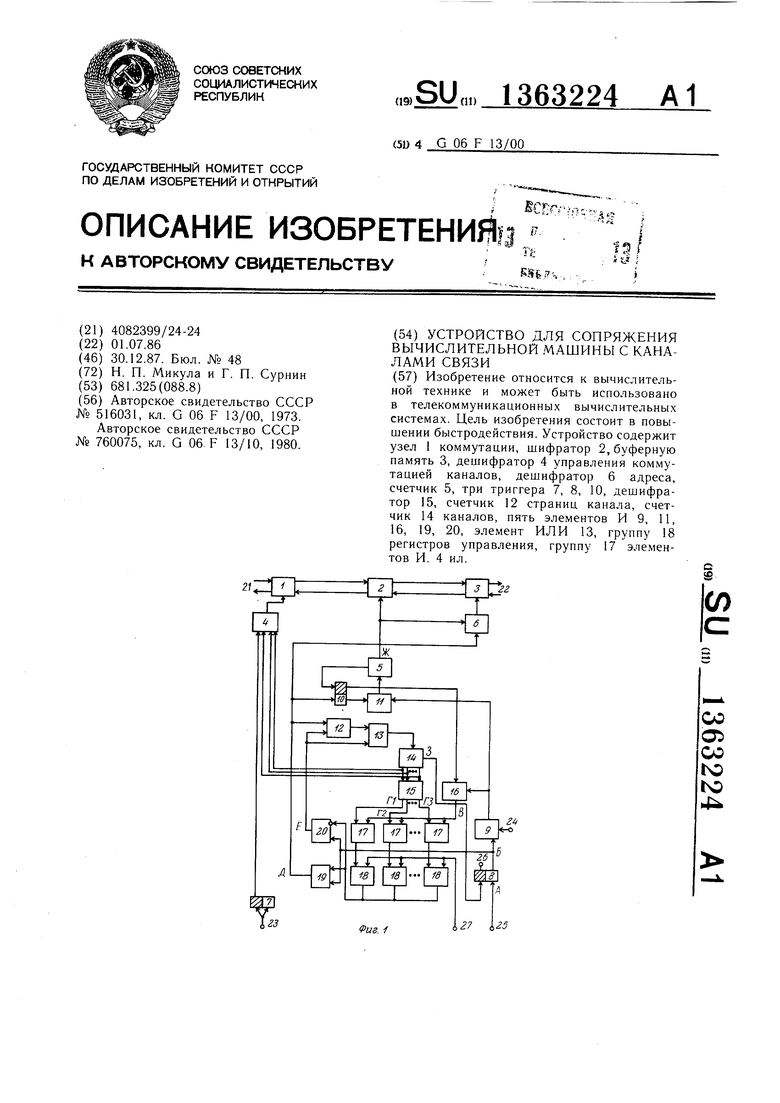

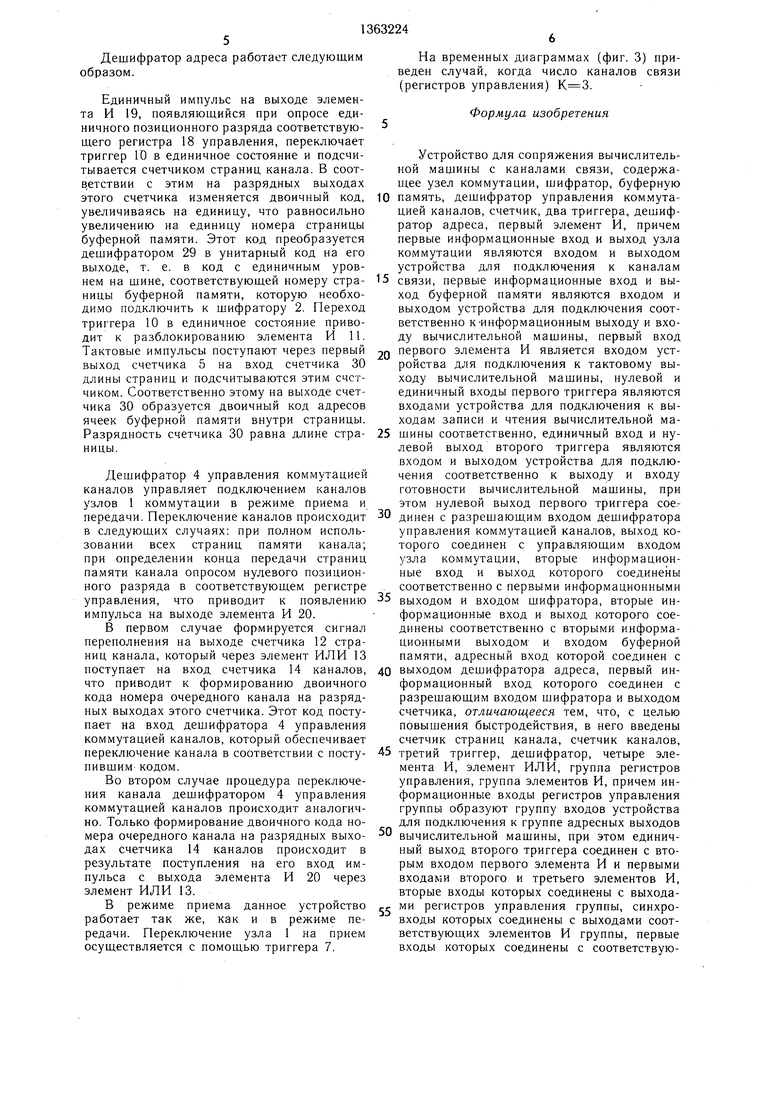

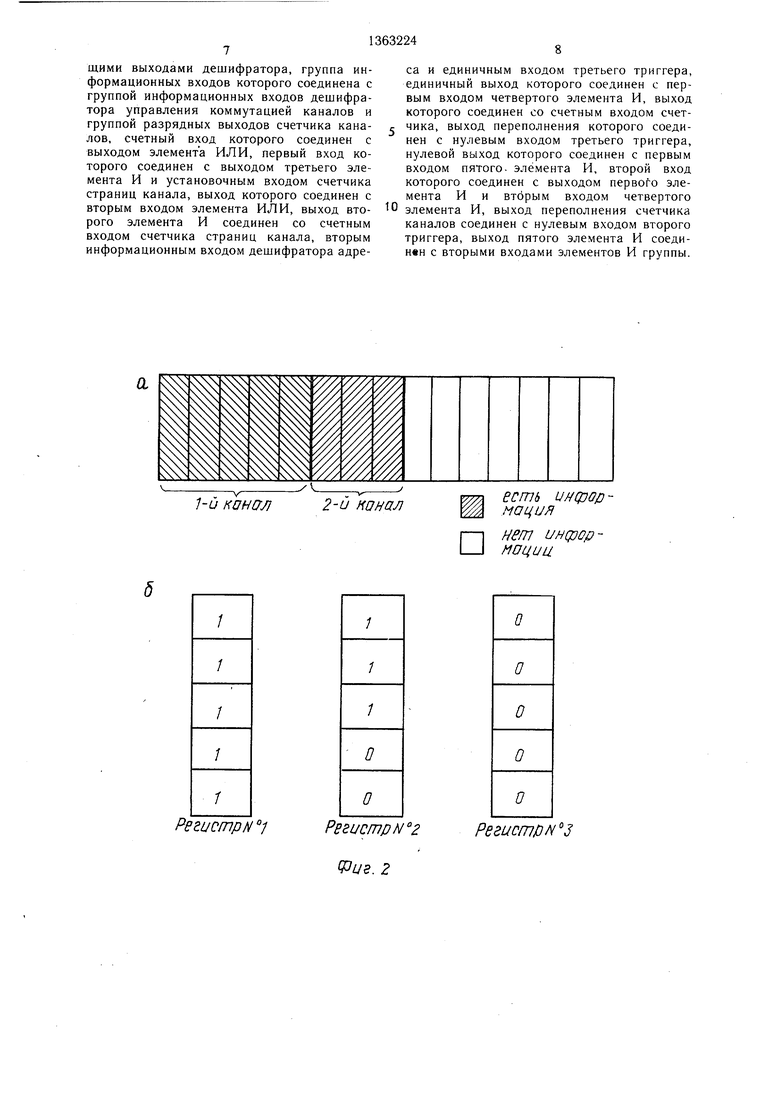

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - длина сообщения в страницах, содержащихся в буферной памяти (а) и кодорежиме обмена в регистрах управления (б); на фиг. 3 - временная диаграмма работы устройства; на фиг. 4 - схема дешифратора адреса.

Устройство содержит узел 1 коммутации, шифратор 2, буферную память 3, дешифратор 4 управления коммутацией каналов, счетчик 5,- дешифратор 6 адреса, триггеры 7 и 8, элемент И 9, триггер 10, элемент И 11, счетчик 12 страниц канала, элемент ИЛИ 13, счетчик 14 каналов, дешифратор 15, элемент И 16, группу элементов И 17, группу регистров 18 управления, элементы И 19 и И 20 и входы и выходы (шины) 21-27 устройства.

Дешифратор адреса содержит счетчик 28 страниц памяти, дешифратор 29 страниц памяти и счетчик 30 длины страницы.

Узел 1 коммутации служит для подключения каналов связи к шифратору 2 в режимах приема и передачи информации. Шифратор 2 предназначен для преобразования битов сообщения по тактовым импульсам, поступающим со счетчика 5. Буферная память 3 служит для хранения информации обмена, представленной в страничной форме.

Дешифратор 4 управления коммутацией каналов управляет работой узла 1 в соответствии с сигналами, поступающими с триггера 7 и счетчика 14 каналов. Счетчик 5 формирует тактовые импульсы, поступающие на входы шифратора 2 и дешифратора 6 адреса, и задает длину страниц путем выработки сигналов для переключения триггера 10. Дешифратор 6 адреса служит для подключения необходимой страницы буферной памяти. Триггер 7 формирует сигнал задания режима работы устройства «Прием. Триггер 8 служит для выработки сигналов разрешения прохождения тактовых импульсов через элемент И 9 в случае поступления соответствующего сигнала от ЭВМ по шине 25. Элемент И 9 управляет прохождением тактовых импульсов, поступающих от источника тактовых импульсов по входной шине 24. Триггер 10 служит для выработки сигналов разрешения прохождения тактовых импульсов через элемент И 11 или через элемент И 16. Элемент И 11 предназначен для управления прохождением тактовых импульсов на вход счетчика 5. Счетчик 12 страниц канала служит для формирования сигнала завершения опроса каждого из регистров

18 управления, если длина сообщения в страницах, переданного в канал связи, равна разрядности соответствующего регистра управления, т. е. при полном исполь- зовании всех страниц памяти канала.

Элемент ИЛИ 13 используется для сборки сигналов, снимаемых со счетчика 12 страниц канала и с элемента И 20. Счетчик 14 каналов служит для формирования кодов номеров опрашиваемых регистров 18

0

управления, или кодов номеров каналов и

5

выработки сигнала завершения обмена информацией по всем каналам связи, подаваемого на нулевой вход триггера 8. Дешифратор 15 преобразует код счетчика 14

каналов в унитарный код, обеспечивая таким образом подключение соответствующего регистра 18 управления группы для опроса импульсами, поступающими от источника тактовых импульсов через вход 24, элемент И 16 и соответствующий элемент

0 И 17.

Элемент И 16 служит для управления прохождением импульсов от элемента И 9. Группа элементов И 17 предназначена для управления прохождением импульсов опроса на вход соответствующего регистра 18 управления группы, определяемого раз- решаюшим сигналом на одном из выходов дешифратора 15. Группа регистров 18 управления обеспечивает хранение информации о длине сообщений в страницах,

Q хранящихся в буферной памяти. Число регистров управления равно числу каналов связи. Элемент И 19 служит для выработки импульса в случае опроса разрядов регистров 18 управления, в которых записаны единицы, элемент И 20 - для выраС ботки импульса в случае опроса первого разряда каждого из регистров 18 управления, в который записан нуль.

Устройство работает следующим образом. Каждый из группы регистров 18 управления соответствует определенному номеру

0 канала связи, т. е. номер регистра управления в группе совпадает с номером соответствующего канала, а каждому единичному позиционному разряду соответствует определенная страница в буферной памя5 ™

При записи информации о режиме обмена в каждый из регистров 18 управления записывается код, определяющий режим обмена соответствующих каналов связи.

0 Если, например, в буферной памяти 3 содержится Н страниц для каждого из К каналов связи, то число регистров управления должно быть К, разрядность каждого регистра управления Н, причем каждый из регистров 18 управления выделяется уз5 лом 1 как принадлежащий к режиму обмена только в одном канале. Учитывая, что длина сообщений в страницах, передаваемая по различным каналам связи.

может быть произвольной, число последовательно записываемых единиц в каждом из регистров управления также может быть произвольным.

Работа устройства начинается с поступления сигнала от ЭВМ по входу 25, который переводит триггер 8 в единичное состояние, при этом разблокируется элемент И 9 и пропускает тактовый импульс на элементы И 16 и 11. В исходном

зиционных разрядов данного регистра управления.

Если в процессе сдвига информационных разрядов в ре истре управления на его выходе появляется позиционный разряд, в котором записан нуль, то на выходе элемента И 20 появляется импульс, который обнуляет счетчик 12 и через элемент ИЛИ 13 поступает на счетный вход счетчика 14 каналов. При этом на разрядных выходах

соответствующий унитарный код, состоящий из «1 на щине 12 и «О на осталь25

состоянии устройства все счетчики обнуле- Ю счетчика каналов фор.мируется двоичный ны, триггер 10 находится в нулевом сое- код номера второго регистра управления, тоянии и блокирует прохождение тактовых который преобразуется дещифратором 15 в импульсов через элемент И 11 на счетчик 5, но разрешает их прохождение через элемент И 16 на вторые входы эле- . ных выходных шинах дешифратора 15. ментов И 17 группы. Обнуленному состоя- Так осуществляется переход к опросу вто- нию счётчика каналов 14 соответствует ну- рого регистра управления, левая кодовая комбинация на его разряд-Переход к опросу очередного регистра

ных выходах, которая подается на входы управления осуществляется также в слу- дещифратора 15. Нулевой кодовой комбина- чае обнаружения единиц во всех позиции на входе дешифратора соответствует 20 ционных разрядах соответствующего регист- унитарный код на его выходах, состоящий ра управления. В этом случае на выходе из единичного уровня на выходной щине Г1 дещифратора и нулевых уровней на остальных выходных щинах. При этом разблокируется элемент И 17 группы, соединенный с щиной Г1 дещифратора 15, и тактовые импульсы поступают на первый сдвиговый вход регистра управления первого канала. Каждый тактовый импульс приводит к сдвигу разрядов в регистре управления. В результате записанные в регистр зо Р разблокировке соответствующего управления значения разрядов последова- элемента И 17 группы. При этом такто- тельно поступают с его выхода на соот- вые импульсы начинают поступать на пер- ветствующие входы элементов И 19 и 20. вый сдвиговый вход регистра управления Если при этом обнаруживается позицион- очередного канала. Так опрашиваются все ный разряд, в котором записана единица, регистры 18 управления и в каждый то на выходе элемента И 19 появляет- , канал передаются сообщения, содержащие ся импульс (на выходе элемента И 20 он заданные страницы буферной памяти.

По окончании приема информации из каналов связи в буферную память 3 так же, как и в режиме передачи, счетчик 14 каналов формирует импульс на выходе пере- 40 полнения, который поступает на нулевой вход триггера 8, устанавливает его в нулевое состояние, формируя сигнал «Готовность на нулевом пыходе этого триггера. Узел 1 отключает каналы связи от щифра- тора 2, а триггер 8 блокирует прохождение тактовых импульсов через элемент И 9. Таким образом, опрос страниц передачи.

счетчика 12 страниц канала формируется сигнал переполнения, который через элемент ИЛИ 13 поступает на вход счетчика 14 каналов, который подсчитывает этот импульс. В результате изменяется значение кодовой комбинации на разрядных выходах этого счетчика, что в свою очередь, приводит к появлению единичного уровня на очередной выходной щине дещифратоне появляется, так как наличие «1 на инверсном входе этого элемента приводит к появлению «О на его выходе). При этом в устройстве происходят следующие изменения.

Дещифратор 6 адреса подключает соответствующую страницу буферной памяти к щифратору 2. Триггер 10 устанавливается в единичное состояние, при этом прохождение тактовых импульсов через элемент И 16 для опроса очередных позиционных разрядов данного регистра управления заблокировано. Разблокируется элемент И 11, тактовые импульсы начи45

записанных в регистрах 18 управления, и выработка необходимых для этого сигналов в данном устройстве обеспечивается триггенают поступать на вход счетчика 5 и шиф- ром 10, элементом И 11, счетчиком 12 стра- ратор 2 осуществляет преобразование битов ниц каналов, элементом ИЛИ 13, счетчиком соответствующей страницы сообщения. После заверщения преобразования страницы счетчик 5 вырабатывает сигнал, который поступает на вход триггера 10 и переключает его в нулевое состояние. Поступ- 55 фиг. 3. ление импульсов на вход счетчика 5 пре-Подключение необходимых страниц букращается, через элемент И 16 импуль- ферной памяти к щифратору 2 осущест- сы поступают для опроса следующих по- вляется дешифратором 6 адреса.

14 каналов, дещифратором 15, элементами И 16, 17, 19 и 20. Описанный процесс опроса страниц передачи поясняется временными диаграммами, приведенными на

зиционных разрядов данного регистра управления.

Если в процессе сдвига информационных разрядов в ре истре управления на его выходе появляется позиционный разряд, в котором записан нуль, то на выходе элемента И 20 появляется импульс, который обнуляет счетчик 12 и через элемент ИЛИ 13 поступает на счетный вход счетчика 14 каналов. При этом на разрядных выходах

счетчика каналов фор.мируется двоичный код номера второго регистра управления, который преобразуется дещифратором 15 в ных выходных шинах дешифратора 15. Так осуществляется переход к опросу вто- рого регистра управления, Переход к опросу очередного регистра

соответствующий унитарный код, состоящий из «1 на щине 12 и «О на остальсчетчика каналов фор.мируется двоичный код номера второго регистра управления, который преобразуется дещифратором 15 в ных выходных шинах дешифратора 15. Так осуществляется переход к опросу вто- рого регистра управления, Переход к опросу очередного регистра

управления осуществляется также в слу- чае обнаружения единиц во всех позиционных разрядах соответствующего регист- ра управления. В этом случае на выходе Р разблокировке соответствующего элемента И 17 группы. При этом такто- вые импульсы начинают поступать на пер- вый сдвиговый вход регистра управления чередного канала. Так опрашиваются все регистры 18 управления и в каждый канал передаются сообщения, содержащие аданные страницы буферной памяти.

счетчика 12 страниц канала формируется сигнал переполнения, который через элемент ИЛИ 13 поступает на вход счетчика 14 каналов, который подсчитывает этот импульс. В результате изменяется значение кодовой комбинации на разрядных выходах этого счетчика, что в свою очередь, приводит к появлению единичного уровня на очередной выходной щине дещифратором 10, элементом И 11, счетчиком 12 стра- ниц каналов, элементом ИЛИ 13, счетчиком фиг. 3. Подключение необходимых страниц бу14 каналов, дещифратором 15, элементами И 16, 17, 19 и 20. Описанный процесс опроса страниц передачи поясняется временными диаграммами, приведенными на

Дешифратор адреса работает следующим образом.

Единичный импульс на выходе элемента И 19, появляющийся при опросе единичного позиционного разряда соответствующего регистра 18 управления, переключает триггер Ш в единичное состояние и подсчитывается счетчиком страниц канала. В соот- в етствии с этим на разрядных выходах этого счетчика изменяется двоичный код, увеличиваясь на единицу, что равносильно увеличению на единицу номера страницы буферной памяти. Этот код преобразуется дешифратором 29 в унитарный код на его выходе, т. е. в код с единичным уровНа временных диаграммах (фиг. 3) приведен случай, когда число каналов связи (регистров управления) .

Формула изобретения

Устройство для сопряжения вычислительной машины с каналами связи, содержащее узел коммутации, шифратор, буферную 10 память, дешифратор управления коммутацией каналов, счетчик, два триггера, дешифратор адреса, первый элемент И, причем первые информационные вход и выход узла коммутации являются входом и выходом устройства для подключения к каналам

нем на шине, соответствующей номеру стра- 15 связи, первые информационные вход и выницы буферной памяти, которую необходимо подключить к шифратору 2. Переход триггера 10 в единичное состояние приводит к разблокированию элемента И 11.

ход буферной памяти являются входом и выходом устройства для подключения соответственно к-информационным выходу и входу вычислительной машины, первый вход

Тактовые импульсы поступают через первый 20 первого элемента И является входом уствыход счетчика 5 на вход счетчика 30 длины страниц и подсчитываются этим счетчиком. Соответственно этому на выходе счетчика 30 образуется двоичный код адресов ячеек буферной памяти внутри страницы.

роиства для подключения к тактовому выходу вычислительной машины, нулевой и единичный входы первого триггера являются входами устройства для подключения к выходам записи и чтения вычислительной маРазрядность счетчика 30 равна длине стра- 25 шины соответственно, единичный вход и нуницы.

Дешифратор 4 управления коммутацией каналов управляет подключением каналов узлов 1 коммутации в режиме приема и

левой выход второго триггера являются входом и выходом устройства для подключения соответственно к выходу и входу готовности вычислительной машины, при этом нулевой выход первого триггера соепередачи. Переключение каналов происходит 0 динен с разрешающим входом дешифратора

в следующих случаях: при полном использовании всех страниц памяти канала; при определении конца передачи страниц памяти канала опросом нулевого позиционного разряда в соответствующем регистре

управления коммутацией каналов, выход которого соединен с управляющим входом узла коммутации, вторые информационные вход и выход которого соединены соответственно с первыми информационными

управления, что приводит к появлению выходом и входом шифратора, вторые ин- импульса на выходе элемента И 20.- формационные вход и выход которого соеВ первом случае формируется сигнал переполнения на выходе счетчика 12 страниц канала, который через элемент ИЛИ 13 поступает на вход счетчика 14 каналов, что приводит к формированию двоичного кода номера очередного канала на разрядных выходах этого счетчика. Этот код поступает на вход дешифратора 4 управления коммутацией каналов, который обеспечивает

динены соответственно с вторыми информационными выходом и входом буферной памяти, адресный вход которой соединен с 40 выходом дешифратора адреса, первый информационный вход которого соединен с разрешающим входом шифратора и выходом счетчика, отличающееся тем, что, с целью повышения быстродействия, в него введены счетчик страниц канала, счетчик каналов.

переключение канала в соответствии с посту- 45 третий триггер, дешифратор, четыре элемента И, элемент ИЛИ, группа регистров управления, группа элементов И, причем информационные входы регистров управления группы образуют группу входов устройства для подключения к группе адресных выходов вычислительной машины, при этом единичный выход второго триггера соединен с вторым входом первого элемента И и первыми входами второго и третьего элементов И, вторые входы которых соединены с выходапившим кодом.

Во втором случае процедура переключения канала дешифратором 4 управления коммутацией каналов происходит аналогично. Только формирование двоичного кода номера очередного канала на разрядных выходах счетчика 14 каналов происходит в результате поступления на его вход импульса с выхода элемента И 20 через элемент ИЛИ 13.

В

мента И, элемент ИЛИ, группа регистров управления, группа элементов И, причем информационные входы регистров управления группы образуют группу входов устройства для подключения к группе адресных выходов вычислительной машины, при этом единичный выход второго триггера соединен с вторым входом первого элемента И и первыми входами второго и третьего элементов И, вторые входы которых соединены с выходарежиме приема данное устройство -г ми регистров управления группы, синхроработает так же, как и в режиме передачи. Переключение узла I на прием осуществляется с помощью триггера 7.

входы которых соединены с выходами соответствующих элементов И группы, первые входы которых соединены с соответствуюНа временных диаграммах (фиг. 3) приведен случай, когда число каналов связи (регистров управления) .

Формула изобретения

Устройство для сопряжения вычислительной машины с каналами связи, содержащее узел коммутации, шифратор, буферную 10 память, дешифратор управления коммутацией каналов, счетчик, два триггера, дешифратор адреса, первый элемент И, причем первые информационные вход и выход узла коммутации являются входом и выходом устройства для подключения к каналам

15 связи, первые информационные вход и выход буферной памяти являются входом и выходом устройства для подключения соответственно к-информационным выходу и входу вычислительной машины, первый вход

первого элемента И является входом устроиства для подключения к тактовому выходу вычислительной машины, нулевой и единичный входы первого триггера являются входами устройства для подключения к выходам записи и чтения вычислительной малевой выход второго триггера являются входом и выходом устройства для подключения соответственно к выходу и входу готовности вычислительной машины, при этом нулевой выход первого триггера соединен с разрешающим входом дешифратора

управления коммутацией каналов, выход которого соединен с управляющим входом узла коммутации, вторые информационные вход и выход которого соединены соответственно с первыми информационными

выходом и входом шифратора, вторые ин- формационные вход и выход которого соединены соответственно с вторыми информационными выходом и входом буферной памяти, адресный вход которой соединен с 40 выходом дешифратора адреса, первый информационный вход которого соединен с разрешающим входом шифратора и выходом счетчика, отличающееся тем, что, с целью повышения быстродействия, в него введены счетчик страниц канала, счетчик каналов.

45 третий триггер, дешифратор, четыре эле45 третий триггер, дешифратор, четыре эле50

мента И, элемент ИЛИ, группа регистров управления, группа элементов И, причем информационные входы регистров управления группы образуют группу входов устройства для подключения к группе адресных выходов вычислительной машины, при этом единичный выход второго триггера соединен с вторым входом первого элемента И и первыми входами второго и третьего элементов И, вторые входы которых соединены с выходавходы которых соединены с выходами соответствующих элементов И группы, первые входы которых соединены с соответствующими выходами дешифратора, группа информационных входов которого соединена с группой информационных входов дешифратора управления коммутацией каналов и группой разрядных выходов счетчика каналов, счетный вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И и установочным входом счетчика страниц канала, выход которого соединен с вторым входом элемента ИЛИ, выход второго элемента И соединен со счетным входом счетчика страниц канала, вторым информационным входом дешифратора адреса и единичным входом третьего триггера, единичный выход которого соединен с первым входом четвертого элемента И, выход которого соединен со счетным входом счетчика, выход переполнения которого соединен с нулевым входом третьего триггера, нулевой выход которого соединен с первым входом ПЯТОГО- элемента И, второй вход которого соединен с выходом первого элемента И и вторым входом четвертого

элемента И, выход переполнения счетчика каналов соединен с нулевым входом второго триггера, выход пятого элемента И соеди- HtH с вторыми входами элементов И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1399746A1 |

| Устройство для сопряжения электронно-вычислительной машины с каналами связи | 1984 |

|

SU1244670A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1478222A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1439610A1 |

Изобретение относится к вычислительной технике и может быть использовано в телекоммуникационных вычислительных системах. Цель изобретения состоит в повышении быстродействия. Устройство содержит узел 1 коммутации, шифратор 2, буферную память 3, дешифратор 4 управления коммутацией каналов, дешифратор 6 адреса, счетчик 5, три триггера 7, 8, 10, дешифратор 15, счетчик 12 страниц канала, счетчик 14 каналов, пять элементов И 9, 11, 16, 19, 20, элемент ИЛИ 13, группу 18 регистров управления, группу 17 элементов И. 4 ил. с S (Л di со tSD гч:) N

а

1-й канал

2-й на нал

есть инфор нация

нет информации

Регистра 1

Рвгистр№2

(PU8.2

О

о

О

о

Регистр №з

Фиг.

ФигЛ

страницы

| Устройство для сопряжения вычислительной машины с каналами связи | 1973 |

|

SU516031A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 760075, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-01—Подача