(54) ПОРОГОВОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер с эмиттерной связью на транзисторах разного типа проводимости | 1978 |

|

SU748812A1 |

| Пороговое устройство | 1979 |

|

SU828393A1 |

| Блок для защиты стабилизированного источника питания постоянного напряжения | 1974 |

|

SU651328A1 |

| Выходной каскад усилителя с защитой от короткого замыкания нагрузки | 1979 |

|

SU923004A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2257002C2 |

| Преобразователь импульсов | 1983 |

|

SU1145433A1 |

| ДВУХКАНАЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2452078C1 |

| Операционный усилитель с защитой выхода от перегрузки | 1981 |

|

SU1020971A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Электрогидравлический регулятор подачи электроэрозионного станка | 1977 |

|

SU742094A1 |

1

Изобретение относится к области автоматики, в частности к усилительной и импульсной технике, и предназначено для усиления и выбора электрических сигналов, амплитуда которых лежит между двумя заданными уровнями.

Известно пороговое устройство, содержащее входной и выходной каскады на транзисторах противоположной проводимости, эмиттерный новторитель, резисторы, причем коллектор транзистора входного каскада соединен с базой транзистора выходного каскада и с коллектором транзистора эмиттерного повторителя.

Однако известное пороговое устройство не обеспечивает отсутствие выходного сигнала при дальнейшем увеличении входного сигнала.

С целью обеспечения отсутствия выходного сигнала при наличии входного, лежащего за двумя уровнями селекции, в предлагаемом устройстве эмиттер транзистора выходного каскада соединен непосредственно с эмиттером транзистора эмиттерного повторителя, при этом база транзистора эмиттерного повторителя и эмиттер транзистора входного каскада подключены к переменным резисторам.

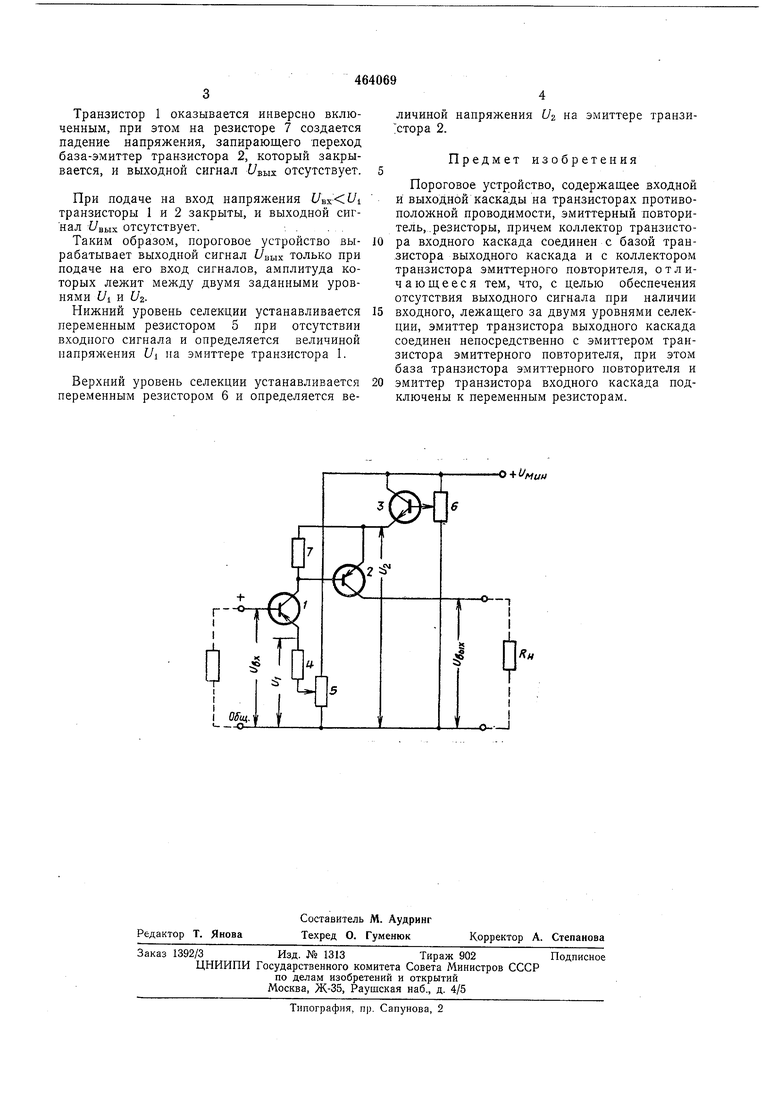

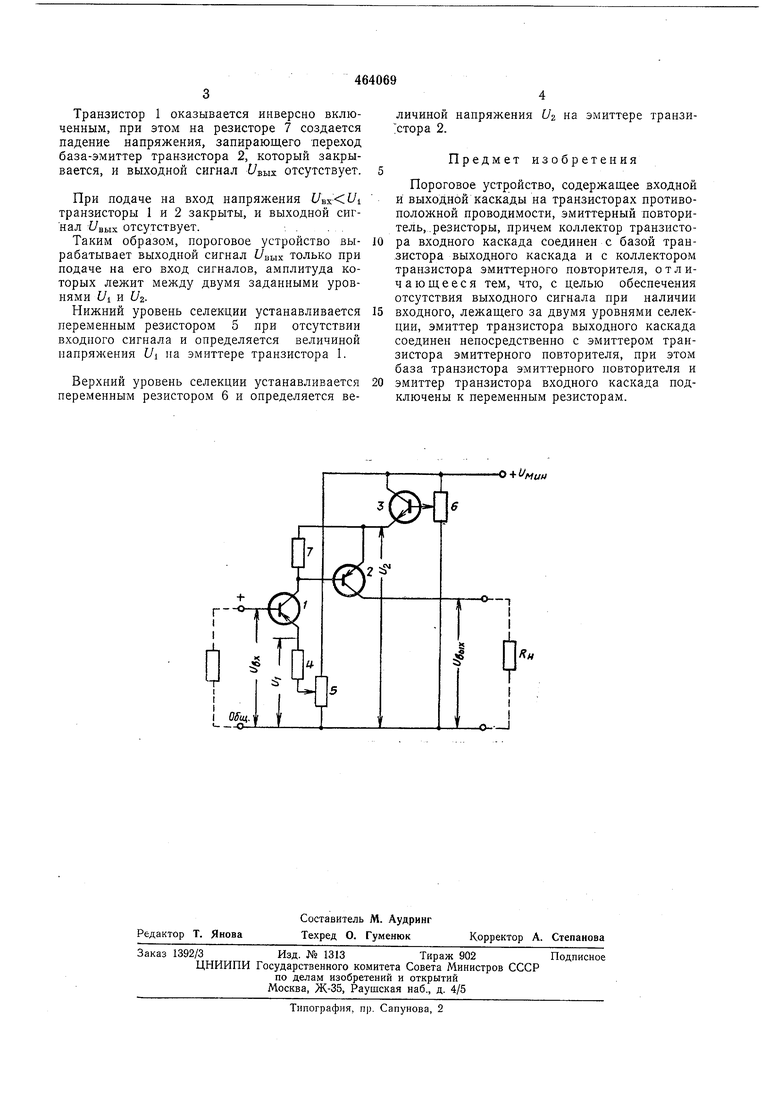

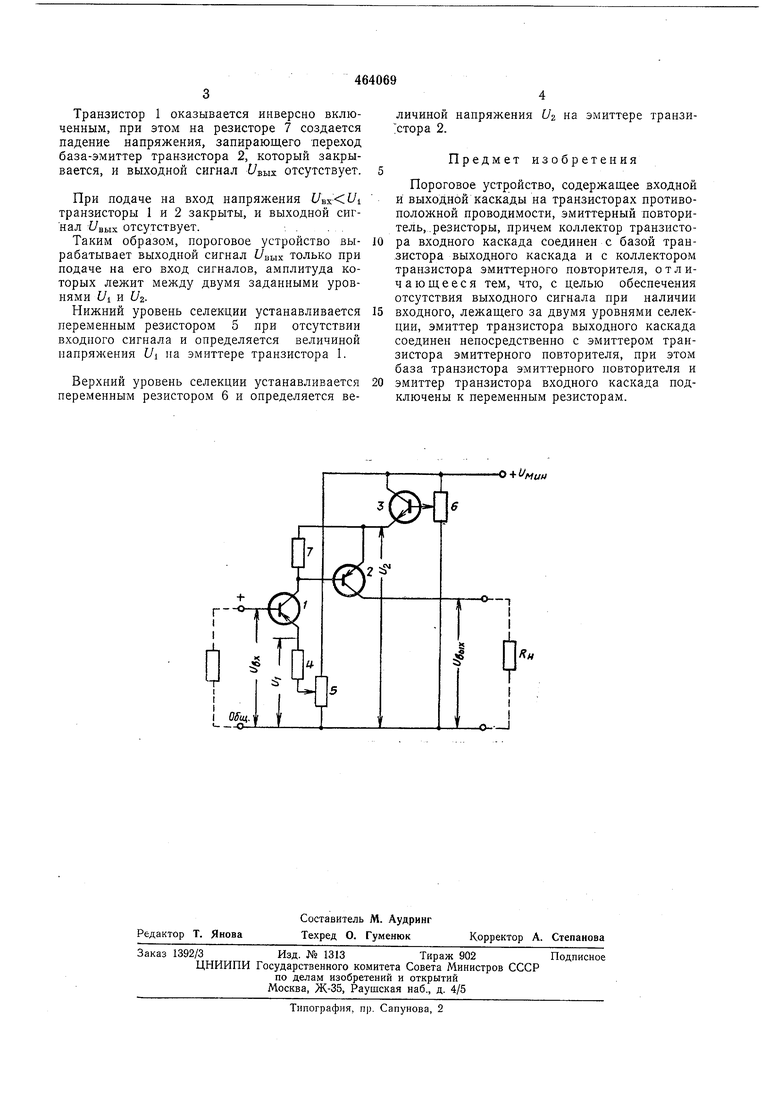

На чертеже представлена схема предлагаемого порогового устройства.

Пороговое устройство состоит из входного

и выходного каскадов, которые выполнены на транзисторах 1 и 2 противоположной проводимости по схеме с общим эмиттером.

Входной и выходной каскады на транзисторах 1 и 2 включены в качестве нагрузки эмнттерного повторителя яа транзисторе 3, причем эмиттер транзистора 1 через резистор 4 соединен с перемеппым резистором 5, а база транзистора 3 эмиттерного повторителя соединена с переменным резистором 6, в свою очередь, оба переменных резистора 5 и 6 подкотючены к источнику питания.

Резистор 7 является нагрузкой транзистора 1.

При отсутствии входного сигнала Ьвх транзисторы 1 Н 2 закрыты и получают питание с эмиттера транзистора 3, при этом выходной сигнал (Увых, снимаемый с коллектора транзистора 2, отсутствует.

При оодаче на вход напряжения (( транзистор 1 открывается и через его нагрузку проходит коллекторный ток, создающий на резисторе 7 падение напряжения, открывающее переход база-эмпттер транзистора 2. Последний открывается и с его коллектора снимается усиленный по мощности выходной сигнал (/выхПри подаче на вход напряжения напряжение f/j соответственно увеличивается и становится больше UzТранзистор 1 оказывается инверсно включенным, при этом на резисторе 7 создается падение напряжения, запирающего переход база-эмиттер транзистора 2, который закрывается, и выходной сигнал отсутствует.

При подаче на вход напряжения транзисторы 1 и 2 закрыты, и выходной сигнал 1/вых отсутствует.

Таким образом, пороговое устройство вырабатывает выходной сигнал 1/вых только при подаче на его вход сигналов, амплитуда которых лежит между двумя заданными уровнями Vi и Hz.

Нижний уровень селекции устанавливается переменным резистором 5 при отсутствии входного сигнала и определяется величиной напряжения t/i па эмиттере транзистора 1.

Верхний уровень селекции устанавливается переменным резистором 6 и определяется веI OSu4. оличиной напряжения Uz на эмиттере транзистора 2.

Предмет изобретения

Пороговое устройство, содержащее входной и выходной каскады на транзисторах противоположной проводимости, эмиттерный повторитель,, резисторы, причем коллектор транзистора входного каскада соединен с базой транзистора выходного каскада и с коллектором транзистора эмиттерного повторителя, отличающееся тем, что, с целью обеспечения отсутствия выходного сигнала при наличии

входного, лежащего за двумя уровнями селекции, эмиттер транзистора выходного каскада соединен непосредственно с эмиттером транзистора эмиттерного повторителя, при этом база транзистора эмиттерного повторителя и

эмиттер транзистора входного каскада подключены к переменным резисторам.

0 + миа

Авторы

Даты

1975-03-15—Публикация

1972-04-03—Подача