1

Изобретение относится к цифровым фазовым дискриминаторам, используемым в радиоизмерительной технике, в часности, нри измерении фазовых сдвигов сигналов фазоимпульсной модуляции (ФИМ), получаемых в результате масштабно-временных нреобразований однократных быстропротекающих процессов с помощью запоминающих электроннолучевых трубок (ЗЭЛТ).

Известен цифровой фазовый дискриминатор, содержащий два формирователя импульсов опорного и измеряемых сигналов, статические триггеры, вентили, счетчик, генератор эталонных имнульсов, регистр, регистры опорного числа и памяти, делитель эталонных импульсов схемы «И и «ИЛИ, триггер.

Иедостаток известного цифрового фазового дискриминатора заключается в появленнн неустранимых ошибок, нриводящих к искажению формы исходного нроцесса.

Целью изобретения является увеличение достоверности результата измерения.

С этой целью введены триггер со счетным входом, донолнительный статический триггер, схема «НЕ и донолнительная схема «И, причем счетный вход триггера соединен с выходом формирователя нмпульсов измеряемого сигнала, его единич}1ый выход подключен к единичному входу дополннтельного статического триггера, еднничный выход которого соединен с нервым входом дополнительной схемы «И, а нулевой выход триггера со счетным входом соединен с единичным входом триггера, нулевой выход которого соединен со вторым входом донолнительной схемы «И, выход которой нодключен ко входу схемы «НЕ и ко входу регистра, а выход схемы «НЕ соединен со входом схемы «И, при этом выход делителя эталонных импульсов соединен с нулевыми входами триггера, триггера со счетным входом и донолнительного статического триггера.

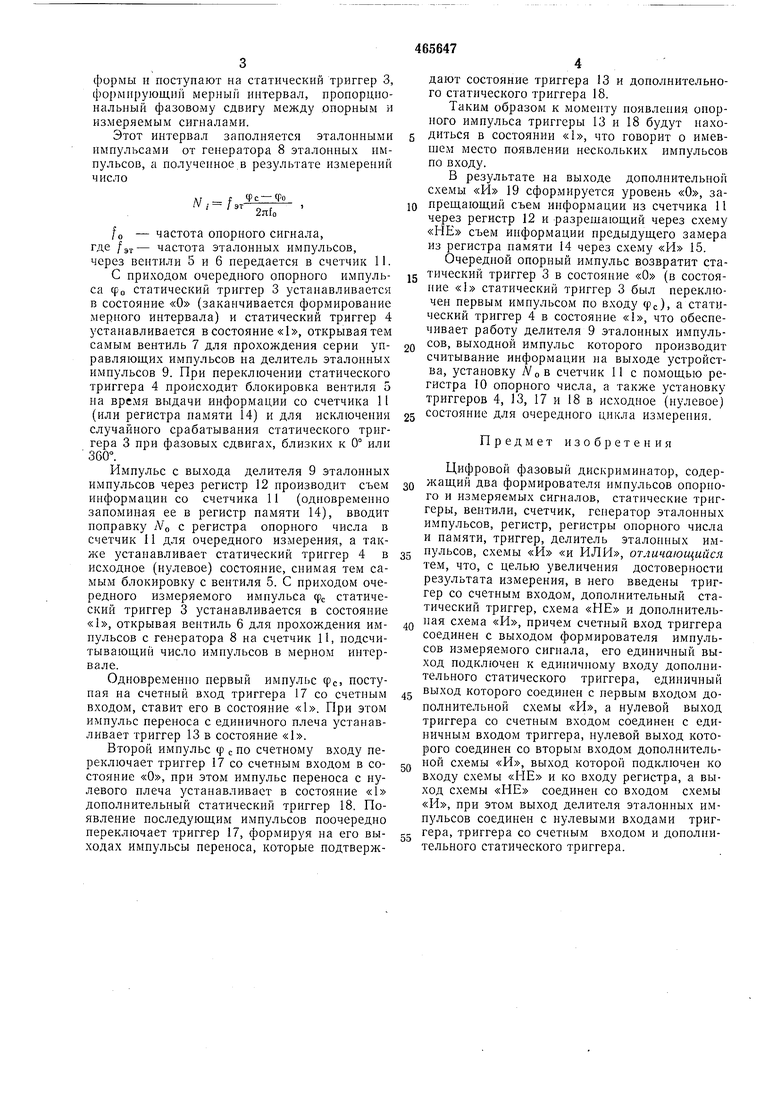

На чертеже представлена блок-схема предлагаемого дискриминатора.

Он содержит формирователь 1 импульсов измеряемого сигнала, формирователь 2 импульсов опорного сигнала, статические триггеры 3 и 4, вентили 5-7, генератор 8 эталонных импульсов, делитель 9 эталонных импульсов, регистр 10 опорного числа, счетчик 11, регистр 12, триггер 13, регистр 14 памяти, схема «И 15, схема «ИЛИ 16, триггер 17 со счетным входом, дополнительный статический триггер 18, дополнительная схема «И 19, схема «НЕ 20.

Работает цифровой фазовый дискриминатор следующим образом.

Сигналы с измеряемой срс и опорной фо фазами преобразуются в формирователях 1 и

0 2 соответственно в импульсы стандартной

формы и поступают на статический триггер 3, формирующий мерный интервал, пронорциоиальный фазовому сдвигу между опорным и измеряемым сигналами.

Этот интервал занолияется эталонными импульсами от генератора 8 эталонных нмпульсов, а полученное в результате измерений число

/V, /,,-

2nfo

/о - частота опорного сигнала, где /эт- частота эталониых импульсов, через вентили 5 и 6 передается в счетчик 11.

С приходом очередного опорного импульса фо статический триггер 3 устанавливается в состояние «О (заканчивается формирование мерного интервала) и статический триггер 4 устанавливается в состояние «1, открывая тем самым вентиль 7 для прохождения серии управляющих импульсов на делитель эталоиных импульсов 9. При переключении статического триггера 4 происходит блокировка вентиля 5 на время выдачи информации со счетчика 11 (или регистра памяти 14) и для исключения случайного срабатывания статического триггера 3 при фазовых сдвигах, близких к 0° или 360°.

Импульс с выхода делителя 9 эталонных импульсов через регистр 12 производит съем информации со счетчика 11 (одновременно запоминая ее в регистр памяти 14), вводит поправку NO с регистра опорпого числа в счетчик 11 для очередного измерения, а также устанавливает статический триггер 4 в исходное (нулевое) состояние, снимая тем самым блокировку с вентиля 5. С приходом очередного измеряемого имнульса фс статический триггер 3 устанавливается в состояние «1, открывая вентиль 6 для прохождепия импульсов с генератора 8 на счетчик И, подсчитывающий число импульсов в мерном интервале.

Одновременно первый импульс фс, поступая па счетпый вход триггера 17 со счетным входом, ставит его в состояние «1. При этом импульс переноса с единичного плеча устанавливает триггер 13 в состояние «1.

Второй импульс ф с по счетному входу переключает триггер 17 со счетным входом в состояние «О, при этом импульс переноса с нулевого плеча устанавливает в состояние «1 дополнительный статический триггер 18. Появление последующим импульсов поочередно переключает триггер 17, формируя на его выходах импульсы переноса, которые подтверждают состояние триггера 13 и дополнительного статического триггера 18.

Таким образом к моменту появления опорного импульса триггеры 13 и 18 будут находиться в состоянии «1, что говорит о имевшем место появлении нескольких импульсов по входу.

В результате на выходе дополнительной схемы «И 19 сформируется уровень «О, за0 прещающий съем информации из счетчика 11

через регистр 12 и разрешающий через схему

«НЕ съем информации предыдущего замера

из регистра памяти 14 через схему «И 15.

Очередной опорный импульс возвратит статический триггер 3 в состояние «О (в состояние «1 статический триггер 3 был переключен первым импульсом по входу Фс), а статический триггер 4 в состояние «1, что обеспечивает работу делителя 9 эталонных импульQ сов, выходной импульс которого производит считывание информации на выходе устройства, установку счетчик И с помощью регистра 10 опорного числа, а также установку триггеров 4, 13, 17 и 18 в исходное (иулевое)

5 состояние для очередного цикла измерения.

Предмет изобретения

Цифровой фазовый дискриминатор, содерQ жащий два формирователя импульсов опорного и измеряемых сигналов, статические триггеры, вентили, счетчик, генератор эталонных импульсов, регистр, регистры опорного числа и памяти, триггер, делитель эталонных импульсов, схемы «И «и ИЛИ, отличающийся тем, что, с целью увеличения достоверности результата измерения, в него введены триггер со счетным входом, дополнительный статический триггер, схема «НЕ и дополнительд пая схема «И, причем счетный вход триггера соединен с выходом формирователя импульсов измеряемого сигнала, его единичный выход подключен к единичному входу дополпительного статического триггера, единичный

g выход которого соединен с первым входо.м дополнительной схемы «И, а нулевой выход триггера со счетным входом соединен с единичным входом триггера, нулевой выход которого соединен со вторым входом дополнительо ной схемы «И, выход которой подключен ко входу схемы «НЕ и ко входу регистра, а выход схемы «НЕ соединен со входом схемы «И, при этом выход делителя эталонных импульсов соединен с нулевыми входами триггера, триггера со счетным входом и дополнительного статического триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый дискриминатор | 1979 |

|

SU801027A1 |

| ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР | 1973 |

|

SU375670A1 |

| ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР | 1972 |

|

SU349007A1 |

| Цифровой фазовый дискриминатор | 1979 |

|

SU809485A1 |

| Цифровой фазовый дискриминатор | 1975 |

|

SU602881A1 |

| Цифровой фазовый дискриминатор | 1980 |

|

SU924737A2 |

| Цифровая динамическая следящая система | 1980 |

|

SU924667A2 |

| Цифровой фазовый дискриминатор | 1976 |

|

SU571769A2 |

| Цифровой фазометр мгновенных значений | 1985 |

|

SU1320770A1 |

| Устройство для измерения частоты | 1979 |

|

SU813291A1 |

Авторы

Даты

1975-03-30—Публикация

1973-08-14—Подача