1

Изобретение относится к области вычислительной техники и может использоваться при селективной обработке данных, представленных как в цифровой, так и в аналоговой форме, а также при статистической обработке данных, в измерительных системах для изменения или компенсации частотных свойств системы.

Известно устройство, состоящее из блоков памяти, содержащих схемы выборки, преобразователей «аналог-код и «код-аналог, блоков вероятностного округления, блоков матричного умножения, сумматоров, блока динамической памяти и блока управления.

В основу работы известного устройства положены аналоговые способы выполнения арифметических операций, в результате чего резко сужается частотный диапазон обрабатываемых сигналов.

Цель изобретения - увеличение быстродействия и диапазона частот входного сигнала.

Это достигается тем, что в предлагаемом аналого-цифровом фильтре сигнал поступает через преобразователь «аналог-код или непосредственно на один из входов первого сумматора, другой вход которого подключен к выходу первого блока матричного умножения, одним из входов через первый блок вероятностного округления соединенного с блоком памяти, другим через второй блок вероятиостного округления - с выходом блока динамической памяти, а непосредственно - с одним из входов второго блока матричного умножения, другие входы которого через третий блок вероятностного округления соединены с выходом блока памяти и непосредственно с выходом первого сумматора, который подключен к входу блока динамической памяти, при этом выход второго блока матричного умножения соединен с преобразователем «код- аналог через второй сумматор.

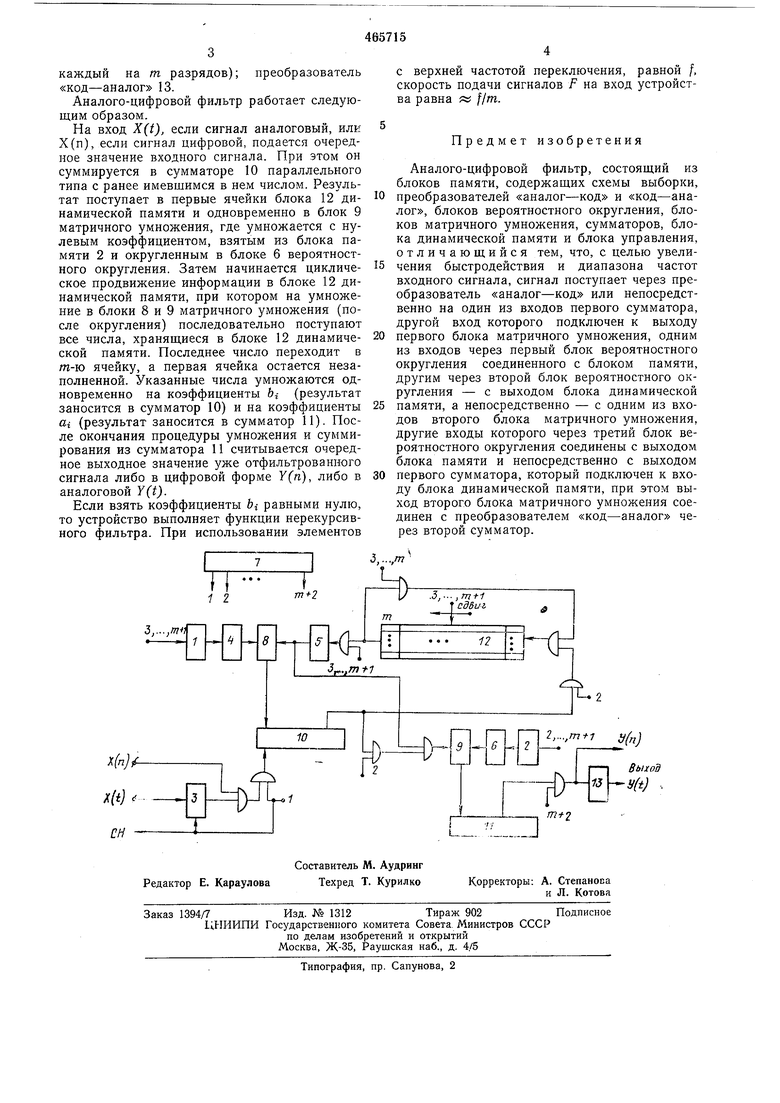

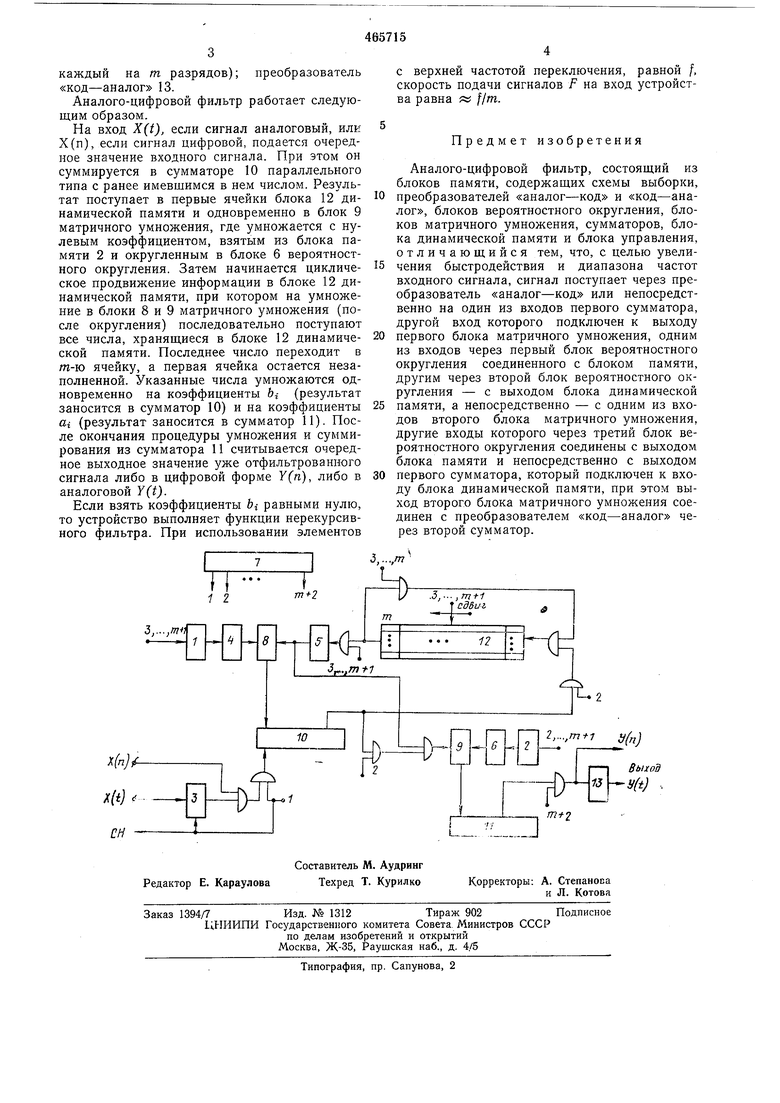

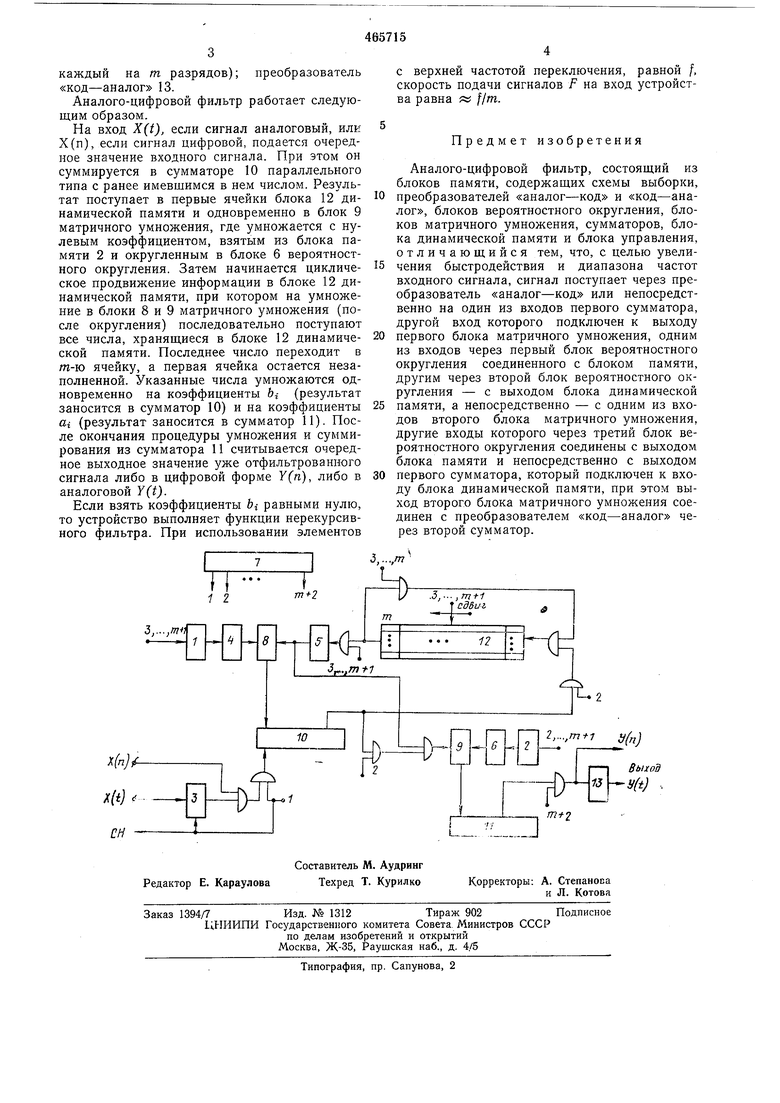

На чертеже представлена функциональная схема предлагаемого аналого-цифрового фильтра.

Схема содержит блоки памяти 1 и 2 со схемой выборки для хранения и выдачи значений коэффициентов фильтра о,; и Ь,-; преобразователь «аналог-код 3; блоки 4, 5 и 6 вероятностного округления -разрядных чисел до /-разрядных; блок управления 7, который представляет собой генератор тактовых импульсов и распределитель импульсов на /п-|-2 выходов (т - параметр фильтра); блоки 8 и 9 матричного умножения двух /-разрядных (матричный дещифратор-щифратор двух /-разрядных чисел в одно 2/-разрядное); сумматоры 10 и 11 параллельного типа на га-разрядов (п 21 S; счет результата осуществляется со старщих k разрядов); блок 12 динамической памяти (k сдвиговых регистров.

каждый на т разрядов); преобразователь «код-аналог 13.

Аналого-цифровой фильтр работает следующим образом.

На вход X(t), если сигнал аналоговый, или Х(п), если сигнал цифровой, подается очередное значение входного сигнала. При этом он суммируется в сумматоре 10 параллельного типа с ранее имевшимся в нем числом. Результат поступает в первые ячейки блока 12 динамической памяти и одновременно в блок 9 матричного умножения, где умножается с нулевым коэффициентом, взятым из блока памяти 2 и округленным в блоке 6 вероятностного округления. Затем начинается циклическое продвижение информации в блоке 12 динамической памяти, при котором на умножение в блоки 8 и 9 матричного умножения (после округления) последовательно поступают все числа, хранящиеся в блоке 12 динамической памяти. Последнее число переходит в /п-ю ячейку, а первая ячейка остается незаполненной. Указанные числа умножаются одновременно на коэффициенты Ь,- (результат заносится в сумматор 10) и на коэффициенты иг (результат заносится в сумматор 11). После окончания процедуры умножения и суммирования из сумматора И считывается очередное выходное значение уже отфильтрованного сигнала либо в цифровой форме У(п), либо в аналоговой (t).

Если взять коэффициенты Ь, равными нулю, то устройство выполняет функции нерекурсивного фильтра. При использовании элементов

с верхней частотой переключения, равной f, скорость подачи сигналов F на вход устройства равна « f/m.

Предмет изобретения

Аналого-цифровой фильтр, состоящий из блоков памяти, содержащих схемы выборки,

преобразователей «аналог-код и «код-аналог, блоков вероятностного округления, блоков матричного умножения, сумматоров, блока динамической памяти и блока управления, отличающийся тем, что, с целью увеличения быстродействия и диапазона частот входного сигнала, сигнал поступает через преобразователь «аналог-код или непосредственно на один из входов первого сумматора, другой вход которого подключен к выходу

первого блока матричного умножения, одним из входов через первый блок вероятностного округления соединенного с блоком памяти, другим через второй блок вероятностного округления - с выходом блока динамической

памяти, а непосредственно - с одним из входов второго блока матричного умножения, другие входы которого через третий блок вероятностного округления соединены с выходом блока памяти и непосредственно с выходом

первого сумматора, который подключен к входу блока динамической памяти, при этом выход второго блока матричного умножения соединен с преобразователем «код-аналог через второй сумматор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой фильтр | 1977 |

|

SU714408A1 |

| Аналого-цифровой фильтр | 1978 |

|

SU723585A1 |

| Устройство для вычисления взвешенного временного ряда | 1976 |

|

SU636620A1 |

| Аналого-цифровой фильтр | 1976 |

|

SU634286A1 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

| Устройство для определения статистических характеристик случайных процессов | 1977 |

|

SU693382A1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Цифровой фильтр | 1982 |

|

SU1109888A1 |

| Цифровой спектроанализатор | 1973 |

|

SU595739A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

Авторы

Даты

1975-03-30—Публикация

1973-01-29—Подача