BXG ф /1ьтр1

Синхр

и

W

С

CJ

ч

в/ зл

.1//

Тт

vr Vf

С

ТТТГ

ВКЗПмР

Т

CZ

c о с

44 00

О

8

W

Выход (

Т

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Цифровой фильтр | 1983 |

|

SU1146798A1 |

Изобретение относится к радиотехнике, в частности к цифровой фильтрации, и может использоваться при обработке сигналов для подавления периодических помех. Цель изобретения - повышение избирательности путем увеличения степени подавления высших гармоник и увеличение динамического диапазона за счет уменьшения уровня собственных шумов. В цифровой режекторный фильтр, содержащий аналого-цифровой преобразователь (АЦП) 1, входной регистр 2, первый сумматор 4, регистр суммы 5, блок памяти 6, регистр памяти 7, выходной регистр 9, цифроаналоговый преобразователь (ЦАП) 10 и блок управления 11, введены мультиплексор 3 и второй сумматор 8. На блоках с 3-го по 7-й реализован фильтр "текущего среднего", который включен в цепь прямой связи устройства. Операция умножения в ней заменена операцией сдвига. Входной сигнал поступает через АЦП 1 и входной регистр 2 на вход второго сумматора 8, а через мультиплексор 3-на первый сумматор 4. В фильтре "текущего среднего" за N тактов вычисляется значение "текущего среднего" входного сигнала, которое вычитается из значения входного сигнала во втором сумматоре 8. Результат фиксируется в выходном регистре 9. В устройстве возможна регулировка полосы режекции путем изменения количества циклов вычисления "текущего среднего". 3 ил.

Фиг. /

Изобретение относится к радиотехнике, в частности к цифровой фильтрации, и может использоваться при обработке сигналов для режекции периодических помех.

Цель изобретения - повышение избирательности путем увеличения степени подавления высших гармоник и увеличения динамического диапазона за счет уменьшения собственных шумов.

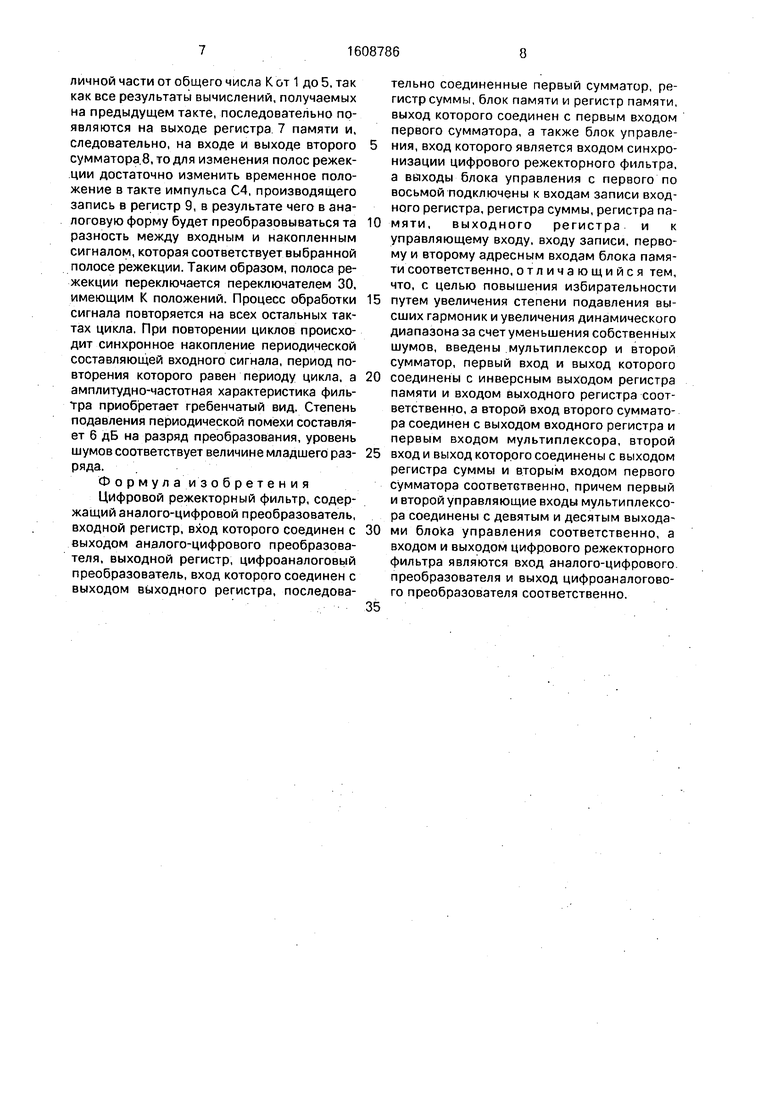

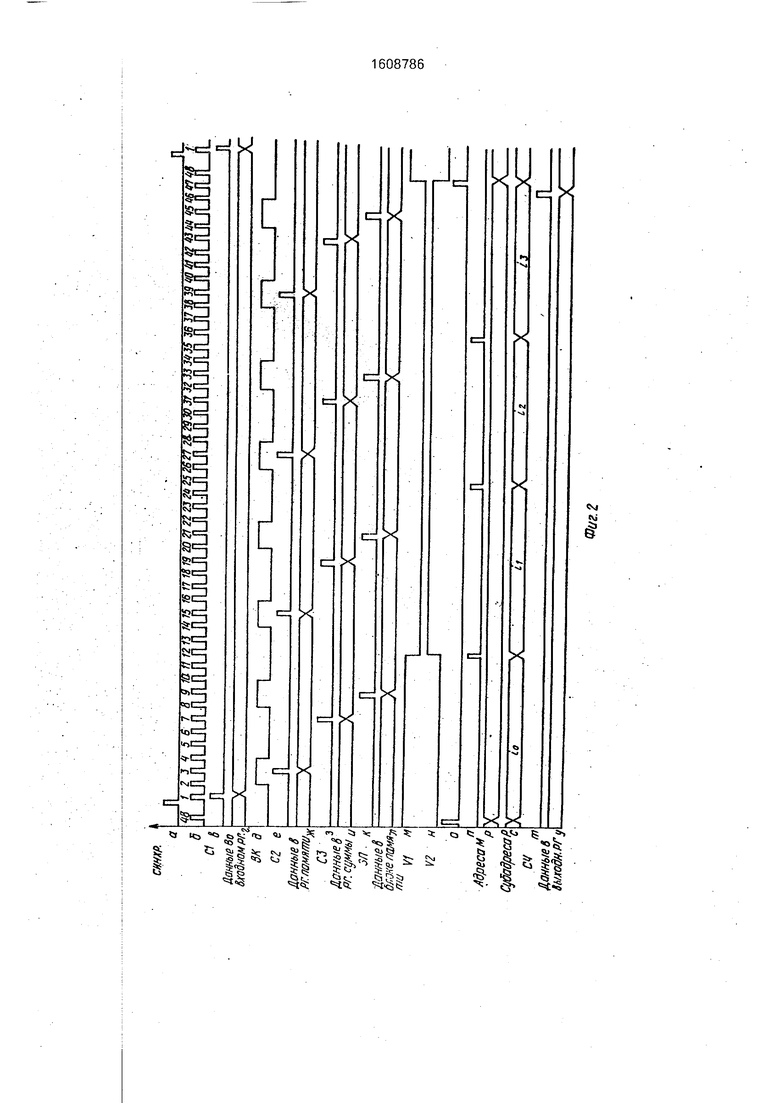

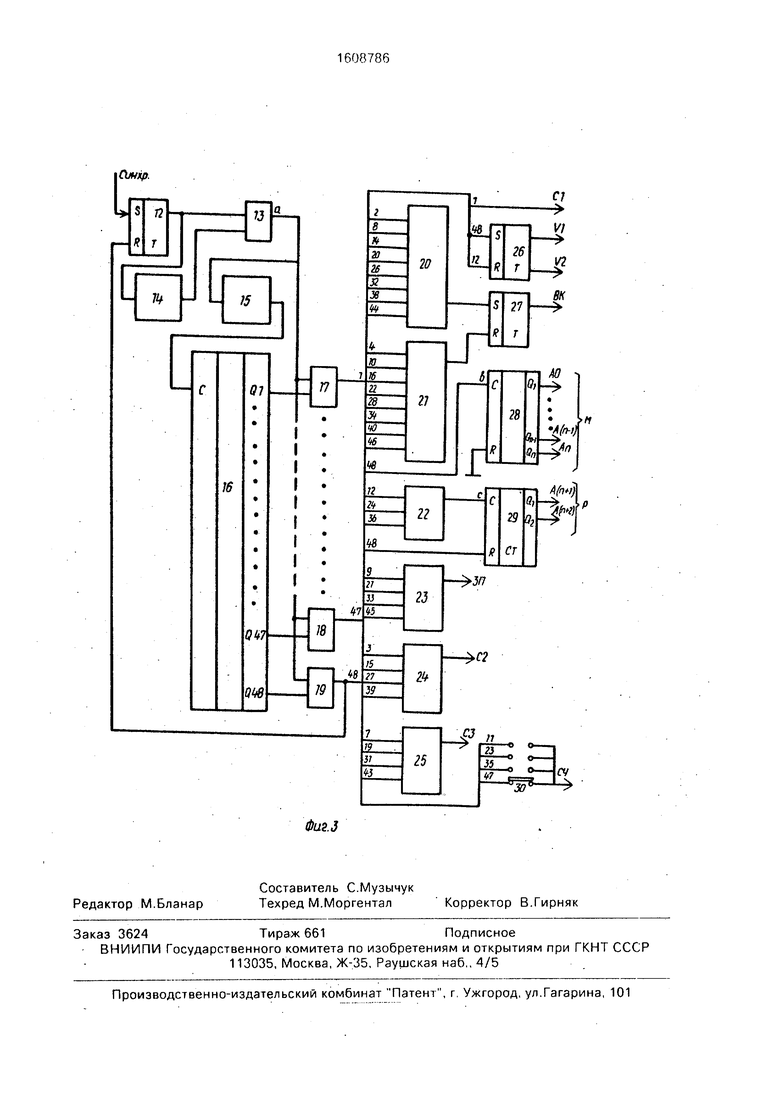

На фиг. 1 приведена структурная электрическая схема цифрового режекторного фильтра; на фиг. 2 - временные диаграммы, поясняюш1ие его работу; на фиг. 3 - структурная электрическая схема блока управления.

Цифровой режекторный фильтр содержит аналого-цифровой преобразователь (АЦП) 1, входной регистр 2, мультиплексор 3, первый сумматор 4, регистр 5 суммы, блок 6 памяти, регистр 7 памяти, второй сумматор 8i выходной регистр 9, цифроаналого- вый преобразователь (ЦАП) 10 и блок It управления.

Блок 11 управления содержит первый триггер 12, элемент И 13, генератор 14, элемент 15 задержки, кольцевой сдвигающий регистр 16, элементы И 17-19, элементы ИЛИ 20-25, второй 26 и третий 27 триггеры, первый 28 и второй 29 счетчики и переключатель 30 полосы режекции.

Цифровой режекторный фильтр работает следующим образом.

В предлагаемом фильтре осуществляется замена интегрирующего типа цифрового фильтра принципиально иным, использующим операцию вычисления текущего среднего, аналогичным инерционному типу.

Текущее среднее - среднее арифметическое между текущим значением функции и предшествующим, т.е. отстоящим во времени на постоянный период времени; Применительно к сигналам, дискретизированным по времени, операция вычисления текущего среднего может быть выражена разностным уравнением;

( + )-0-5, где х(п) - текущее значение выборки;

- усредненное на предыдущем цикле значение выборки;

N - число выборок в цикле усреднения.

Фильтр с использованием операции вычисления текущего среднего имеет передаточную функцию

1 V-N

Н (Z)

. 1-b-Z- где b - коэффициент сглаживания равен 0,5.

Существенным достоинством такого фильтра является то, что операция умножения на коэффициент сглаживания b 0,5 сводится к простому сдвигу кода результата суммирования вправо на один разряд, что не требует расширения арифметического

5 устройства и сокращает время обработки выборки. Недостатком является то, что полоса режекции при b 0,5 становится довольно широкой. Уменьшение полосы режекции достигается с помощью повторе0 ния операции вычисления текущего среднего. Использование фильтра текущего среднего не в цепи обратной связи уменьшает уровень собственных шумов до уровня младшего разряда и исключает влияние из5 менения амплитуд и сдвигов фаз высших гармоник подаваемого сигнала, вносимых фильтром нижних частот при перестройке фильтра.

0 Цифровой режекторный фильтр предназначен для подавления периодических, содержащих ряд гармоник, помех. Поэтому он действует циклически. Время цикла Тц должно поддерживаться равным периоду

5 следования помехи. Цикл складывается из повторяющихся тактов (То). Число тактов в цикле определяется числом гармоник, подлежащих подавлению в полосе частот обработки сигнала, В синхронном режиме

0 работы должно выполняться соотношение Тц N То, где N - число отсчетов АЦП 1 (выборок), приходящихся на период следования подавляемого сигнала.

Предварительная установка цифрового

5 режекторного фильтра в исходное состояние не требуется.

За время такта производится последовательно преобразование выборки сигнала с помощью АЦП 1 в К-разрядный двоичный

0 код, вычисление операц л текущего среднего, состоящей из операции считывания из блока 6 памяти, суммирования содержимого ячейки памяти с кодом выборки в сумматоре 4, записи полученной суммь обратно в

5 ту же ячейку блока 6 памяти, вычитания полученного результата из кода выборки сигнала, выполняемого сумматором 8, и об- - ратное преобразование кода результата в аналоговую форму с помощью ЦАП 10,

0На вход блока 11 управления подаются

синхроимпульсы, период следования которых равен То -.

На любом из N тактов импульс синхро- 5 низации поступает на вход S-триггера 12 и устанавливает его а состояние 1. При этом подается разрешающий потенциал на первый вход элемента И 13 и запускается генератор 14. На второй вход элемента И 13

поступают импульсы с генератора 14. Через эле1/1ент 15 задержки импульсная последовательность поступает на вход регистра 16. В исходном состоянии на выходе его первого разряда 01 - разрешающий потенциал 1, поступающий на первый вход элемента И 1, а в остальных разрядах потенциал О. На второй вход элемента И 17 поступает пер зый импульс (фиг. 2 а, б), который проходит на выход элемента И 17 и используется в Ксчестве импульса С1 для записи информации в регистр 2. Импульс, поступающий на ((ХОД регистра 16, устанавливает О на вых)деО1 и 1 на выходе Q2. Таким образом только на одном из сорока восьми выход }в Q1-Q48 регистра 16 присутствует пот1}нциал, соответствующий логической 1. На выходе элемента И 18 появляется сорок седьмой импульс, на выходе элемента И 1$ - сорок восьмой.

Импульсы с выходов элементов И 17-19 шдовательно поступают на соответству- входы элементов ИЛИ 20-25, на уста- входы триггера 26, на контакты 30 полосы режекции и слу- для формирования сигналов управле- работой цифрового режекторного зтра в соответствии с временной диаг- иой (фиг. 1) 1-я в цикле выборка входного преобразованная в двоичный па- ельный код на предыдущем такте при из блока 11 управления им- С1 (фиг. 2в), записывается в регистр 1 / ультиплексор 3, выполненный на логи- элементах 2И-ИЛИ, пропускает за- нный в регистре 2 код на второй вход 4. Этот же код поступает на зто- вход сумматора 8.

нетчик 29 устанавливает i-й адрес яче- юка 6 памяти. Число разрядов счетчика logaN. Счетчик 29, имеющий Р разря- где Р 1од2К, К -- количество операций 1сления текущего среднего, на такт, по предыдущего такта устанавлива- в нулевое состояние. При поступлении В К (фиг. 2д) в соответствии с вре- диаграммой на блок 6 памяти про- считывание из io ячейки памяти записанного на предыдущем цикле, появлении импульса С2 (фиг. 2г) проис- запись этого кода в регистр 7 памяти, хода регистра 7 памяти код поступает эрвый вход сумматора 4. После завершения операции сложения результат со сдвигом на один (полусумма) по сигналу СЗ (фиг. 2з) сывается в регистр 5 суммы. По сигна- ВК и ЗП (фиг. 2д и к), поступающим на 6 памяти из блока 11 управления, ре- ат из регистра 5 суммы записывается

пос

ющ1|1е

новочные

переключателя

жат

ния

фил

рам1

сигйала

рал/

поступлении

пулцса

ческ|их

ПИСс

сумматора рой

ек 6j 28 IV дов,

ВЬГЧ1

окончании

ется

сигнала

менной

исхсдит

кода

При

С вы на П1

полученный

разряд

за пи

лам

блок

зуль

в ту же 1о ячейку блока 6 памяти. Затем на счетный вход счетчика 29 поступает импульс, устанавливающий следующий субадрес ячеек памяти li. По сигналам VI и V2 5 (фиг. 2м и н), приходящим с выходов триггера 26, мультиплексор 3 переключает второй вход сумматора .4 к выходу регистра 5 суммы (фиг. 2и).

Повторение операции текущего средне- 10- го происходит следующим образом. Сигнал В К (фиг. 2д) поступает на блок 6 памяти, происходит считывание из ii ячейки кода, записанного также на предыдущем цикле. При появлении импульса (фиг. 2ё) С2 на ре- 15 гистре 7 памяти происходит запись этого кода в регистр 7 памяти (фиг. 2ж). Выход регистра 7 памяти подключен к первому входу первого сумматора 4, на выходе которого устанавливается результат сложения 20 содержимого ячейки ii, записанного на предыдущем цикле, и содержимого регистра 5 суммы, записанного в ячейку io и являющегося результатом предыдущего сложения. При поступлении импульса СЗ 5 (фиг. 2з) происходит запись полученного результата со сдвигом кода на один разряд вправо в регистр 5 суммы. Затем по сигналам ВК и ЗП (фиг. 2д и к) результат из регистра 5 суммы записыается в ячейку ii блока 0 6 памяти. При поступлении импульса на вход счетчика 29 происходит смена субадреса ячейки памяти, и вся последовательность операций повторяется до записи в ячейку с адресом ia. Такой повтор происходит до тех 5 пор пока счетчик 29 не переберет все К субадресов и кольцевой сдвигающий регистр 16 не вернется в выходное состояние (фиг. 2о, п, р, с).

На второй вход сумматора 8 поступает 0 значение выборки сигнала в параллельном двоичном коде, хранящееся во входном регистре 2 в течение такта.

На первый вход сумматора 8 (фиг. 2о, п, р, с) поступает содержимое регистра 7 памя- 5 ти (фиг. 2л) в обратном коде для обеспечения операции вычитания в дополнительном коде.

Код разности поступает с выхода сумматора 8 по импульсу С4 (фиг. 2т), поступающе- 0 му из блока 11 управления, один раз за период на регистр 9, фиксируется в регистре 9 (фиг. 2у). С выхода этого регистра код разности поступает на вход ЦАП 10, на выходе которого восстанавливается дискрет- 5 но-аналоговая форма сигнала.

Ширина полос режекции цифрового гребенчатого фильтра определяется величиной Тц 2 , где К - число вычислений текущего среднего за один такт. Изменение полосы режекции достигается использованием различной части от общего числа К от 1 до 5, так как все результаты вычислений, получаемых на предыдущем такте, последовательно появляются на выходе регистра. 7 памяти и, следовательно, на входе и выходе второго сумматора.8, то для изменения полос режек- ции достаточно изменить временное положение в такте импульса С4, производящего запись в регистр 9, в результате чего в аналоговую форму будет преобразовываться та разность между входным и накопленным сигналом, которая соответствует выбранной полосе режекции. Таким образом, полоса ре- жекции переключается переключателем 30. имеющим К положений. Процесс обработки сигнала повторяется на всех остальных тактах цикла. При повторении циклов происходит синхронное накопление периодической составляющей входного сигнала, период повторения которого равен периоду цикла, а амплитудно-частотная характеристика фильтра приобретает гребенчатый вид. Степень подавления периодической помехи составляет 6 дБ на разряд преобразования, уровень шумов соответствует величине младшего разряда. .

Ф о р м у л а и 3 о б р е т 6 н и я Цифровой режекторный фильтр, содержащий аналого-цифровой преобразователь, входной регистр, вход которого соединен с выходом аналого-цифрового преобразователя, выходной регистр, цифроаналоговый преобразователь, вход которого соединен с выходом выходного регистра, последовательно соединенные первый сумматор, регистр суммы, блок памяти и регистр памяти, выход которого соединен с первым входом первого сумматора, а также блок управления, вход которого является входом синхронизации цифрового режекторного фильтра, а выходы блока управления с первого по восьмой подключены к входам записи входного регистра, регистра суммы, регистра памяти. выходного регистра и к управляющему входу, входу записи, первому и второму адресным входам блока памяти соответственно, отличающийся тем, что, с целью повышения избирательности

путем увеличения степени подавления высших гармоник и увеличения динамического диапазона за счет уменьшения собственных шумов, введены мультиплексор и второй сумматор, первый вход и выход которого

соединены с инверсным выходом регистра памяти и входом выходного регистра соответственно, а второй вход второго сумматора соединен с выходом входного регистра и первым входом мультиплексора, второй

вход и выход которого соединены с выходом регистра суммы и вторым входом первого сумматора соответатвенно, причем первый и второй управляющие входы мультиплексора соединены с девятым и десятым выходами блока управления соответственно, а входом и выходом цифрового режекторного фильтра являются вход аналого-цифрового, преобразователя и выход цифроаналогово- го преобразователя соответственно.

V P; :

.

li

18 III

«41

Ixx M

о t: Ч -VJ 5 .

Й o

§ i li

I t I

:§ § 5 - § «

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-11-23—Публикация

1988-12-26—Подача