(54) АДАПТИВНЫЙ АНАЛЙГО-ЦИФРОВОЙ ФИЛЬТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1986 |

|

SU1365107A1 |

| Устройство для стабилизации средней частоты шумовых выбросов над пороговым уровнем | 1980 |

|

SU902269A1 |

| Система передачи данных | 1986 |

|

SU1462507A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Цифровой коррелометр | 1985 |

|

SU1298767A1 |

| Устройство для измерения отношения сигнала к помехе в телевизионном канале | 1985 |

|

SU1292206A1 |

| Устройство для детектирования частотно-модулированного сигнала | 1985 |

|

SU1261080A1 |

| Цифровой фильтр | 1987 |

|

SU1478298A1 |

| Устройство управления углом опережения зажигания двигателя внутреннего сгорания | 1984 |

|

SU1226482A1 |

| Спектральный анализатор | 1987 |

|

SU1613969A1 |

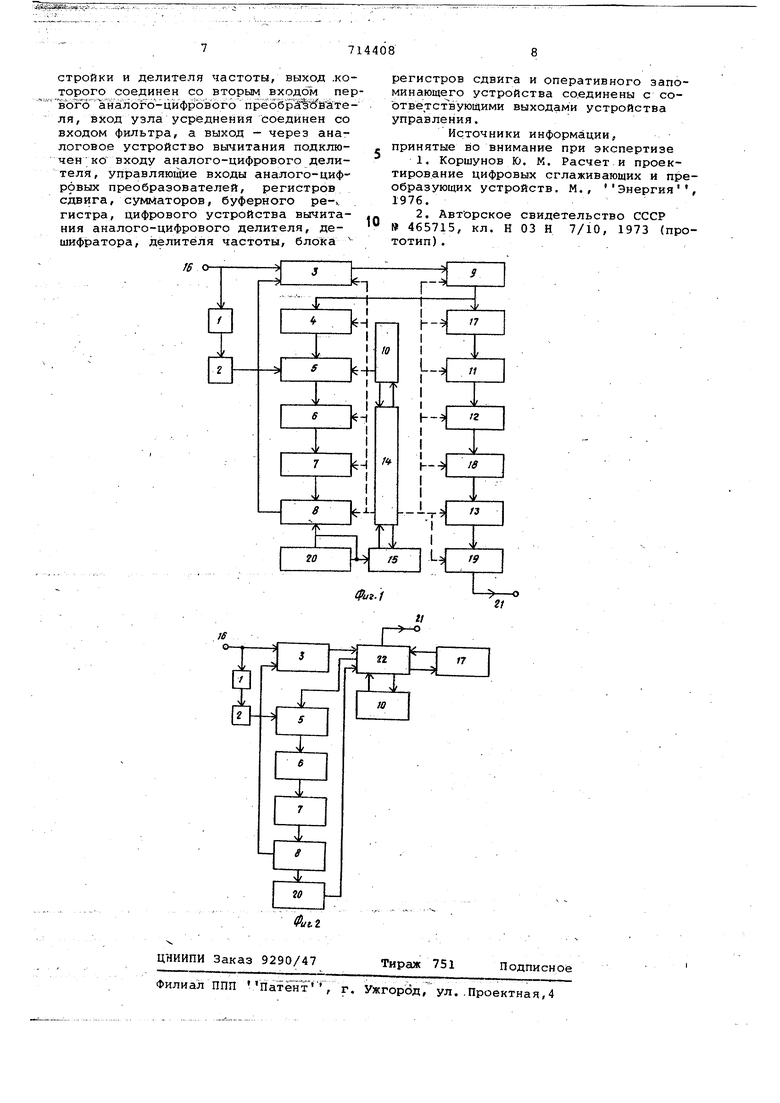

Изобретение относится к вычислительной технике и может быть использовано для выделения сигнала на фоне шумов в условиях ограниченного временч усреднения (или с;уществования сигНсша) информационно-измерительных си .стемах,в блоках сопряжения датчиков с ЭВМ, в телеметрии, в системах обработки медико-биологической информации, в задачах обработки радиолокационных сигналов, регистраторах кратковременно существующих процессов, в системах автоматического регулирования, Известны устройств:а фильтрации ста ционарных и нестационарных сигналов, содержащие аналого-цифровые преобразователи, запоминакицие и вычислительные устройства, блоки адаптации, которые устанавливают автоматиче1ски по. рядок астатизма на основе анализа входного сигнала либо меняют объем памяти по анализу входного сигнала и шума 1 . Недостатком устройства является тй что при адаптации по принципу изменения порядка астатизма фильтр имеет большие затраты оборудования,а при ав томатической оптимизации объема памяти требуется проведение предвариLельного подбора оптимальных условий регулирования объема памяти, что значительно снижает оперативность схемы в работе, Наиболее близким по технической сущности к данному является фильтр, состоящий из блбков памяти, содержащих схемы выборки, преобразователей аналог-код и код-аналог, блоков вероятностного округления, блоков матричного умножения, сумматоров, блока динамической памяти и блока управления; входной сигнал поступает . через преобразователь аналог-код или непосредственно на один из входов первого сумматора, второй вход которого подключен к выходу первого блока матричного умножения, одним из входов через первый блок вероятностного округления соединенного с блоком памяти, другим входом через второй блок вероятностного округления - с выходом блока динамической памяти, а непосредственно - с одним из входов второго блока матричного умножения, другие входы блоков матричного умножения через третий блок вероятностного округления соединены с выходом блока памяти и непосредственно с выходом первого cyNwaTopa, ко3 71 Si-iiii:--ii... .,;-:--.; :.;..;.- - -,-;.,- ;:::::: : ::/ / торий подключен к входу блока дийамическрй памяти, выход втсэрого блока матричного умножения соединен с прербразователем код-аналог через вторЪй сумматор 2. НеДбСТЖтКЬм Данного фильтра явля-. ётся узкое функциональное назначение, ,Т::Вй зайнЬе с п{)именимостью датя фильтрации стационарных сигналов и невозТможность его; использования в условиях фильтраций нестациона рнйх сигналов или кратковременно существующих сигналов. Целью изобретения является расши рение функциональных возможностей Sa Счётобеспечения фильтрации нестацио/нарНЕдХ сигналов и кратковременно су- i щёствутаЩизс сигйалов, :.. Это достигается тем, что в аналого- цифровой фильтр, содержащий первый аналого-цифровой преобразователь, пер вый вход которого является входом фильтра, два сумматора, вход первого из которых соединен с выходомпервого аналого-цифройого гфеобразователя, постоянное и оперативное запоминающие устройства, генератор тактовых импульсов и устройство управления, бвёйены два регистра сдвига, регистр Программной настройки, последовательнбсоединенные цифровое устройство вычитания, аналого-цифровой делитель, второй аналого-цифровой преобразова.тель, дешифратор и делитель частоты, Узел-усреднения, аналоговое устройство вычитания, блок регистров сдвига и буферный регистр, причем входы цифрового устройства вычитания и первого регистра сдвига соединены с выходом первого сумматора, выход первого ; регистра сдвига через порледователь. Н6 сбедйнеййые опёра:тйвное запоминающеё устройство, блок регистров сдвига, буферный регистр, второй сумматор и Бторой регистр сдвира подключен к - - - .- . ..--:..-. «itot j--- -,.-.-.т:----J - «-... ВЫХОДУ фиЯьтра, устройство управления соединено двухсторонними связями с постоянным запоминающим устройствоМ и с регистром программной настрой ки, выход гёНера:тора Т а1 т6вУхимпульсов подключен ко входам регистра программной настройки й делителя. часто- А.-..-, -лг- -- I- --,- ..-:.-. 1 :: - . Ты, Выход которого соединен со вторым входом первого аналого-цифрового преобраз6ва:теля, вход узла усреднения сбедйнён со входом фйЛьТра, Гвыход аналоговое устройство вычйтания-подключен ко входу аналого-цифро. . - .. вого делителя, управяяющиё входы аналого-цифровых преобразователей, региетров сдйИга, сумматоров-, буферного . регистра, цифрового устройства вычитания, аналого-цифрового делителя, дешифратора, делителя частоты, блока perMcfpttS ШсВйгЙ и бШратйвн6го запоминающего устройства соединены,с соотвёТствующймй вых;одами устройства управления 1 . - .- - - , На фиг. 1 представлена функциональная схема фильтра; на фиг. 2 - одна из возможных модификаций схемы. Устройство содержит узел 1 усредгнения, аналоговое устройство 2.вычитания, аналого-цифровой преобразователь 3, цифровое устройство 4 вычитания, аналого-цифровой делитель 5, аналого-цифровой преобразователь 6, дешифратор 7, делите ль 8 частоты, сумматор 9, постоянное запоминающее устройство (ПЗУ) 10, оперативное запоминающее устройство (ОЗУ) 11, блок 12 регистров сдвига, сумматор 13, устройство 14 управления, регистр 15 программной настройки, вход 16 фильтра, регистр 17 сдвига,буферный регистр 18, регистр 19 сдвига,, генератор. 20 тактовых импуЛьсов, выход 21 фильтра, микропроцессор 22. Адаптивный аналого-цифровой фильтр (фиг. 1) работает в следующей последовательности . ;: Аналоговый входной сигнал U(t) усредняется RC-цепью узла 1 в течение интервала 1 и одновременно преобразуется в код в первом аналого-цифровом преобразователе 3 с подачей кода в первьтй сумматор 9 для накопления в нем кодовN, пропорциональных входному сигналу в интервале времени 2t. В устройстве 2 Формируется аналоговое значение разности u(t +r)-u(t) а в устройстве 4 дискретная величина N(t + 2tr)-N(t), которые подаются на вход аналого-цифрового делителя 5 для формирования сигнала /0(-C+-tr - 0(t)/ /N{t-f2r7-N(-t)/ Величина которого кодируется преобразователем б с малой разрядностью.(например 2+3 бита) и дешифрируется. Выходы дешифратора 7 производят выбор соответствук1щего выхода делителя 8 частоты, сигнал которого как управляющий импульс запуска .преббразования. подается на преобразователь 3. .Та КИМ образом, частота кодирования вход ного сигнала оказывается пропорциональной V(t), т. е. время снятия заI. ,-. мера адаптивно выбирается в фильтре, Поэтому в первом сумматоре 9 при одном и том же числе накоплений М (напримерМ - 8) окажутся замеры, произведенные через разные промежутки времени, характеризующие одним и тем же . / . значением V(t). .После накрпления заданного количества замеров (величина М задается кратной целой степени с условием ) с помощью регистра; 15 программной настрсэйки производится их арифметическое усреднение (деление на 2) за счет сдвига на г разрядов (где г определяется из условия М - ) на регистре 17 сдвига и передачи F (t) JrSN N(t ) в ОЗУ11, где N(t ) кодированные значения входного сигнала . Таким образом процедура повторяет ся определенное число раз. После заполнения ОЗУ происходит параллельное считывание значения F (t) в регистры блока 12. Одновременно из ПЗУ про исходит считывание констант сдвига-в устройство 14 управления по адресу, соответствующему номеру i. В ПЗУ хра нятся константы, представлянвдие собо не сами коэффициенты нестационарности, а информацию о том, на сколько разрядов необходимо сдвинуть величину F (t) в каждом из регистров блока 12 (структура каждой константы ПЗУ состоит из последовательности знаков и величин четырех коэффициентов., т.е С1, , СЗ, Ц.С4) для того, чтобы р сумматоре 13 после сложения получить величину Y (t) (t) X. ( + 2 2 + 2 -.-l+ ) пропорциональную величине F (t)/ К , где - коэффициент нест ционарности. Такая организация умножения на . коэ ффициент нестационарности |/К позволяет, сократить объем оборудо вания ПЗУ (так как хранятся не caiMH коэффициенты а величины сдвигов в {регистрах блока-12) и повысить быстро действие умножения. Для упрощения уст ройства 14 управления ОЗУ 11 цёлесо|Образнр выполнять по схеме стековой (памяти со считыванием результата че1рез буферный регистр 18 из вершины стека и записью входных значений F: (t) из регистра 17 сдвига во входной .регистр стека. После накопления значений в сумматоре 13 происходит передача суммы в регистр 1.9 сдвига для их усреднения и выдача результата. Сигнал на. выходе определяется выражением -г- R у к - -к где R, М - параметры внешней настройки и К (i) - коэффициенты нестационар ности закладываются разработчиком, Применяющим данный фильтр, а величина tj - адаптивный параметр настройки, выбираемый в самом фильтре при усреднении нестацио.нарных сигналов в процессе работы. Адаптивный аналоготцифровой фильтр) может выполняться в другом варианте реализации (фиг. 2), в котором функции составных частей обозначенных циф рами 4, 9, 11-15, 18, 19 возложены на микропроцессор 22, реализующий тот же алгоритм работы программным-путем, Этот вариант имеет, меньшие аппаратурные затраты в микроэлектронном исполнении, второй вариант реализации применим в более медленных процессах. так как переход к программной реалиг зации функции составных частей .4, 9, 11-15, 18, 19 приведет к- снижению быстродействия в 20 + 50 раз в зависимости от типа применяемого микропроцессора. В изобретении заложено четыре величины адаптации: -интервал времени усреднения t/, изменяемый автоматически адаптивно по крутизне изменения входного сигнала-величина предварительного усреднения - М; -количество накоплений в ОЗУ - R; -с; (i) , ) , Сз (г) , С. (1) , определяемые коэффициентами нестационарности К (1), где i и 1, 2,,..R, причем для стационарныз4 сигналов.. M-R, 1, а для нестационарных М 7 К, а коэффициенты С закладываются в ПЗУ 10 фильтра на основании априорных знаний о природе сигнала и шума или на основании анализа реального сигнала (или его модели) на универсальных ЭВМ, Формула изобретения Адаптивный аналого-цифровой фильтр, содержащий первый аналого-цифровой преобразователь, первый вход которого является входом фильтра, два сумматора, вход первого из которых соединен с выходом первого.аналого-цифрового преобразователя, постоянное и оперативное запоминающие устройства, гене-, ратор т.актовых импульсов и устройство управления, о т л ич ающ и и с.я тем, что, с целью расширения функциональных возможностей за счет обеспе- чения фильтрации нестационарных сигналов и кратковременно существующих сигналов, в него вёедены два регистра сдвига, регистр программной настройки, последовательно соединенные цифровое устройство вычисления, аналого-цифровой делитель, второй аналого-цифровой преобразователь, дешифра- тор и делитель частоты, узел усреднения, аналоговое устройство вычитаний, блок регистров сдвцга и буферный регистр, причем-входы цифрового устройства вычитания и первого регистра сдвига соединены с выходом первого сумматора, выход первого регистра сдвига через последовательно соёйиненные оперативное запоминающее устройство, блок регистров сдвига, буферный регистр, второй сумматор и второй регистр сдвига подключен к выходу фильтра, устройство управления соединено двухсторонними связями с постоянным запоминающим устройством и с регистром программной настройки, выход генератора тактовых, импульсов подключен ко входам регистра программной настройки и делителя частоты, выход .которого соединен со вторым входбм первютюаналогсй-цифрового прёобрйШйтеля, вход узла усреднения соединен со входом фильтра, а выход - через аналоговое устройство вычитания подключен ко входу аналого-цифрового делителя , управляющие входы аналого-цифровых преобразователей, регистров сдвига, сумматоров, буферного ре-,, . гистра, цифрового устройства вычитания аналого-цифрового делителя, дешифратора, делителя частоты, блока

регистров сдвига и оперативного запоминающе го устройства соединены с соответствующими выходами устройства управления.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР

465715, кл. Н 03 Н 7/10, 1973 (прототип) .

Авторы

Даты

1980-02-05—Публикация

1977-09-26—Подача